반도체 기초

PART 미리보기 |

출제 경향 반도체 소자 영역에서는 주로 MOSFET과 DRAM, 그리고 낸드 플래시(NAND Flash) 메모리 소자에 대한 문제가 자주 출제되고 있다. MOSFET에서는 에너지 밴드 다이어그램을 이용해 MOSFET의 동작 원리를 설명하는 설명형 문제와, 소자 미세화에 따른 단채널 효과의 개선 대책 등을 묻는 솔루션형 문제가 주를 이룬다. 최근에는 이러한 소자 미세화에 대응하여 새로운 구조 또는 물질로 변경한 신규 소자에 대한 문제가 출제되고 있다. 아직까지 메모리 영역에서의 문제는 DRAM과 낸드 플래시에 대한 것이 대부분이며, DRAM에서는 주로 기본 동작과 누설 전류, 리프레시 등의 문제를, 낸드 플래시에서는 메모리 셀의 기본 동작과 최근 이슈인 전하 포획 플래시(CTF) 및 3D 낸드/V-NAND* 셀에 대한 원리와 문제점, 그리고 이에 대한 솔루션형 문제가 자주 출제되고 있다. 매우 기본적인 내용부터 심화 내용까지 다양한 문제들이 출제되고 있으니, 각 소자에 대한 기본 개념에 충실함은 물론 최신 기술까지 두루 학습하기 바란다. * 삼성전자에서는 ‘V-NAND’를, SK하이닉스에서는 ‘3D 낸드’라는 표현을 사용하니, 헷갈리지 않도록 주의한다. 주제별 기출문제 분석 주제 1 : 반도체 기초

주제 2 : PN 접합 다이오드

주제 3 : MOSFET

주제 4 : DRAM

주제 5 : 낸드 플래시

주제 6 : 메모리 소자 기타

|

기출문제 풀이

기출문제 ❶

실리콘 반도체의 에너지 밴드 다이어그램을 설명하시오.

STEP 1 접근 전략

설명형 문제로 난이도는 중하 수준이며 출제 빈도가 높다.

원자 간 거리에 따른 전자의 에너지 밴드 생성 원리를 설명한다.

전도대(EC), 가전자대(EV), 에너지 밴드 갭(Eg)의 의미를 설명한다.

전도체, 반도체, 부도체의 정의를 밴드 갭 개념으로 보충 설명한다.

STEP 2 답안 구조화 TIP

Q 실리콘 반도체의 에너지 밴드 다이어그램?

독립된 원자 → 불연속적 에너지 준위

원자 간격 감소 → 밴드 형성(파울리 배타율)

전도대(EC), 가전자대(EV), 밴드 갭(Eg)

에너지 ↑ → 전자 이동(EV ⇒ EC)

전도체(M), 반도체(S), 부도체(I)의 밴드 갭(Eg): EgI › EgS › EgM

STEP 3 모범답안

독립된 원자 내의 불연속적인 에너지 준위는 원자 간의 간격이 가까워짐에 따라 파울리의 배타율에 의해 각각의 에너지 준위가 나뉘어 밴드를 형성하게 됩니다. 실리콘의 경우, 핵에서 가까운 1S에서 2P 까지의 에너지 준위는 원자 간 거리가 가까워져도 서로 영향을 거의 미치지 못하는 반면, 최외각의 3S와 3P의 경우는 원자 간 거리가 가까워짐에 따라 2N개의 상태와 6N개의 상태가 상위 4N, 하위 4N개로 양분됩니다. 그리고 절대 온도 0K에서 모든 전자는 하위 4N개의 상태에만 존재하게 됩니다. 이렇게 전자로 가득 차 있는 하위 에너지 대역을 가전자대, 상부의 전자가 존재하지 않는 빈 에너지 대역을 전도대라고 하고, 두 대역 사이의 전자가 점유할 수 없는 에너지 상태를 금지대라 하며 이때의 에너지 차를 에너지 밴드 갭(Eg)이라 합니다. 실리콘의 경우, 1.12eV의 Eg를 갖습니다. 또한 전도대의 가장 낮은 에너지 준위를 EC, 가전자대의 가장 높은 에너지 준위를 EV로 표기합니다. 따라서 에너지 밴드 다이어그램은 위치에 따라 EC와 EV를 표시한 도표라고 정의할 수 있습니다.

전류의 형성을 위해서는 가전자대에 있는 전자가 에너지를 받아 Eg를 뛰어넘어 전도대로 올라가 자유롭게 이동할 수 있어야 합니다. 이 이론으로 전도체, 부도체, 반도체의 개념을 정리하면, Eg가 커서 전자의 이동이 어려운 물질을 절연체(부도체), Eg가 매우 작거나 없어 전자가 자유롭게 이동함으로써 전류가 잘 흐르는 물질을 전도체, 그리고 Eg가 부도체와 전도체의 중간 정도인 물질을 반도체로 정의할 수 있습니다.

꼬리 질문 1 반도체 재료로 실리콘을 선호하는 이유는 무엇인지 설명하시오. |

반도체 원료인 실리콘은 지구의 지각을 구성하는 원소 중 산소 다음으로 풍부한 원소로, 원재료를 얻기 쉽고 독성이 없어 환경이나 인체에도 무해합니다. 또한 적절한 E g(1.12eV)를 가지며, 무엇보다 실리콘 산화막의 특성이 다른 반도체 재료에 비하여 월등히 우수합니다. 또 녹는점(1,414℃)이 높으며 고순도의 불순물 정제 기술이 발달되어 상대적으로 저가, 고품질의 웨이퍼를 생산할 수 있습니다. |

꼬리 질문 2 페르미 준위에 대해 설명해 보시오. |

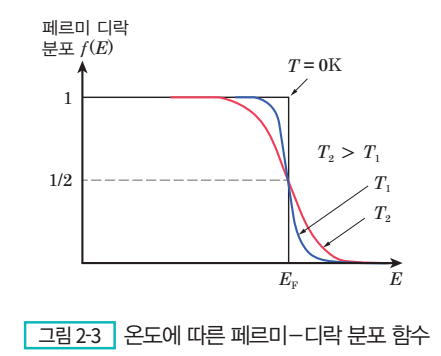

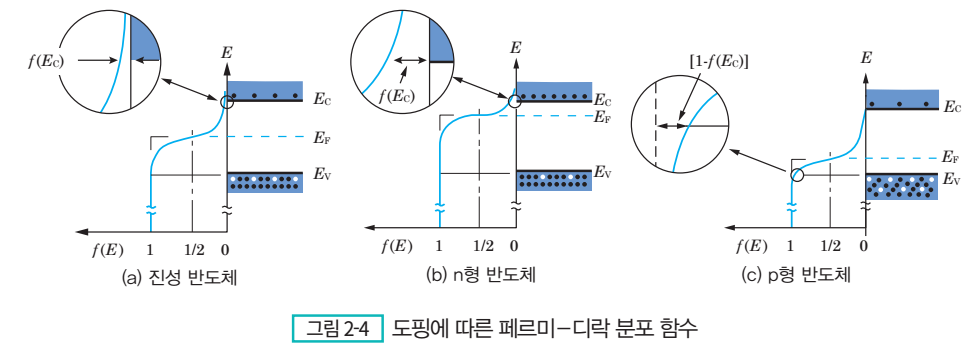

페르미 준위(EF)는 반도체 소자 동작의 분석에 있어 매우 중요한 값으로 두 가지 의미를 갖습니다. 하나는 0K에서 전자가 가질 수 있는 최대 에너지 준위(EF까지 모든 에너지 준위는 채워져 있고 그 이하는 비어 있다)라는 것이고, 다른 하나는 임의의 온도 T에서 전자가 채워질 확률 f(E = EF)이 1/2인 에너지 준위라는 것입니다. 온도가 올라갈수록 페르미 준위 이상의 에너지 준위에서도 전자에 의해 채워질 확률이 증가하게 되고, 이에 따라 페르미 준위 아래쪽에 전자가 채워질 확률은 낮아지게 됩니다. 진성 반도체에서는 온도에 따른 페르미-디락 분포 그래프가 페르미 준위를 기준으로 상하가 대칭인 반면, n형 반도체의 경우에는 전도대의 전자 농도가 가전자대의 정공 농도보다 높기 때문에 페르미 준위가 EC 근처로 올라가게 됩니다. 반대로 p형 반도체의 경우에는 가전자대의 정공 농도가 전도대의 전자 농도보다 높기 때문에 페르미 준위가 EV 근처로 내려오게 됩니다. 페르미 준위는 열 평형 상태의 소자 내에서 일정한 값을 갖습니다. |

핵심 이론 정리

1. 에너지 밴드 모델(Energy band model)

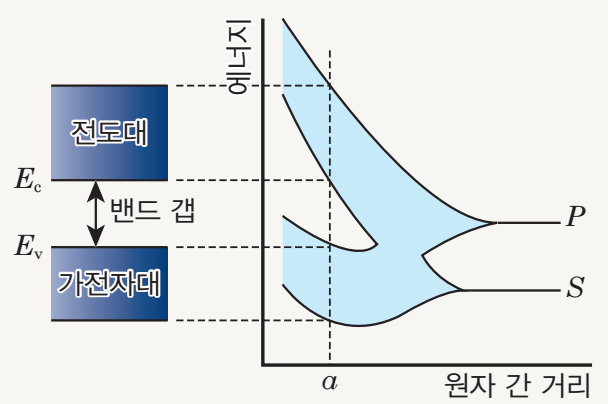

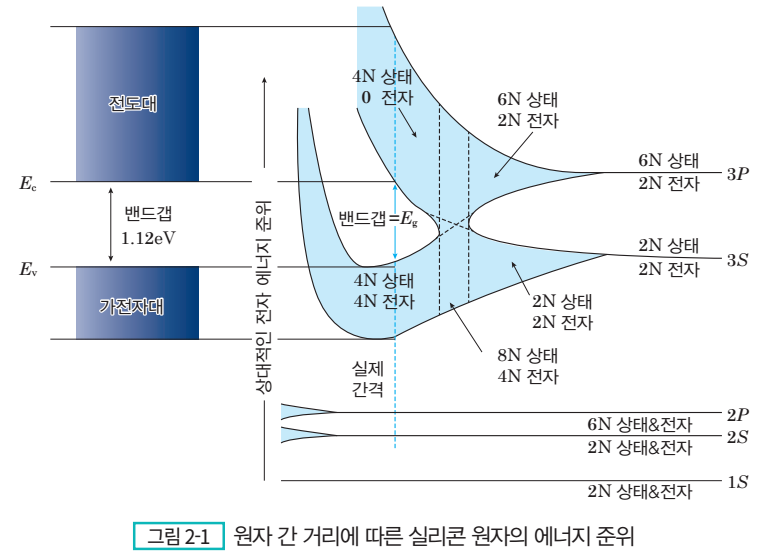

반도체는 원자들이 모여 구성되는 것이므로 독립된 원자 내의 불연속적인 에너지 준위는 원자 간의 간격이 가까워지면 파울리의 배타율(고체 내부에서 전자는 동일한 양자수(Quantum number), 주양자수(n), 부양자수(l), 자기양자수(m), 스핀양자수(s)를 가질 수 없다)에 따라 각각의 에너지 준위가 나뉘어 대역(밴드)을 형성하게 된다. 실리콘의 경우, 다음 [그림 2-1]과 같이 핵에서 가까운 1S에서 2P까지의 N개의 원자에 의한 10N개의 전자가 점유할 수 있는 상태는, 원자 간 거리가 가까워져도 서로 영향을 거의 미치지 못한다. 반면 최외각의 3S23P2의 경우 실제 원자 간 거리까지 가까워지면 3S2의 2N개의 상태와 3P2의 6N개의 상태가 상위 4N, 하위 4N개로 양분되고, 각각 2N개씩 총 4N개의 전자는 절대 온도 0도에서 모두 하위 4N개의 상태에만 존재하게 된다. 이렇게 전자로 가득 차 있는 하위 에너지 대역을 가전자대(Valence band), 상부의 전자가 존재하지 않는 빈 에너지 대역을 전도대(Conduction band)라고 하고, 두 대역 사이의 전자가 점유할 수 없는 에너지 상태를 금지대(Forbidden band)라 하며 이 에너지 차를 금지대 폭 또는 에너지 밴드 갭(Energy band gap, Eg)이라 한다. 또한 전도대의 가장 낮은 에너지 준위를 EC, 가전자대의 가장 높은 에너지 준위를 EV로 표기한다. 실리콘의 경우, 1.12eV의 Eg를 갖는다. 따라서 외부 전계 인가 시 캐리어의 이동에 의한 전류의 형성을 위해서는 가전자대에 있는 전자가 Eg이상의 에너지(열 또는 광에너지)를 받아 Eg를 뛰어넘어 비어있는 전도대로 올라가 자유 전자 형태로 자유롭게 이동할 수 있어야 한다.

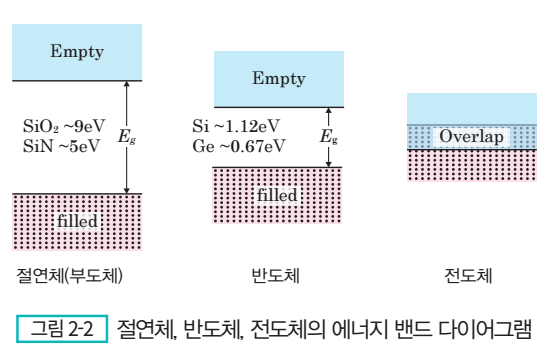

반도체의 개념을 에너지 밴드 이론으로 다시 정의할 수도 있다. [그림 2-2]와 같이 Eg가 ~5eV 이상으로 커 가전자대에서 전도대로 전자의 이동이 어려운 물질을 절연체(부도체), Eg가 매우 작거나 두 대역이 겹쳐져 전자로 채워진 에너지 준위와 전자가 없는 빈 에너지 준위가 공존하므로 외부 전계 인가 시 전자가 자유롭게 이동하여 전류가 잘 흐를 수 있으므로 전도체로 정의할 수 있다. 그리고 Eg가 부도체와 전도체의 중간(~3eV 이하) 정도인 물질을 반도체로 정의할 수 있다.

2. 페르미 준위(Fermi energy level)

절대 온도 T에서 고체 내부의 임의의 에너지 준위에 전자가 존재할(또는 해당 에너지 준위를 전자가 점유할) 확률 함수 f(E)를 페르미-디락 분포 함수(Fermi-Dirac distribution)라 하고 다음과 같은 식으로 표현한다.

페르미 준위(EF)는 반도체 소자 동작의 분석에 있어 매우 중요한 값으로 두 가지 의미를 갖는다. 하나는 [그림 2-3]과 같이 0K에서 전자가 가질 수 있는 최대 에너지 준위(EF까지 모든 에너지 준위는 채워져 있고 그 이하는 비어 있다)라는 것이고, 다른 하나는 임의의 온도 T에서 전자가 채워질 확률 f(E = EF)이 1/2인 에너지 준위라는 것이다. 온도가 올라갈수록 페르미 준위 이상의 에너지 준위에서도 전자에 의해 채워질 확률이 증가하게 되고, 이에 따라 페르미 준위 아래쪽에 전자가 채워질 확률은 낮아지게 된다(페르미 준위를 기준으로 대칭).

진성 반도체는 온도에 따른 페르미-디락 분포 그래프가 페르미 준위를 기준으로 상하가 대칭인 반면, [그림 2-4]와 같이 n형 반도체의 경우는 전도대의 전자 농도가 가전자대의 정공 농도보다 높기 때문에 페르미 준위가 EC 근처로 올라가게 된다. 반대로 p형 반도체의 경우는 가전자대의 정공 농도가 전도대의 전자 농도보다 높기 때문에 페르미 준위가 EV 근처로 내려오게 되고 이때의 정공 농도는 전체 확률 1에서 전자가 존재할 확률 f(EC)를 뺀 값이 된다(1 - f(EC)). 페르미 준위에 대한 다른 중요한 사실은 열 평형 상태의 소자 내에서 페르미 준위가 일정하며 단 하나만 존재한다는 사실이다.

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기