반도체 기초 Ⅱ

학습 포인트 |

반도체 소자는 전자와 정공으로 구성된 캐리어에 의해 전류가 흐른다. 따라서 캐리어가 어떻게 만들어지고 그 거동은 어떠한지를 이해하는 것은 매우 중요하다. 이를 위해서 진성 반도체와 외인성 반도체의 차이점을 명확히 파악하여야 한다. 또 캐리어의 농도로부터 반도체 소자 내의 전기장 및 전위 분포를 알 수 있으므로, 캐리어 농도 계산을 위해 에너지 상태 밀도와 페르미 준위의 정의를 이해하여야 한다. |

개념 맵 |

1 진성 반도체(Intrinsic semiconductor)

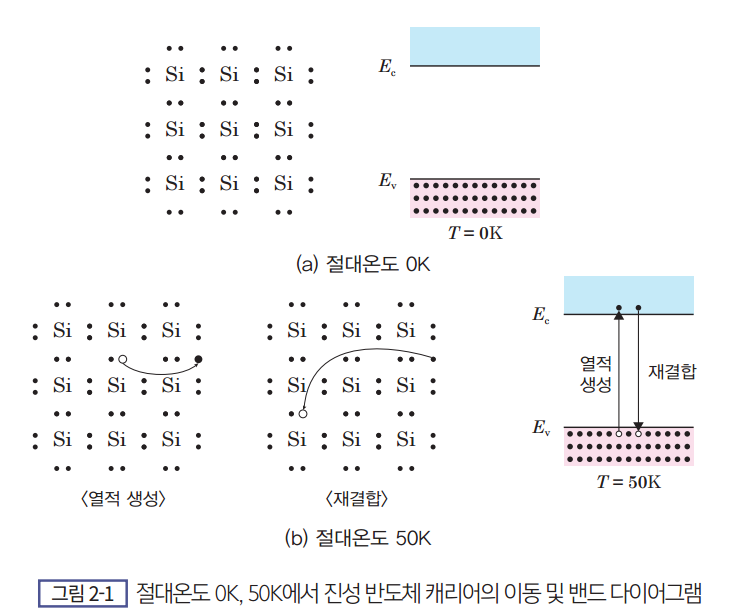

진성 반도체란 불순물이나 결함이 없는 거의 완벽한 실리콘 반도체를 의미한다. [그림 2-1]과 같이 절대온도 0K에서는 전자의 열적 생성1이 없어 전자가 공유결합 내에 묶여 있게 되므로 캐리어의 농도가 0이지만, 절대온도가 0K보다 높아지면 열적 생성에 의해 전도대의 전자와 가전자대의 정공이 쌍을 이뤄 생성된다. 이러한 전자-정공 쌍2 때문에 가전자대의 전자의 농도(n)와 전도대의 정공의 농도(p)가 동일해진다. 즉, n0 = p0 = ni가 된다. 이때 ni를 진성 캐리어 농도(Instrinsic carrier concentration)라 하며, n0, p0는 열 평형 상태3에서의 전자와 정공의 농도이다.

열적 생성1: 가전자대에 있던 전자가 열에너지를 받아 전도대로 올라가고, 그 결과 원래의 가전자대에는 정공이 생기는 것

전자-정공 쌍(Electron Hole Pair, EHP)2: 전도대로 올라간 전자와 가전자대에 생긴 빈 자리인 정공의 쌍

열 평형 상태3: 빛이나 전기 에너지 등의 개입 없이 오직 열에너지만이 주어진 상태

이러한 진성 캐리어 농도(n1)는 주어진 온도에서 어떤 일정한 값을 갖게 된다(300K에서 ni = 1.5 × 1010cm-3). 이렇게 정상 상태4에서 일정한 진성 캐리어 농도를 유지하기 위해서는 [그림 2-1(b)]와 같이 열적 생성률(Generation rate, gi)과 생성된 전자-전공 쌍의 재결합율(Recombination rate, ri)이 같아야 한다.

정상 상태4: 진행 중인 어떤 반응에 있어 외부의 영향 없이 입력과 출력이 일정하게 유지되는 상태

2 외인성 반도체(Extrinsic semiconductor)

진성 반도체는 열적으로 생성된 전자-정공 쌍(EHP)만이 캐리어로 작용하게 되므로, 소자로 사용하기에는 캐리어의 수가 너무 적다. 따라서 순수한 반도체에 Ⅴ족(인, 비소) 또는 Ⅲ족(붕소) 원소와 같은 불순물(도펀트)을 주입(도핑)하여 캐리어 농도를 높임으로써, 반도체의 전기 전도도를 조절한다. 이러한 반도체를 외인성 반도체(Extrinsic semiconductor)라고 하며 도핑량에 따라 고농도에는 ‘+’, 저농도에는 ‘-’ 기호를 붙이기도 한다. 외인성 반도체는 진성 반도체와 달리, 전자의 농도(n)와 정공의 농도(p), 진성 캐리어의 농도(ni)가 서로 다르지만(n0≠p0≠ni), 불순물 주입 후에도 전체적인 전하 중립성(Charge neutrality)이 유지(n0p0 = ni2)되는 특징이 있다.

(1) n(negative)형 반도체

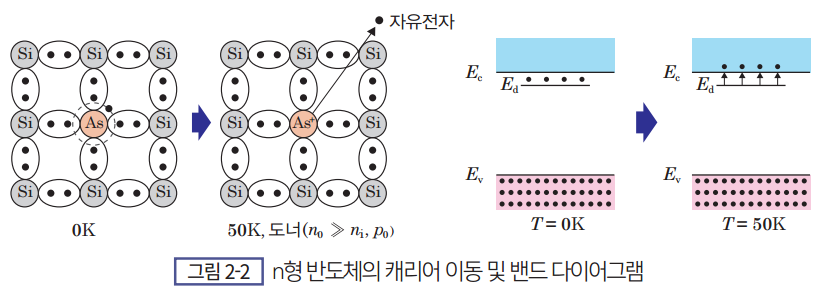

n형 반도체란 진성 반도체에 Ⅴ족 불순물(인, 비소)을 주입한 반도체이다. 이 경우에 Ⅴ족 불순물의 최외각 전자 중 4개는 실리콘과 공유결합을 하고 있지만, 남은 1개의 전자는 핵과의 인력이 약하므로 약간의 에너지만 받아도 쉽게 자유전자가 될 수 있다. 따라서 절대온도 0K에서는 전자가 Ⅴ족 원소에 약하게 구속되어 있지만, [그림 2-2]의 좌측과 같이 0K 이상이 되면 이온화5되어 자유전자로서 전도에 참여하게 된다. 결국 양이온이 된 Ⅴ족 원소는 전자 하나를 내어 놓는다 하여 도너(Donor)라고 명명하고, 전도대역에 전자를 생성하게 하는 전자 생성 원소이다. 따라서 n형 반도체에서 다수 캐리어는 전자, 소수 캐리어는 정공이 된다(n0 ≫ ni, p0).

이온화5: 전기적으로 중성인 원자나 분자가 전자를 얻거나 잃음으로써 음전하 또는 양전하를 가진 이온으로 되는 것

[그림 2-2] 우측의 에너지 밴드 측면에서 보면, 도너 주입으로 인해 전도대 바로 아래에 얕은 도너 에너지 준위(Ed)가 만들어진다. 이 준위에 있던 전자가 에너지를 받으면 전도대로 쉽게 올라가 자유전자가 되는 것이다. 즉 이온화를 위해 (Ec - Ed)만큼의 에너지가 필요하다(인의 경우 ~44meV).

(2) p(positive)형 반도체

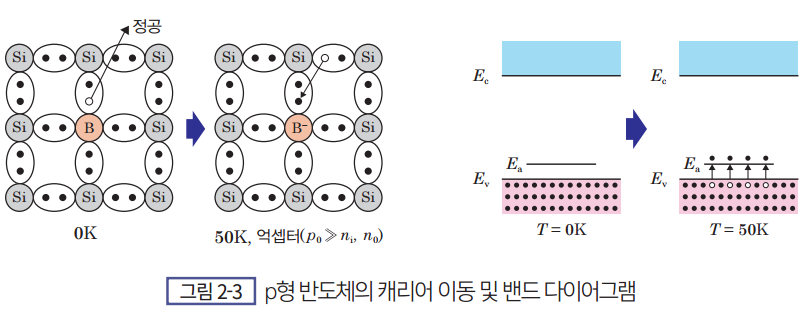

p형 반도체란 진성 반도체에 Ⅲ족 불순물(붕소)을 주입한 반도체이다. 이 경우에 Ⅲ족 불순물의 최외각 전자 3개는 실리콘과 공유결합을 하고, 부족한 1개의 전자 자리에 정공이 발생한다. 따라서 절대온도 0K 이상에서는 [그림 2-3]의 좌측과 같이 주위의 전자가 이 정공으로 쉽게 이동하게 되고, 정공에 의한 전도가 가능해진다. 결국 음이온이 된 Ⅲ족 원소는 전자 하나를 받아 들인다 하여 억셉터(Acceptor)라 명명하고, 가전자대역에 정공을 생성하게 하는 정공 생성 원소이다. 따라서 p형 반도체에서 다수 캐리어는 정공, 소수 캐리어는 전자이다(p0 ≫ ni , n0).

[그림 2-3] 우측의 에너지 밴드 측면에서 보면, 억셉터 주입으로 인해 가전자대 바로 위에 얕은 억셉터(Acceptor) 에너지 준위(Ea)가 만들어지고, 이온화에 필요한 에너지는 Ea - Ev(~45meV)가 된다. 따라서 에너지를 받으면 가전자대의 전자가 쉽게 올라가 정공이 만들어지고, 이때 만들어지는 정공이 전도에 참여하는 것이다. 반면 억셉터 에너지 준위(Ea)로 올라온 전자는 전도에 참여하지 못한다.

3 페르미 에너지 준위(Fermi energy level)와 캐리어 농도

(1) 에너지 상태 밀도

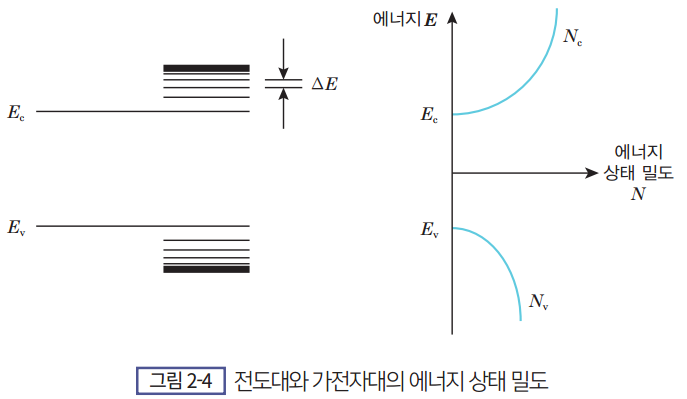

반도체 내의 캐리어 농도를 구하기 위해서는 먼저 에너지 상태 밀도 함수를 정의해야 한다. 앞서 설명한 바와 같이 에너지 밴드는 수많은 에너지 준위들로 구성되어 있는데, 이 중 전자 또는 정공이 점유할 수 있는 자리의 밀도를 에너지 상태 밀도(Density of states, N(E))라 하고, [개/cm3·eV]의 단위를 갖는다.

[그림 2-4]에서 Nc와 Nv는 각각 전도대와 가전자대의 에너지 E에서의 에너지 상태 밀도를 의미하며, Ec와 Ev에서 밀도가 낮고, Ec 및 Ev로부터 멀어질수록 밀도가 높아지는 특징이 있다.

- Nc(E) = (전도대에서 ΔE 내에 존재하는 상태들의 수) / (ΔE × 부피)

- Nv(E) = (가전자대에서 ΔE 내에 존재하는 상태들의 수) / (ΔE × 부피)

(2) 페르미 준위(Fermi level)

고체 내부의 임의 에너지 준위에서 전자가 존재할(또는 해당 에너지 준위를 전자가 점유할) 확률 함수를 페르미-디락 분포 함수(Fermi-Dirac distribution, f(E))라 하고 다음과 같은 식으로 표현한다.

(k: 볼츠만 상수로 8.62 × 10-5 eV/K (kT = 0.026eV), EF: 페르미 에너지 준위)

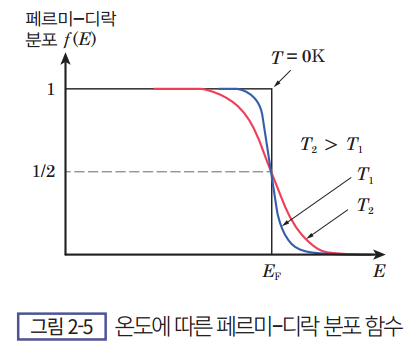

위 식에 표현된 페르미 에너지 준위는 반도체 소자 동작의 분석에 있어 매우 중요한 값으로, 두 가지 의미를 갖는다. 하나는 [그림 2-5]의 검은 실선과 같이 0K에서 전자가 가질 수 있는 최대 에너지 준위(EF까지 모든 에너지 준위는 채워져 있고 그 이하는 비어 있다)라는 것이고, 다른 하나는 임의의 온도 T에서 전자가 채워질 확률 f(E)이 1/2인 에너지 준위라는 것이다. 온도가 올라갈수록 페르미 준위 이상의 에너지 준위(E > EF)에서도 전자에 의해 채워질 확률이 증가하게 되고, 이에 따라 페르미 준위 아래쪽(E< EF)의 전자가 채워질 확률은 낮아지게 된다.

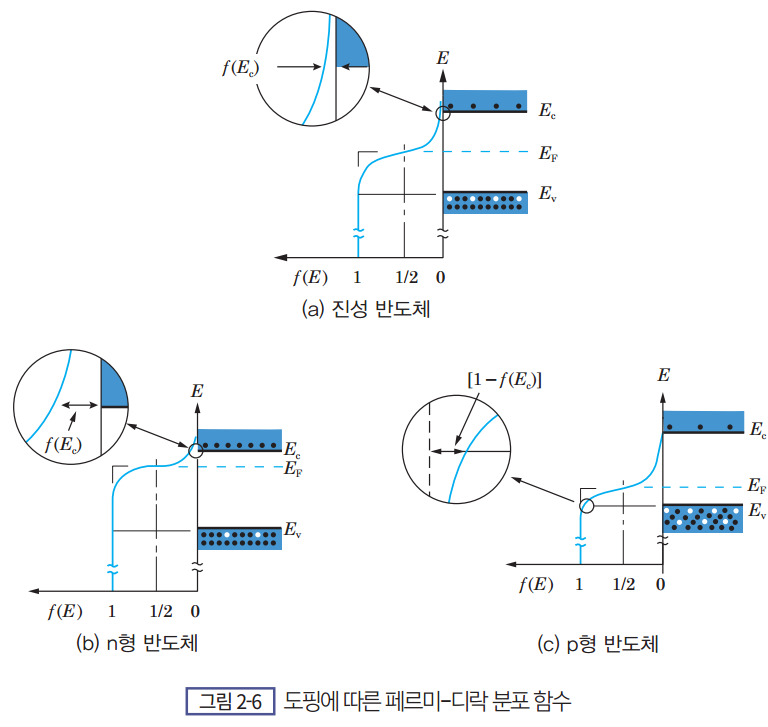

한편 [그림 2-6(a)]와 같이 진성 반도체의 페르미 준위는 Ev와 Ec의 중간에 위치하지만, n형과 p형 반도체는 그렇지 않다. n형 반도체는 전도대의 전자 농도가 가전자대의 정공 농도보다 높기 때문에 페르미 준위가 Ec 근처로 올라가게 되고, 반대로 p형 반도체는 가전자대의 정공 농도가 전도대의 전자 농도보다 높기 때문에 페르미 준위가 Ev 근처로 내려온다. 이때의 정공이 존재할 확률은 전체 확률 1에서 전자가 존재할 확률 f(Ec)를 뺀 [1 - f(Ec)]이 된다. 이 외에도 페르미 준위에 대해 알아야 할 중요한 사실 하나는, 열 평형 상태에 있는 소자 내에서 페르미 준위는 모든 영역에서 일정하다는 사실이다.

(3) 평형 상태에서의 캐리어 농도

우리가 사용하는 반도체 소자는 외부에서 인가하는 전압이나 신호를 통해 반도체 내부의 전하의 흐름을 제어하게 된다. 이때 전하의 흐름, 즉 전류의 크기는 캐리어의 농도로부터 알 수 있으므로, 우리는 반도체 내의 캐리어 농도를 구하는 방법을 알아야 한다. 먼저 전자의 농도는 다음 식과 같이 전도대의 상태 밀도 Nc(E)와 페르미-디락 분포 f(E)을 곱하여 전체 에너지 대역 내에서 모두 적분하면 된다. 마찬가지로 정공의 농도는 가전자대의 상태 밀도 Nv(E)에 정공이 점유할 확률(전자가 점유하지 않을 확률) [1- f(E)]을 곱하여 적분하면 된다.

Nc(E): 전도대 내 에너지 E 에서의 상태 밀도

Nv(E): 가전자대 내 에너지 E 에서의 상태 밀도

f(E): 전자가 점유할 확률

1-f(E): 정공이 점유할 확률

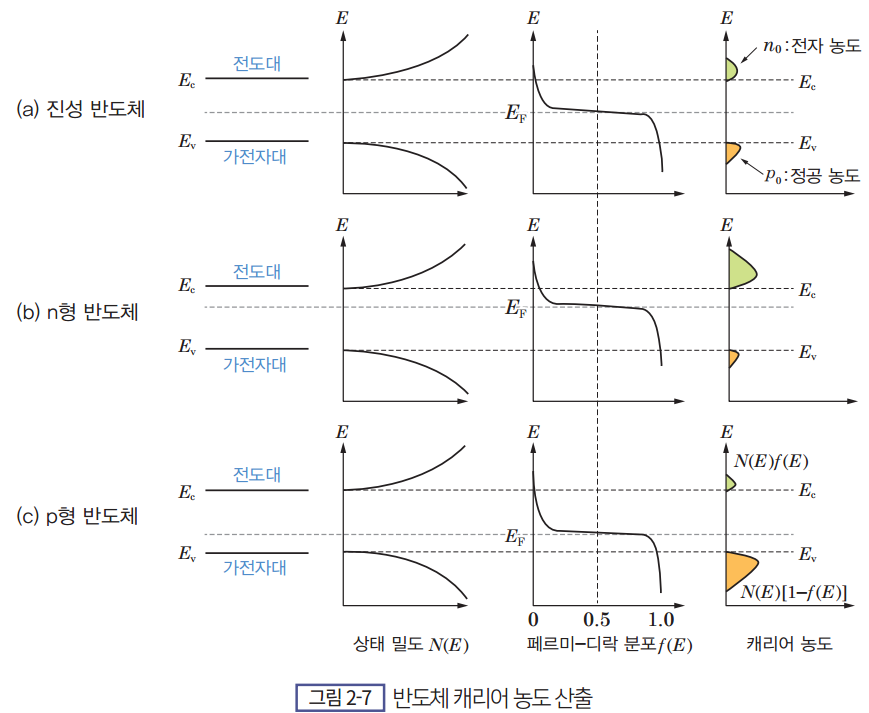

위 식을 토대로, [그림 2-7]에는 상태 밀도와 페르미-디락 분포, 그리고 이 두 값의 곱을 적분하여 구한 캐리어 농도가 나타나 있다. 진성 반도체의 경우 전도대과 가전자대에 있는 각각의 전자와 정공의 농도가 같으나, n형 반도체에서는 전도대의 전자의 농도가 더 증가하였고, p형 반도체에서는 가전자대의 정공의 농도가 더 증가하였음을 알 수 있다. 이는 도핑에 따른 페르미-디락 분포 함수가 위로 또는 아래로 움직인 결과이다.

앞의 적분식에 근사 조건을 사용해 식을 정리하면, 다음과 같이 간략한 식으로 캐리어 농도를 표현할 수도 있다.

(Ei: 진성 페르미 준위로 Ec와 Ev의 중간 지점의 에너지 준위, ni: 진성 캐리어 농도로 1.5 × 1015cm-3(300K))

위 식에 의하면, n형 또는 p형 반도체처럼 페르미 준위(EF)가 전도대나 가전자대 쪽으로 이동하게 되는 경우, 페르미 준위(EF)와 진성 페르미 준위(Ei) 간의 차이가 생겨 평형 상태의 전자나 정공의 농도는 지수 함수적으로 증가함을 알 수 있다. 또한 (식 2-6)을 통해, 평형 상태에서 전자나 정공의 농도 중 하나만 알면 나머지는 쉽게 구할 수 있다는 사실도 확인할 수 있다. 그러므로 전자의 농도가 증가하면 정공의 농도는 감소한다는 사실도 알 수 있다.

이 시점에서, 일부 독자들은 ‘도핑에 따라 전자나 정공과 같은 다수 캐리어의 농도가 증가하는 것은 당연하지만, 소수 캐리어의 농도가 감소하는 이유는 무엇일까?’하는 의문을 가질 수도 있을 것이다. 이는 n형 반도체의 경우 전도대의 전자 농도가 너무 높아지면 전자가 가전자대로 내려와 정공과 재결합함으로써 가전자대의 정공의 농도가 감소하기 때문으로 설명할 수 있겠다.

4 캐리어 농도의 온도 의존성

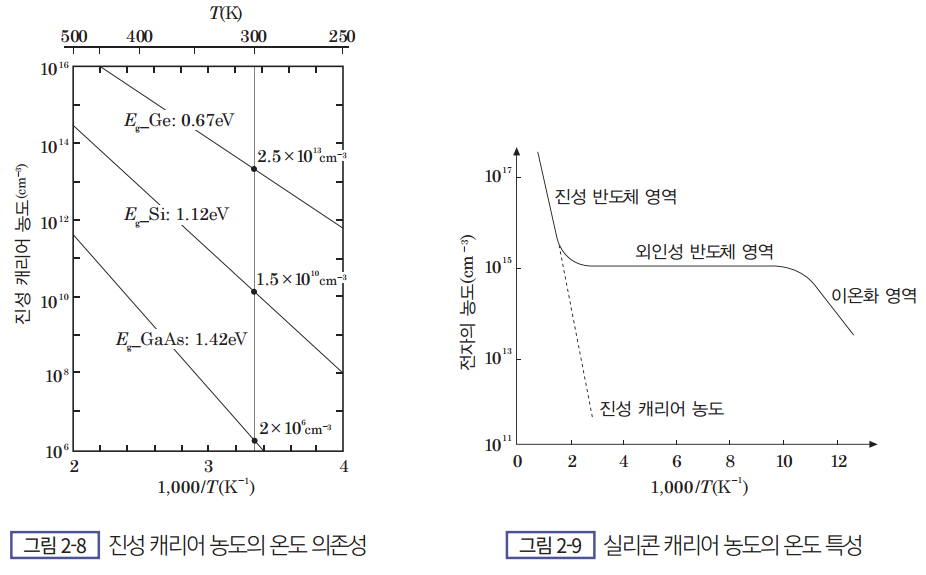

[그림 2-8]은 반도체별 진성 캐리어 농도의 온도 의존성을 나타낸다. 열적 생성으로 인해 생겨나는 진성 캐리어는 그 농도가 당연히 온도에 지수 함수적으로 의존하고 있지만, 이 외에 에너지 갭의 영향도 받고 있다. 에너지 갭이 클수록 가전자대의 전자가 전도대로 올라가는 데 많은 에너지가 요구되므로, 에너지 갭이 크면 캐리어 수는 줄어들 수밖에 없는 것이다.

[그림 2-9]에서는 1015cm-3의 도너로 도핑된 반도체에서 온도에 따른 전자 농도의 상관 관계를 보여주고 있다. 매우 낮은 온도에서는 도너에 속한 전자가 도너 원자에 묶여 전자의 농도가 매우 낮지만, 온도가 상승함에 따라 도너 원자가 모두 이온화되면서 전자 농도가 증가하게 된다. 이 영역(~100K)을 이온화 영역이라고 한다. 이후 완전 이온화가 되면 전도대의 전자 농도는 주입한 도너 원자의 수와 같게 되고(n0≒ND = 1015cm-3), 전자수는 열적 생성으로 인한 전자-정공 쌍 수가 아직 도너에 의한 전자의 농도(n0) 대비 매우 적으므로 일정 온도 구간 동안 1015cm-3의 농도를 유지하게 된다. 따라서 이 구간을 외인성 영역이라 한다. 이보다 온도가 더욱 높아지게 되면 열적 생성으로 생긴 전자-정공 쌍에 의해 전자수가 매우 증가하여 도너에 의한 전자수를 초과하게 되므로(ni ≫ND) 진성 반도체 영역이 된다. 하지만 진성 반도체 영역이므로 페르미 준위는 에너지 밴드의 중앙에 위치한다. 소자의 동작은 전자-정공 쌍에 의한 캐리어 생성보다는 도핑에 의한 캐리어 농도 조절이 훨씬 안정적이므로, 소자 설계 시 소자의 동작 온도를 외인성 영역의 온도보다 훨씬 낮게 가져가도록 설계한다.

5 보상(Compensation)과 공간 전하 중성 조건(Space charge neutrality)

실리콘에 도너와 억셉터 도펀트를 중복하여 도핑한 경우, 농도가 높은 쪽이 낮은 쪽을 보상하여 높은 쪽으로 반도체 타입이 바뀐다. 이것이 보상(Compensation)의 의미이며, 이때 농도는 도너와 억셉터 간의 농도 차이가 된다. 예를 들어, 도너를 1018cm-3, 억셉터를 1016cm-3 도핑한 경우, 이 반도체는 도너를 도핑한 반도체(n형 반도체)가 되고 최종 농도(n0)는 1018 - 1016cm-3이 되는 것이다.

공간 전하 중성 조건에 대해서는, 앞서 설명한 바와 같이 외인성 반도체도 전체적으로는 중성이므로 반도체 내의 모든 전하들의 전하량의 합은 0이 되어야 한다. 즉, ‘음의 전하를 띠는 전도대의 전자와 억셉터 이온의 전하량의 합’이 ‘양전하를 갖는 가전자대의 정공과 도너 이온의 전하량의 합’과 같아야 한다는 것이다.

따라서 단일 도핑의 경우, n형 반도체는, n0 ≫ p0이므로 n0≒ND, p형 반도체는 p0 ≫ n0이므로 p0≒NA가 되고, 상호 보상 도핑 후 n형 반도체가 된 경우는 n0≒ND - NA, p형 반도체가 된 경우는 p0≒NA - ND가 된다(NA, ND 완전 이온화의 경우).

6 반도체 내의 캐리어의 운동

(1) 열 평형 상태에서의 캐리어의 운동

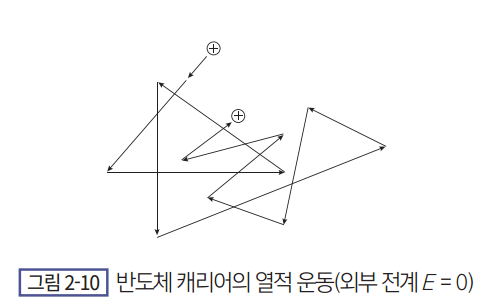

반도체 내의 전자와 정공들은 [그림 2-10]과 같이 열에너지를 받아 계속해서 매우 빠른 속도로 움직이고 있다(전자의 평균 열적 속도(Thermal velocity)는 ~107cm/sec 정도). 이들의 움직임은 직선 운동이 아니며, 결정 내의 원자, 결함, 불순물 또는 다른 전자들과 충돌하면서 불규칙한 산란6을 하게 된다. 거시적인 관점에서 캐리어는 무작위한 방향으로 움직이므로, 많은 수의 캐리어에 대해 평균한 순(Net) 속도는 0이 된다. 따라서 캐리어의 열적 운동은 전류를 생성하지 않는다.

산란6: 파동이나 빠른 속도의 입자가 분자, 원자, 미립자 등에 충돌하여 운동 방향을 바꾸고 흩어지는 현상

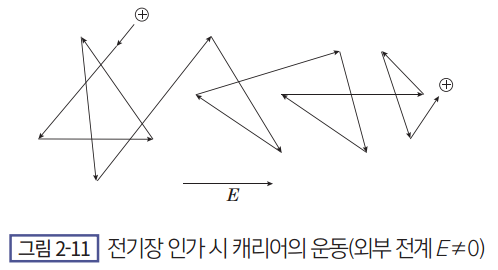

(2) 캐리어의 표동(Drift)

열 평형 상태에서의 운동과는 다르게, [그림 2-11]과 같이 반도체에 외부 전계가 인가된 경우에는 캐리어들의 평균 속도가 더 이상 0이 아니다. 이는 캐리어들이 전계가 인가되기 전의 자체적인 열적 운동을 하면서, 동시에 전계의 영향을 받은 운동도 하고 있기 때문이다. 이러한 전계의 영향을 받은 움직임을 표동(Drift)이라 하고, 이 움직임의 속도를 표동 속도(Drift velocity)라고 한다.

정상 상태에서 캐리어의 표동 속도는 다음 식과 같이 나타낼 수 있으며, 이는 캐리어의 운동량과 전계 내에서 캐리어가 받는 힘, 그리고 캐리어의 충돌 간 평균 자유 시간의 관계로부터 유도해 낼 수 있다. 전자의 경우에는 전계 방향의 반대 방향으로 이동하기 때문에 음의 부호가 붙는다.

-

-

-

-

유효 질량7: 고체 내의 격자의 영향을 고려하여 캐리어들의 움직임을 자유로운 공간에서의 움직임과 유사하게 계산할 수 있도록 변형한 캐리어들의 질량

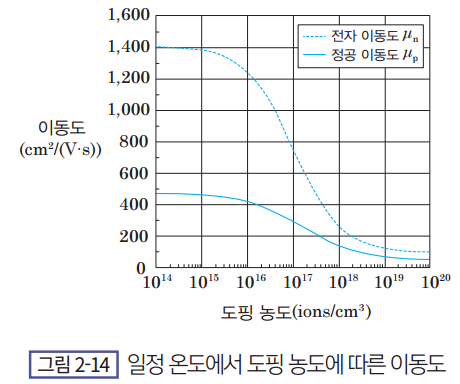

[표 2-1]은 대표적인 반도체인 실리콘과 게르마늄 반도체의 캐리어 이동도를 보여준다. 이동도(Mobility)란 해당 반도체 내에서 캐리어가 얼마나 쉽게 움직일 수 있는지를 나타내는 값으로, 단위는 [cm2/V·s]이다. 이때, 정공의 이동도가 전자의 이동도보다 훨씬 느린 이유는 유효 질량이 전자보다 무겁기 때문이다.

표 2-1 실리콘과 게르마늄 반도체의 캐리어 이동도

구분 | Si | Ge |

전자의 이동도 | 1,400 | 3,900 |

정공의 이동도 | 470 | 1,900 |

(3) 이동도(Mobility)의 온도 및 도핑 농도 의존성

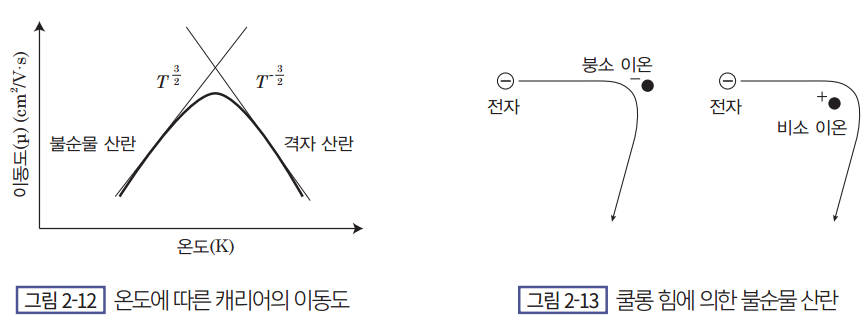

[그림 2-12]는 온도에 따른 캐리어의 이동도를 나타낸 것이다. 온도가 낮은 경우에는 캐리어들의 움직임이 느려, 캐리어가 도펀트 이온 사이를 통과할 때 [그림 2-13]과 같은 전기적 척력 혹은 인력(쿨롱의 힘)에 의한 불순물 산란(Impurity scattering)이 일어난다. 이는 캐리어의 이동도를 감소시키는 주 원인이 된다. 반면 온도가 증가하면 캐리어들의 움직임이 활발해지고 이에 따라 불순물 산란도 감소하여 이동도는 증가하게 된다.

그러나 고온이 되면 격자 진동에 의해 캐리어 이동 시 격자와의 충돌에 의한 격자 산란(Lattice scattering)8이 일어나고 캐리어의 이동도는 다시 감소하게 된다. 이러한 이동도의 온도(T) 의존성은, 불순물 산란의 경우 근사적으로 T

격자 산란8: 결정 내 원자들의 집합적인 진동(격자 진동)을 포논(Phonon)이라 하고, 격자 산란을 포논 산란(Phonon scattering)이라고도 함.

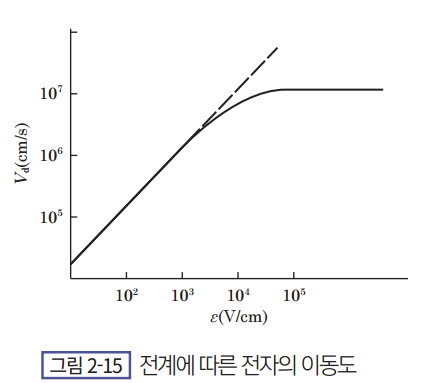

(4) 이동도와 강 전계효과

캐리어의 표동을 설명하면서 표동 속도가 전계에 비례(

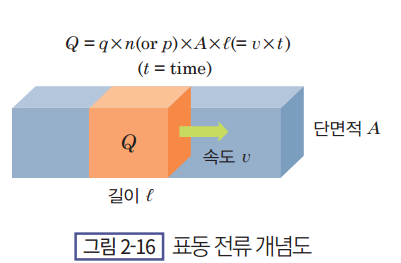

(5) 캐리어와 표동 전류(Drift current)

표동 전류(Drift current)는 외부 전계에 의한 캐리어의 표동(Drift)으로 발생되는 전류이며, [그림 2-16]으로부터 다음과 같은 식이 유도된다.

전자의 표동 전류(

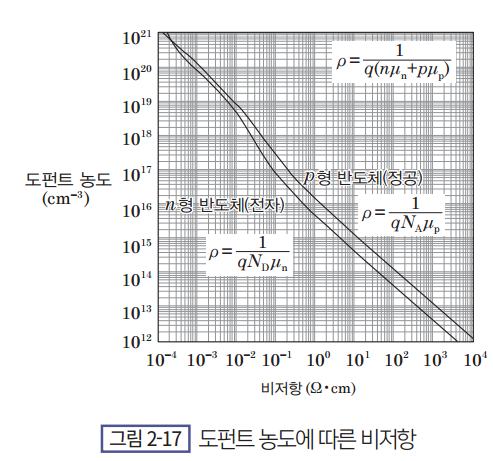

[그림 2-17]에는 도펀트 농도에 따른 비저항의 관계를 나타내었다. 동일한 도펀트 농도에서 전자의 비저항이 정공보다 작은 이유는 전자의 이동도가 크기 때문이며, 도펀트의 농도가 증가함에 따라 선형적으로 감소하던 비저항이 1016cm-3 근처에서 꺾이는 이유는 앞에서 펴봤듯이 농도 증가 시 발생하는 불순물 산란에 의해 캐리어의 이동도가 감소했기 때문이다.

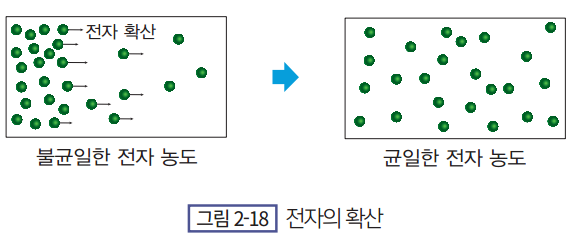

(6) 확산 전류(Diffusion current)

반도체에 흐르는 전류 중에는 앞서 살펴본 표동 전류 외에 캐리어의 농도 차이로 인해 생성되는 확산 전류(Diffusion current)가 있다. 확산이란 상대적으로 농도가 높은 쪽에서 낮은 쪽으로 캐리어가 이동하는 현상으로, 확산에 의한 전자(정공)의 흐름을 전자(정공) 플럭스(Electron(Hole) flux)라고 한다. 전자(정공) 플럭스는 캐리어 농도의 기울기에 비례하는데 그 비례 상수를 확산 계수(D)라 한다. 확산 계수는 입자가 해당 반도체 내에서 얼마나 빨리 확산할 수 있는지에 대한 척도가 되며, 단위로는 [cm2/s]를 사용한다.

표 2-2 전자 및 정공의 확산 계수

반도체 | 전자 확산 계수 | 정공 확산 계수 |

Si | 35 | 12.4 |

Ge | 101 | 49.2 |

전자(정공) 플럭스 앞의 음의 부호는 확산에 의한 입자의 실질적 운동이 입자의 농도를 감소시키는 방향이기 때문에 붙는 것이고, 전자의 확산 전류의 경우에는 자체의 음의 전하량으로 인해 양의 부호로 바뀌게 된다. 따라서 결과적으로는 전자와 정공의 전류 방향이 서로 반대가 된다. 이들 전자(전공) 플럭스에 전하량(q)을 곱하면, 다음과 같이 단위 면적을 지나는 확산 전류 밀도를 구할 수 있다.

한편 캐리어 농도의 차이와 외부 전계가 동시에 있는 경우, 반도체 내부에 흐르는 전체 전류는 표동 전류 성분과 확산 전류 성분을 모두 합한 것므로, 다음과 같은 식으로 나타낼 수 있다.

열 평형 상태에서 전체 전류가 0이라는 사실로부터 확산 계수와 이동도 사이에 다음과 같은 관계가 성립되며, 이를 아인슈타인 관계식(Einstein relationship)이라 한다.

기출문제로 정리하기 ※ 기출문제를 읽고 스스로 답변해 본 후, 이와 관련된 ‘이론 페이지’의 내용을 확인하여 자신의 답안과 비교합니다. | 이론 페이지 |

최신 기출 1 반도체란 무엇이고 반도체 소자 제작에 실리콘이 주로 사용되는 이유에 대해 설명하시오. | p.61, 64 |

최신 기출 2 실리콘 반도체의 에너지 밴드 다이어그램에 대해 설명하시오. | p.65 |

최신 기출 3 n형과 p형 반도체의 차이점에 대해 설명하시오. | p.70~71 |

최신 기출 4 페르미 준위에 대해 설명하시오. | p.72~73 |

최신 기출 5 반도체 내의 표동 전류와 확산 전류에 대해 설명하시오. | p.80~81 |

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기