MOSFET

학습 포인트 |

MOS 커패시터의 원리를 기반으로 현대 반도체 제품을 구성하는 가장 핵심적인 소자인 MOSFET의 각 동작 영역별 동작 원리를 이해하고 미세화에 따른 단 채널 효과 문제와 그 해결책에 대해 알아본다. 또한 최신 MOSFET 기술에 대해서도 학습한다. |

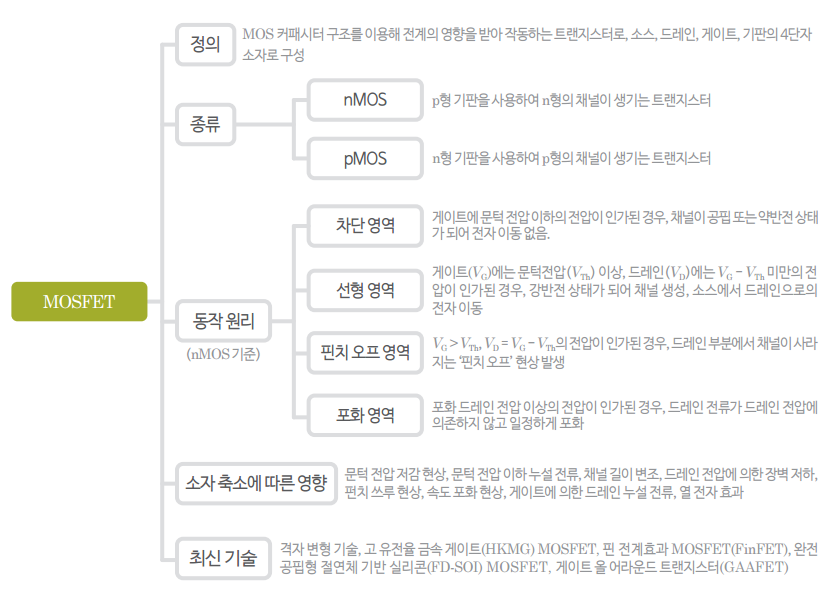

개념 맵 |

1 MOSFET의 구조

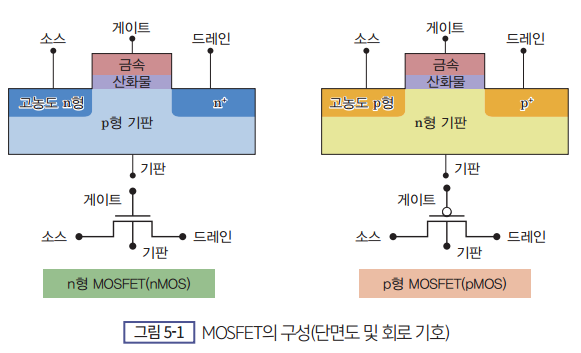

MOSFET은 금속 산화막 반도체 전계효과 트랜지스터(Metal Oxide Semiconductor Field Effect Transistor)의 약자로서, MOS 커패시터 구조1를 이용해 전계의 영향을 받아 작동하는 트랜지스터로 주로 증폭기 또는 스위치 등으로 사용된다. [그림 5-1]과 같이 MOS 커패시터의 양단에 2단자(소스, 드레인)를 추가하여, 게이트(Gate), 기판(Substrate), 소스(Source), 드레인(Drain)의 4단자로 구성된다. 이때 소스는 캐리어(전자 또는 정공)를 공급하는 단자를, 드레인은 캐리어가 빠져나가는 단자를 의미한다. MOS 커패시터는 게이트에 문턱 전압 이상의 전압을 인가했을 때 반도체 표면에 반전층(Channel)이 생겨 전하들이 모이는 원리였지만, MOSFET은 추가적으로 드레인과 소스 사이에 전압을 인가하여, 이때 생긴 전계에 의해 채널의 전하들이 움직여 전류가 흐르게 된다.

MOS 커패시터 구조1: 금속-산화물-반도체의 구조

MOSFET은 기판의 종류와 채널에 따라 두 가지로 나뉜다. 먼저 p형 기판을 사용하여 n형의 채널이 생기는 트랜지스터는 n형 MOS 트랜지스터(nMOSFET, nMOS), 이와 반대로 n형 기판을 사용해 p형의 채널이 생기는 트랜지스터는 p형 MOS 트랜지스터(pMOSFET, pMOS)라고 한다. 여기에서 잠깐, nMOS와 pMOS의 차이를 생각해보자. nMOS는 소스와 드레인에 고농도의 Ⅴ족 원소인 비소(As) 또는 인(P)을 주입하여 형성되고, pMOS는 고농도의 Ⅲ족 원소인 붕소(B)를 주입하여 형성된다. 또 nMOS는 드레인 쪽의 전압이 소스 쪽의 전압보다 높아 드레인에서 소스 쪽으로 전류가 흐르지만, pMOS는 소스 쪽의 전압이 더 높으므로 소스에서 드레인 쪽으로 전류가 흐른다. 회로도상의 기호는 [그림 5-1]의 하단처럼 도식하며, pMOS는 게이트에 빈 원을 표시함으로써 nMOS와 구별되게 한다.

2 MOSFET의 동작 원리

(1) 에너지 밴드 다이어그램

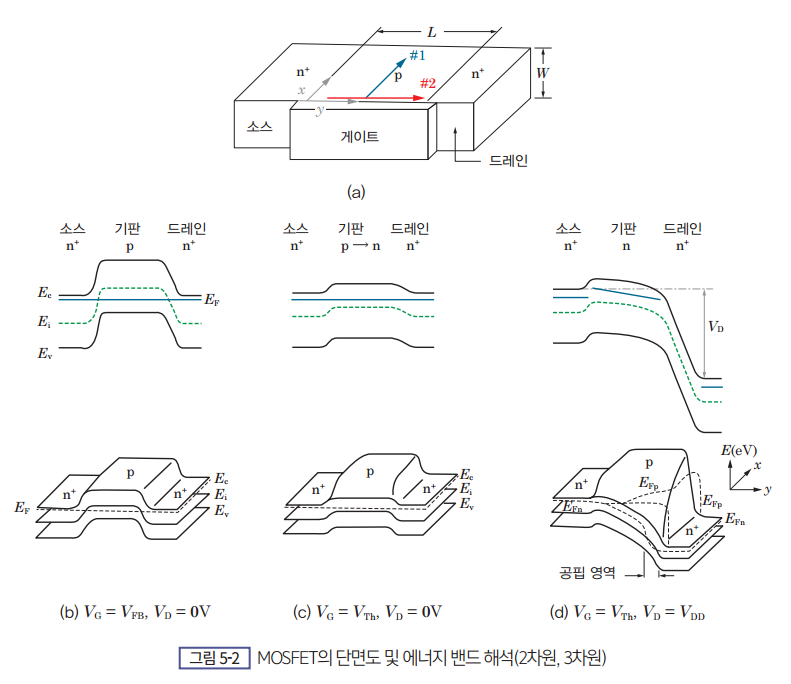

MOSFET의 동작 원리는 MOS 커패시터에서와 마찬가지로, nMOS를 기준으로 설명한다. [그림 5-2]는 nMOS의 구조와 에너지 밴드를 나타낸 것이고, [그림 5-2(a)]에서 nMOS 구조에 있는 화살표 #1은 MOS 커패시터 단원에서 설명 시에 에너지 밴드를 그렸던 방향이다. 하지만 실제로 캐리어가 이동하는 방향은 화살표 #2 방향이므로, 이 방향의 2차원 및 3차원 에너지 밴드를 가지고 MOSFET의 동작 원리를 설명하도록 하겠다.

[그림 5-2(b)]는 MOS 커패시터의 평탄대(Flat band)2 상태(VG = VFB)로, 아직 채널이 형성되지 않은 상태이다. 드레인에 전압을 인가하지 않은 상황(VD = 0V)이므로 드레인 전류도 흐르지 않는 열 평행 상태이다. 따라서 페르미 준위(EF)가 일정하고, 소스 및 드레인과 p형 기판의 접합부에는 공핍 영역이 형성되어 공핍 영역 공간 전하로 인한 내부 전위(Vbi)가 발생한다.

평탄대2: 평탄 밴드를 의미. 실제 MOS 커패시터를 평탄대 상태로 만들기 위해서는 게이트 전압(V G)에 평탄대 전압(VFB)만큼을 걸어야 함.

[그림 5-2(c)]는 게이트에 문턱 전압을 인가(VG = VTh)하고, 드레인에는 아직 전압을 인가하지 않은(VD = 0V) 강 반전 상태이다. n-p-n 접합에서 p형 반도체의 진성 페르미 준위(Ei)가 페르미 준위(EF) 아래로 내려와 n형 반도체로 반전된 것을 확인할 수 있다. 드레인 전압(VD = 0)이 인가되지 않아 페르미 준위가 일정하고, 소스와 드레인 양단에 전위차가 없으므로 전류가 흐르지 않는다.

이제 [그림 5-2(d)]와 같이 드레인에 양의 전압(VDD)3을 인가하면 드레인 쪽의 밴드가 더 아래로 휘게 된다. 이렇게 되면 소스의 전자가 전계에 의해 표동(Drift)되어 드레인으로 이동하고, 전류가 흘러 평형 상태가 아니게 되므로 페르미 준위는 더 이상 상수가 아니다.

VDD3: 동작 드레인 전압

(2) 각 상태별 캐리어의 움직임 및 전류-전압 특성

이번 절에서는 MOSFET의 동작 원리를 게이트와 드레인에 인가되는 전압에 따라 좀 더 상세히 알아보고, 입력 신호의 전달(VG - ID) 및 출력(VD - ID) 특성에 대해서도 살펴보도록 하자. 본 서에서는 특별한 언급이 없는 한 소스(Source) 단자를 접지(0V)시켜 MOSFET 각 단자의 기준 전압으로 삼는다(예 VD = VDS).

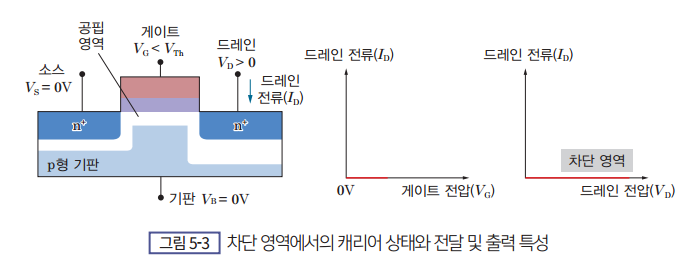

① 차단 영역(Cut-off region) (VG < VTh)

[그림 5-3]과 같이, 게이트에 문턱 전압 이하의 전압 (VG < VTh)이 인가된 경우를 보자. 이 경우에 채널은 공핍 또는 약 반전 상태가 되어, 드레인에 전압이 인가되더라도 소스에서 드레인으로의 전자 이동이 일어나지 않는다. 이렇게 드레인 전류가 흐르지 않는 영역을 차단 영역(Cut-off region)이라고 한다. 이 영역에서는, 후술할 문턱 전압 이하의 작은 전류가 흐를 수 있다.

② 선형 영역(Linear region) (VG > VTh, VD < VG - VTh)

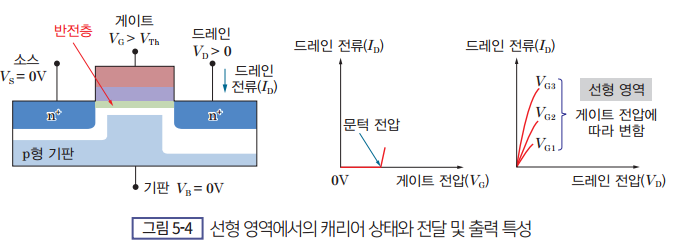

이번에는 문턱 전압 이상 (VG > VTh)이면서 드레인에 VG - VTh 미만의 전압을 인가하였다. 이 상황에서는 강 반전 상태가 되어 채널이 생성되고, 소스에서 드레인으로의 전자 이동이 일어나 드레인 전류가 흐르게 된다. 이때 반전층(채널)은 소스와 드레인 사이에서 저항의 역할을 하게 되므로, 드레인 전류가 드레인 전압에 대해 선형적으로 흐르게 되며 이 영역을 선형 영역(Linear region)이라 한다.

MOS 커패시터 단원에서 설명한 문턱 전압의 식(식 4-9)과 반도체 기초 Ⅱ단원에서 언급한 표동(Drift) 전류의 식(식 2-10)을 이용하면, 선형 영역에서의 드레인 전류(ID)를 나타내는 수식을 유도할 수 있다(이때 공핍 영역의 전하는 채널 전위 변화에 무관하다고 가정한다). 이 식을 이용해 선형 영역(낮은 드레인 전압

(W: nMOS의 채널 폭(Width), L: 채널의 길이(Length),

이 식은 강 반전 상태까지 유효하며, 드레인 전류가 드레인 전압에 비례하여 흐르는 것을 알 수 있다. 이러한 특성은 [그림 5-4]의 출력(VD - ID) 그래프에서도 볼 수 있다. 한편 그래프에서 드레인 전압이 어느 정도 증가하면 드레인 전류의 증가폭이 감소하면서 약간 휘는 현상이 보여진다. 이는 드레인 전압이 증가하면 드레인 부분의 공핍 영역이 증가하면서 반전층 폭이 감소하게 되어 캐리어 수가 감소하기 때문이다. 수식적으로는 드레인 전류 식의

③ 핀치 오프 영역(Pinch-off region) (VG > VTh, VD = VDSAT = VG - VTh)

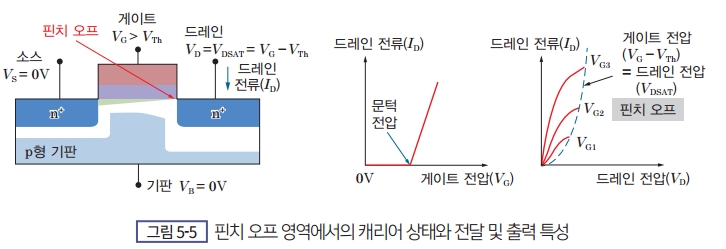

이번에는 문턱 전압 이상의 게이트 전압이 인가된 상태(VG > VTh)에서, 드레인 전압이 점차 증가하여 게이트 전압과 같아진 상황(VD = VG - VTh)을 보자.

이 경우에는 [그림 5-5]와 같이 게이트 전압에 의해 생성된 반전층(채널)이 드레인 전압에 의해 상쇄된다. 결국 드레인 부분에서 채널이 사라지는 핀치 오프(Pinch-off) 현상이 발생하게 되는데, 이렇게 게이트 전압(VG) - 문턱 전압(VTh)과 동일하게 되는 드레인 전압을 포화 드레인 전압(Saturation drain voltage, VDSAT)이라고 한다. 따라서 게이트 전압이 증가함에 따라 핀치 오프가 발생하는 포화 드레인 전압(VDSAT)도 증가하게 되는 것이다.

④ 포화 영역(Saturation region) (VG > VTh, VD > VDSAT)

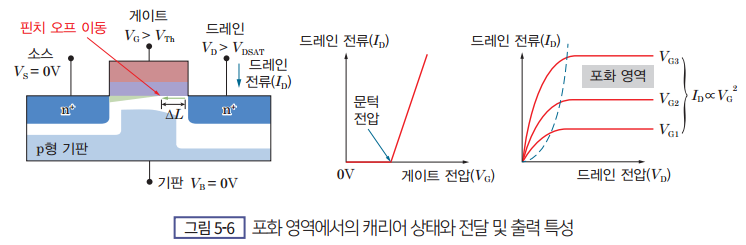

포화 영역은 핀치 오프 상태에서, [그림 5-6]과 같이 드레인 전압이 더 증가해 포화 드레인 전압 이상(VD > VDSAT)이 된 상황이다. 이 상황에서는 핀치 오프되는 지점이 드레인에서 소스 쪽으로 계속 밀리며, 드레인 전류가 더 이상 드레인 전압에 의존하지 않고 일정하게 포화된다. 이는 장 채널에서는 핀치 오프 지점과 드레인 사이의 거리([그림 5-6]에서의 ∆L)가 전체 채널의 길이 대비 매우 짧으므로 게이트 전압에 의해 생성되어 이동하는 캐리어(전자)의 양은 거의 같고, 핀치 오프 지점과 드레인 사이에 걸리는 전압(VD - VDSAT)이 단순히 핀치 오프 지점까지 도달한 전자를 드레인 쪽으로 끌어당기는 역할만 하게 되어 전체 전류의 양이 일정하게 유지되기 때문이다.

이 영역에서 드레인 전류의 식은 선형 영역에서의 전류 식을 변형(VD = VG - VTh = VDSAT)하여 다음 식과 같이 나타낼 수 있으며, 전달 컨덕턴스(gm(sat.))도 구할 수 있다. 이 식을 통해 포화 영역에서의 드레인 전류(ID)는 게이트 전압(VG - VTh)의 제곱에 비례하여 증가함을 알 수 있다.

3 소자 축소(Scale-down)의 영향

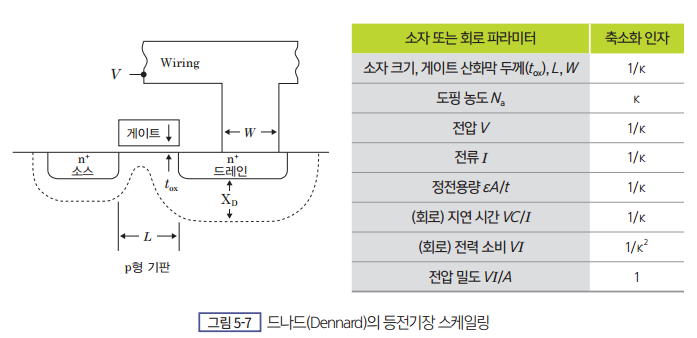

Texas instruments의 엔지니어인 잭 킬비(Jack Kilby)가 1959년에 집적회로를 발명한 이후, 반도체는 눈부신 발전을 거듭해 왔다. 그 후 1965년에는 페어 차일드의 연구원으로 있던 고든 무어(Gordon Moore)가 ‘반도체 칩의 밀도가 매 2년마다 2배로 늘어난다’는 실험적인 법칙을 발표하였고, 이는 장래 반도체의 성능 향상을 예측할 수 있는 기준으로 사용되어 왔다. 이렇게 반도체 칩의 집적도를 올리기 위해 트랜지스터의 축소화(Scale-down)가 꾸준히 진행되고 있으며, 덕분에 집적도의 증가뿐만 아니라 트랜지스터의 저 전력화와 고속화도 이룰 수 있었다. 이러한 소자의 축소화를 합리적으로 달성할 수 있는 등전기장 스케일링(Constant field scaling) 이론이 1974년 IBM의 드나드(Dennard)에 의해 트랜지스터 수준에서 제시되었다. 그 내용은 [그림 5-7]과 같이 채널(게이트) 길이의 감소에 따라 관련되는 다양한 항목들도 이에 비례하여 축소시키면 트랜지스터 내부의 전계가 그대로 유지된 채로 집적도와 성능의 향상이 가능하다는 것이다. 그러나 반도체를 수급하는 시스템 업체 입장에서 서로 다른 부품들의 전원 전압이 동시에 감소하지 않기 때문에 전원 전압의 축소가 쉽지 않다. 따라서 트랜지스터는 축소되었으나 전원 전압이 축소되지 않아 내부의 수직, 수평 전계가 증가하고 이로부터 단 채널 효과(Short channel effect) 문제가 발생하게 되는 것이다.

한편 채널 길이가 소스 및 드레인 접합의 공핍 영역 폭에 비견될 수 있을 만큼 작아졌을 때 MOSFET의 소자 축소 효과가 발생한다. 이러한 소자 축소 효과를 광의적으로 단 채널 효과(Short Channel Effect)라 한다. 단 채널 효과에는 문턱 전압 저감 현상(VTh roll-off), 드레인 전압에 의한 장벽 저하(Drain induced barrier lowering), 캐리어의 속도 포화 현상(Velocity saturation), 열 전자 효과(Hot electron effect), 채널 길이 변조(Channel length modulation) 등의 다양한 문제들이 있다. 이 중 문턱 전압 저감 현상(VTh roll-off)을 협의적 의미의 단 채널 효과라고 정의하기도 한다.

(1) 문턱 전압 저감 현상(VTh roll-off)

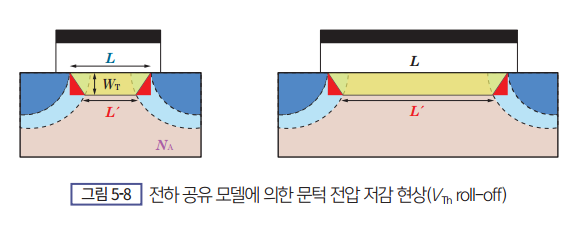

문턱 전압 저감 현상(VTh roll-off)은 상술한 바와 같이 협의적 의미의 단 채널 효과로, 게이트 길이가 짧아짐에 따라 문턱 전압이 낮아지는 현상을 말한다. 이는 MOS 커패시터 단원에서 살펴 본 문턱 전압식과 관련 있다. 구체적으로는 산화막에 걸리는 전압과 관련된 항목 Qd/Ci의 공핍층 전하(Qd)와 관련이 있다.

MOSFET의 채널 아래에 생기는 공핍 영역은 대부분 게이트 전압에 의해 만들어지지만, [그림 5-8]의 삼각형 영역은 소스와 드레인에 의해 만들어진 공핍 영역 전하의 영향을 받고 있다. 장 채널에서는 공핍 영역 전하에 대한 영향(삼각형 영역)이 전체 공핍 영역 전하량에 비해 무시할 수 있는 수준이지만, 채널의 길이가 감소함에 따라 공핍 영역 전하에 대한 영향이 상대적으로 더 커지게 되므로, 이를 무시할 수 없게 된다. 이러한 효과를 전하 공유(Charge sharing) 현상이라고 한다. 따라서 최대 공핍 영역을 형성하기 위해 산화막에 인가해 주는 게이트 전압이 줄어들고 이것이 바로 문턱 전압의 감소로 나타나는 것이다.

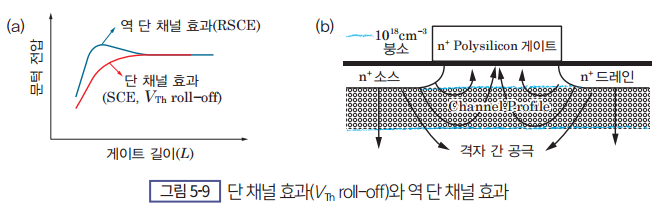

[그림 5-9]는 채널 길이에 따른 문턱 전압을 도시한 것이다. 그런데 채널 길이가 감소함에 따라 문턱 전압이 저하되는 단 채널 효과(VTh roll-off)와는 양상이 다르게, 어느 정도 채널 길이가 감소할 때까지는 오히려 문턱 전압이 증가하다 그 이후로 다시 감소하는 역 단 채널 효과 Reverse Short Channel Effect, RSCE)가 관찰되었다.

초기에는 이 현상의 원인이 후술할 ‘DIBL 또는 펀치 쓰루(Punch through) 현상의 억제를 위한 조치인, 후광(Halo) 이온 주입’의 효과라고 알려졌으나, 후광 이온 주입을 하지 않은 경우에도 동일 현상이 발견되었다. 그리고 그 원인은 다음과 같다. n+ 소스, 드레인의 이온 주입 시, 격자 간 공극(Interstitial)과 같은 결정 결함(Defect)을 막기 위해 고온 열처리(Anneal)가 진행되는데, 이 과정에서 [그림 5-9(b)]처럼 결함이 실리콘 내부로 급속하게 확산된다. 이에 따라 실리콘 기판에 있던 붕소(B)는 결정 결함을 따라 채널에 가까운 소스, 드레인 근처로 올라와 쌓이고, 이러한 붕소의 농도 증가 현상에 의해 역 단 채널 효과가 발생한다. 이 현상은 과도 증속 확산(Transient Enhanced Diffusion, TED)이라고 한다. 이 현상에 대해서는 이온 주입 공정 단원에서 상세 설명한다. 정리하자면, 일정 채널 길이까지의 감소는 과도 증속 확산의 영향으로 문턱 전압이 증가하지만, 그 이후에는 앞서 설명한 단 채널 효과(VTh roll-off)에 의해 문턱 전압이 다시 감소하게 되는 것이다.

(2) 문턱 전압 이하 누설 전류(Sub-threshold leakage current)

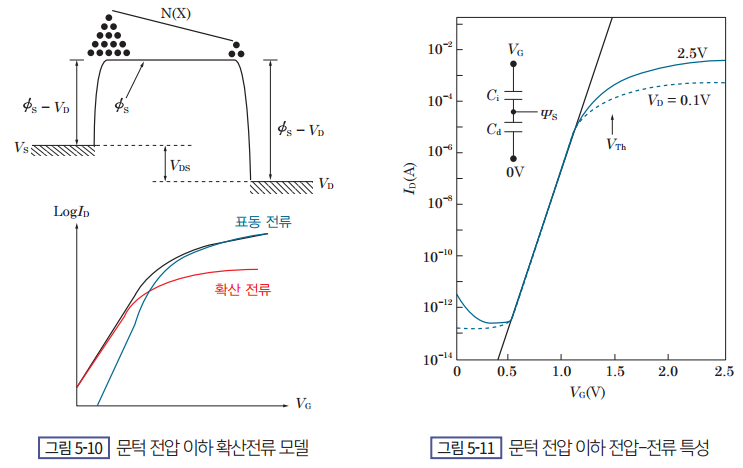

지금까지의 MOSFET은 문턱 전압 이하에서 드레인 전류가 전혀 흐르지 않는 이상적인 경우로 가정하여 설명하였다. 하지만 실제 MOSFET은 문턱 전압 이전(

(Cd: 공핍 영역 정전용량, VD: 드레인 전압)

지수 함수 항을 제외한 앞 부분은 주로 상수 항이고, 첫 번째 지수 함수 항은 드레인 전압이 q/kT 이상으로 조금만 올라가도 무시될 수 있다.4 마지막 지수 함수 항은 게이트 전압에 따라 확산 전류(ID)가 지수 함수적으로 증가함을 보여 준다. 이를 토대로 [그림 5-11]의 게이트 전압에 대한 로그 드레인 전류(logID)의 그래프는 선형적으로 그려진다.

장 채널에 한해 가능하며, 단 채널의 경우는 이후 설명할 드레인에 의한 전위 장벽 저하(Drain Induced Barrier Lowering, DIBL)라는 현상으로 드레인 전압의 함수가 됨.4

여기에서 잠깐, 중요한 변수 두 가지를 정의하려고 한다. 하나는 위 식에서 봤던 η 값이다. 우리가 게이트 전압을 변동시키는 것은, 실리콘 표면에서의 표면 전위(

위 식을 통해, η 값이 작을수록 게이트 전압으로 표면 전위를 잘 제어할 수 있음을 알 수 있다. 만약 공핍 영역에 의한 정전용량(Cd)이 0이고 게이트 산화막에 의한 정전용량(Ci)만 존재했을 때는 게이트에 인가한 모든 전압이 표면 전위가 될 것이다. 그러므로 게이트 전압만으로 표면 전위를 제어하기 위해서는, 가능한 한 산화막의 정전용량(Ci)을 크게 하거나 실리콘 공핍 영역에 의한 정전용량(Cd)을 최소화시킬 필요가 있다.

또 다른 중요한 변수 하나는 문턱 전압 이하의 기울기(Sub-threshold Swing, SS 또는 S-Factor)이다. 이는 다음 식과 같이 드레인 전류가 10배(로그 그래프상으로 1 오더(Order)) 변화하기 위해 게이트에 인가되는 전압의 변화량으로 정의한다. 이러한 정의는 [그림 5-11]에서 설명했듯이 문턱 전압 이하에서 로그 드레인 전류(logID) 값이 게이트 전압에 대해 선형적으로 변하기 때문에 가능한 것이다.

SS는 [그림 5-11] 그래프 기울기의 역수를 의미하며, SS 값이 작아질수록(기울기가 커질수록) 트랜지스터의 ON/OFF 특성이 좋아지면서 오프 전류(Off-current)도 개선된다. 이러한 현상은 단 채널 소자일수록 영향이 커진다. 따라서 SS 값을 감소시키기 위한 노력이 필요한데, 앞에서와 마찬가지로 공핍 영역에 의한 정전용량(Cd)의 최소화, 게이트 산화막에 의한 정전용량(Ci)의 최대화가 이루어져야 한다. 이때, 공핍 영역에 의한 정전용량(Cd)은 채널의 도핑 농도를 감소시켜 공핍 영역의 두께를 증가시킴으로써 줄일 수 있고, 게이트 산화막에 의한 정전용량(Ci)은 게이트 산화막의 두께를 감소시키거나 고 유전율의 절연막을 사용하는 방법으로 증가시킬 수 있다. 하지만 이러한 문턱 전압 제어는 심사숙고하여 진행할 필요가 있다. 문턱 전압을 너무 낮추면 오프 전류가 증가하고, 오프 전류의 감소를 위해 문턱 전압을 증가시키면 온 전류(On-current)가 감소하는 부작용이 발생하기 때문이다. 따라서 양자 간의 적절한 상호 보완이 필요하다.

앞의 SS에 대한 식(식 5-10)에서 상수 부분(2.3kT/q)은 실온에서 이론적으로 약 60mV의 값을 가진다. 하지만 불행히도, 효과적으로 잘 설계된 MOSFET조차 SS가 60mV/dec보다 조금 더 큰 값을 가지고 있다. 이론적으로 기존의 MOSFET이 60mV 이하의 SS을 갖는 것은 불가능하며, 60mV 이하의 SS을 갖는 소자의 구현을 위해서 터널링 전계효과 트랜지스터와 같은 새로운 개념의 소자 혹은 저온 동작 트랜지스터 등의 다양한 연구가 진행 중에 있다.

(3) 채널 길이 변조(Channel length modulation)

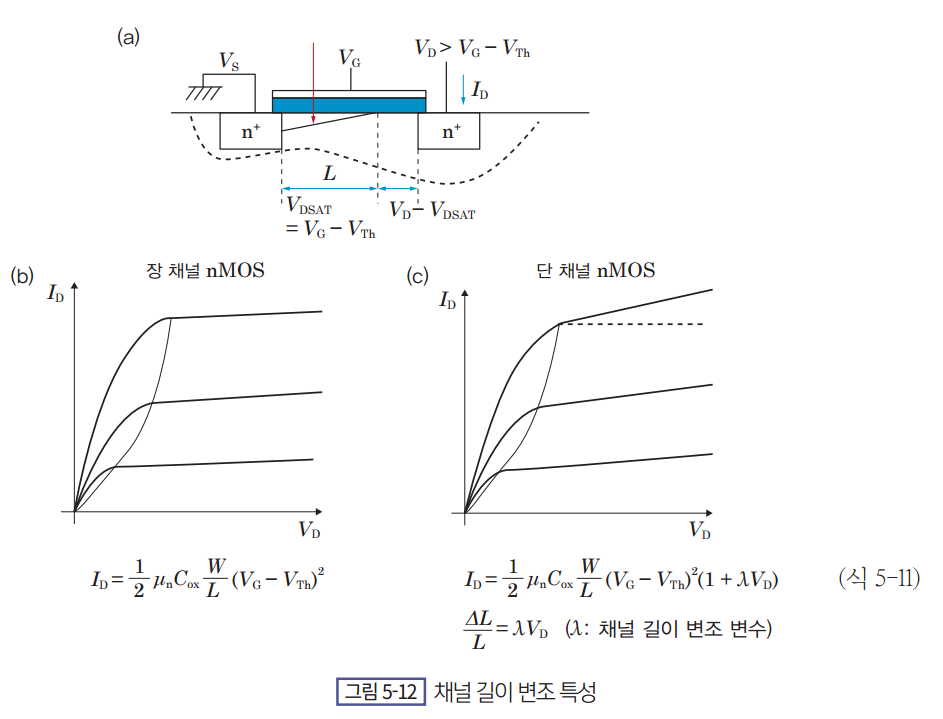

앞서 설명한 바와 같이 MOSFET은 3가지 영역(차단, 선형, 포화 영역)에서 동작한다. 이 중 포화 영역은 핀치 오프 현상으로 인해 드레인 전류가 드레인 전압과 무관하게 일정한 영역이다. 드레인 전압이 게이트 전압-문턱 전압 간 차이와 같아지면(VD = VG - VTh), 채널과 드레인이 만나는 지점에서 핀치 오프 현상이 발생한다.

[그림 5-12(a)]와 같이 드레인 전압이 증가하면, 핀치 오프 지점이 드레인에서 소스 쪽으로 이동하면서 트랜지스터의 유효 채널 길이가 감소하게 된다. 채널 길이의 감소는 포화 영역에서도 드레인 전류가 드레인 전압의 영향을 받게 만들고, 드레인 전압 증가에 따라 드레인 전류가 증가하는 채널 길이 변조(Channel length modulation) 현상을 불러일으킨다. 장 채널 소자에서는 이러한 현상이 큰 의미가 없지만, 단 채널 소자에서는 얘기가 달라진다. 드레인 전압의 변동에 따라 전류의 안정적인 공급에 문제를 초래할 수 있어 단 채널 소자에 적지 않은 영향을 미치기 때문이다.

[그림 5-12(b)]와 같은 장 채널 트랜지스터의 포화 영역 전류 식에, 드레인 전류가 채널 길이(L)에서 줄어든 채널 길이(ΔL)에 반비례한다는 의미의 관계식(ID∝1/(L - ΔL))을 대입하면, [그림 5-12(c)]의 하단 식(식 5-11)을 유도할 수 있다. 이 식은 채널 길이 변조의 영향으로 드레인 전압이 증가함에 따라 드레인 전류가 증가함을 나타내며, 여기서 λ는 채널 길이 변조 변수(Channel length modulation parameter)이다. MOSFET 제조 공정에서는 기판의 불순물 도핑 농도를 높여 채널 길이 변조 변수(λ)가 작은 값을 갖도록 하고 있다.

(4) 드레인 전압에 의한 장벽 저하(Drain Induced Barrier Lowering, DIBL)

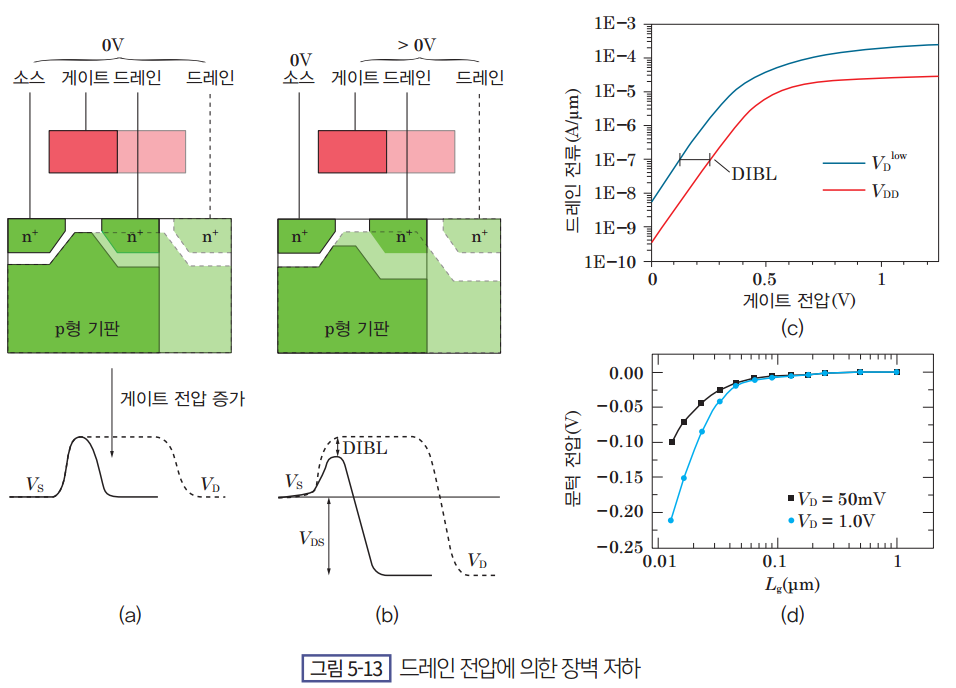

드레인 전압에 의한 장벽 저하 효과는 소스에서 드레인 쪽으로의 전자 이동을 위해 넘어야 하는 내부 전위 장벽의 모양에 의존한다. [그림 5-13(a)]와 같이 드레인 전압(VD) 및 게이트 전압(VG)이 0V인 경우에는, 소스에서 드레인 쪽으로의 전자 흐름을 막는 내부 전위 장벽이 존재하는데 이상적으로 게이트 전압은 전자의 이동을 위해 내부 전위 장벽을 낮추는 유일한 전압이어야 한다.

[그림 5-13(b)]와 같이 채널이 짧아지고 드레인 전압(VD)이 증가하게 되면, 공핍 영역이 소스와 채널 사이의 전위 장벽에 영향을 미치는 지점까지 확장된다. 궁극적으로 게이트 전압이 아닌 드레인 전압에 의해 채널과 소스 간의 내부 전위 장벽이 낮아지고, 이로 인해 [그림 5-13(c)]와 같이 누설되는 드레인 전류가 증가하는 현상이 발생한다. 이 현상을 드레인 전압에 의한 장벽 저하(Drain Induced Barrier Lowering, DIBL)라 부르며, 다음과 같이 표현할 수 있다.

(

채널 길이에 따른 문턱 전압을 도시한 [그림 5-13(d)]에서 드레인 전압이 높을 경우 문턱 전압의 감소가 심해짐을 알 수 있다.

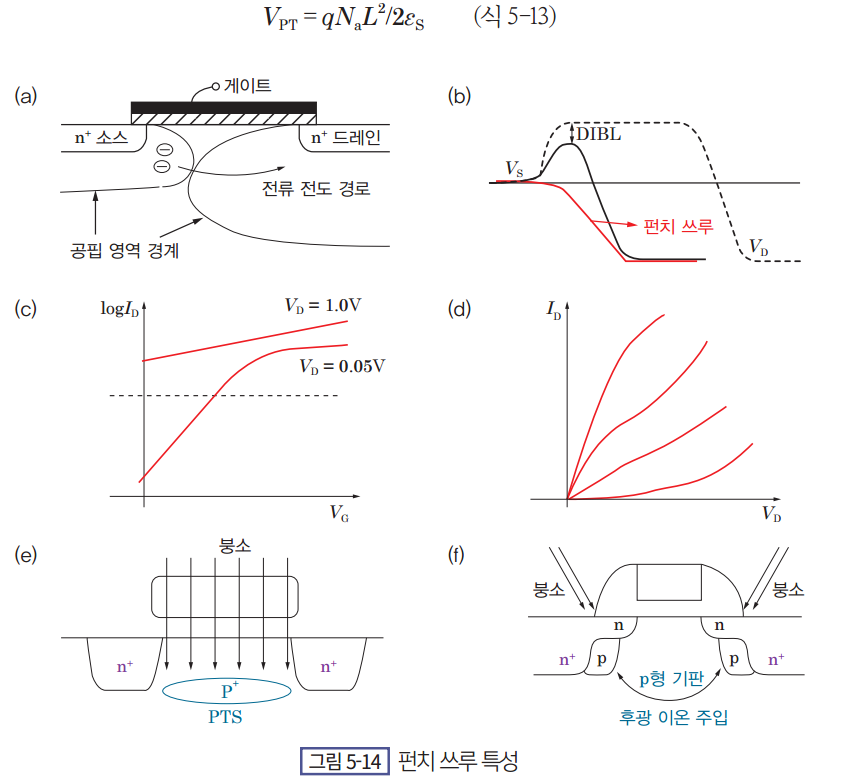

(5) 펀치 쓰루(Punch-Through) 현상

[그림 5-14(a)] 및 [그림 5-14(b)]와 같이, 드레인 전압 인가 시에 드레인 접합 공핍 영역이 소스 접합 공핍 영역과 만나 게이트의 제어를 전혀 받지 못하는 영역이 생긴다. 그렇게 되면 실리콘 표면이 아닌 하부에 전류 전도 경로가 형성되어 드레인에서 소스 쪽으로 큰 전류가 흐르는 펀치 쓰루(PunchThrough)현상이 발생한다. 앞서 설명한 DIBL 현상이 심화된 경우로 볼 수 있으며, 펀치 쓰루 현상이 일어나는 전압은 다음과 같이 기판 농도와 채널 길이의 함수로 표현할 수 있다.

펀치 쓰루 현상의 대책으로는 소스, 드레인 접합 깊이(Junction depth, Xj)의 감소와 펀치 쓰루가 발생하는 깊이에서의 기판 농도 증가 등의 방법이 있다. 이 중 기판 농도 증가를 위해, [그림 5-14(e)]와 같이 적정 깊이를 목표로 전체적으로 도핑 농도를 증가시키는 펀치 쓰루 방지 이온 주입(Punch Through Stop ion implant, PTS)이 사용됐다. 하지만 이 경우에는 기판 바이어스 효과 및 접합 정전용량의 문제가 있었고, 이를 개선하기 위해 나온 것이 바로 후광 이온 주입(Halo ion implantation) 방법이다. 드레인 전압이 증가하면, 소스와 드레인 접합의 아래 모서리에 있는 공핍 영역이 확장되는데, [그림 5-14(f)]와 같이 후광 이온 주입은 이 영역의 농도만을 올리는 방법이다.

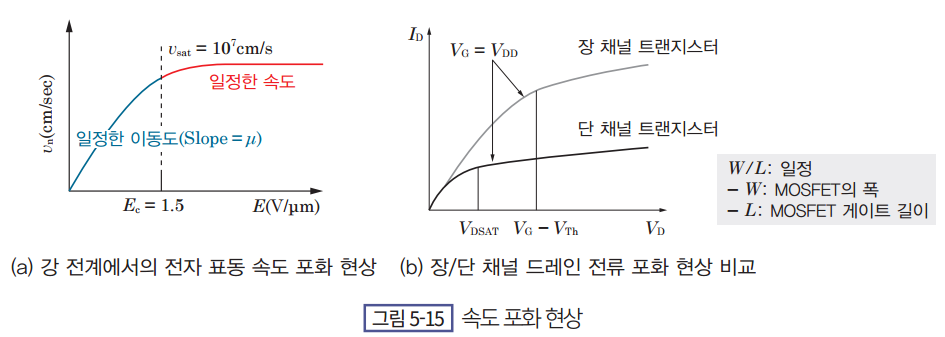

(6) 속도 포화 현상(Velocity saturation)

반도체 기초 Ⅱ단원에서 설명했듯이, 캐리어의 속도는 [그림 5-15(a)]와 같이 강 전계하에서 전계에 비례(v = με)하다가, 강 전계(> 103V/cm)가 되면 캐리어의 평균 열적 속도(vsat, 전자의 경우, 107cm/s) 부근에서 포화되는 모습을 보인다. 이는 전계에 의해 열적 속도 이상의 에너지가 추가 전달됐을 때, 추가된 에너지가 캐리어의 속도 증가에 기여하지 못하고 실리콘 격자 내로 전달되었기 때문이라고 설명하였다.5

광학 포논 산란(Optical phonon scattering)의 효과로 해석5

속도 포화 현상은 단 채널 트랜지스터에서 크게 나타나는데, 이는 채널 길이가 짧아져 소스/드레인 사이의 전계가 강해졌기 때문에 낮은 드레인 전압에서 속도 포화가 일어나게 되는 것이다. 따라서 [그림 5-15(b)]와 같이 단 채널에서는 핀치 오프에 의한 것보다 캐리어의 속도 포화에 의해 더 낮은 드레인 전압에서 전류 포화가 일어난다.

장 채널에서는 게이트 전압의 증가에 따라 게이트 전압의 제곱에 비례(

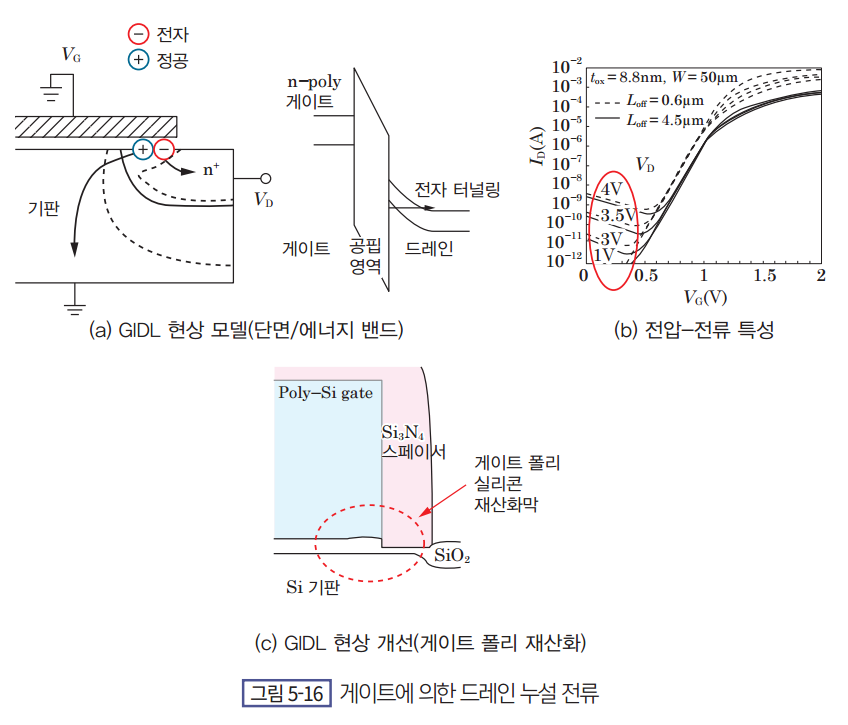

(7) 게이트에 의한 드레인 누설 전류(Gate Induced Drain Leakage, GIDL)

OFF 상태의 MOSFET에서 게이트와 드레인 간의 전압 차이가 큰 경우를 살펴보자. 이는 nMOS기준으로 봤을 때, 게이트 전압에는 0V 또는 음의 전압이 인가되고6, 드레인에는 양의 전압이 걸리는 상황에 해당한다. 이 경우에 게이트와 드레인이 서로 중첩되는 드레인의 표면에는 양단 간의 강한 전계로 인해 전자가 표면으로부터 밀려나게 되고, 그 공간에 공핍 영역(Deep depletion)이 생성된다. 드레인 영역은 저항을 낮추기 위해 고농도로 도핑되므로, 공핍 영역의 두께가 매우 얇다.

오프 전류(Off-current) 제어를 위한 목적임.6

이러한 조건 속에서 GIDL이 일어나는 원리는 이렇다. 먼저 드레인에 양의 전압을 인가함으로써, [그림 5-16(a)]와 같이 페르미 준위가 내려가고 드레인 표면에서의 에너지 밴드가 아래로 휘게 된다. 그 결과 가전자대의 전자가 얇아진 밴드를 터널링7하여 전도대로 이동할 수 있는 환경이 조성된다. 이후 전도대로 이동한 전자는 양전압이 인가된 드레인으로 이동하고 가전자대에 생성된 정공은 가장 전위가 낮은 기판으로 이동하여, [그림 5-16(b)]와 같이 드레인에서 기판으로의 누설 전류가 생기게 되는 것이다. 이 현상을 게이트에 의한 드레인 누설 전류(Gate Induced Drain Leakage, GIDL)라고 한다.

터널링7: 에너지 장벽이 강한 전계에 의해 기울어지면, 가전자대와 전도대 간의 거리가 가까워져 캐리어가 에너지 장벽을 뚫고 통과할 수 있는 양자역학적 현상

GIDL 현상은 채널 길이에 대한 의존성은 크지 않지만, 대기 전류를 증가시키고, 차단 영역에서 MOSFET의 누설 전류를 일으키는 주된 요인으로 작용한다. 따라서 DRAM과 같은 메모리 소자의 셀 트랜지스터에 있어 접합 누설 전류에 의한 리프레시(Refresh) 특성 문제로 작용할 수 있으므로 개선이 필요하다. 이를 개선하기 위해 다음과 같은 방법이 사용된다.

PN 접합 시 드레인의 농도를 경사지게(Graded junction) 형성시키는 방법

게이트 폴리 재산화(Gate poly re-oxidation): 게이트 식각 후 얇은 산화막을 성장시키고, 게이트 양 끝단의 산화막 두께 증가에 의해 전계를 완화시키는 방법([그림 5-16(c)] 참조)

(8) 열 전자 효과(Hot electron effect)

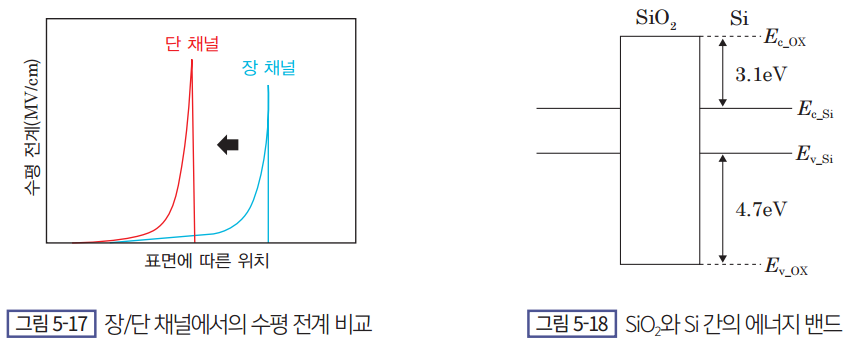

[그림 5-17]과 같이, MOSFET의 채널 길이가 짧아짐에 따라 채널 방향의 전계가 강해지는데, 이때 채널 내 전계 분포는 핀치 오프가 생기는 드레인 근처에서 최대치를 보이게 된다.

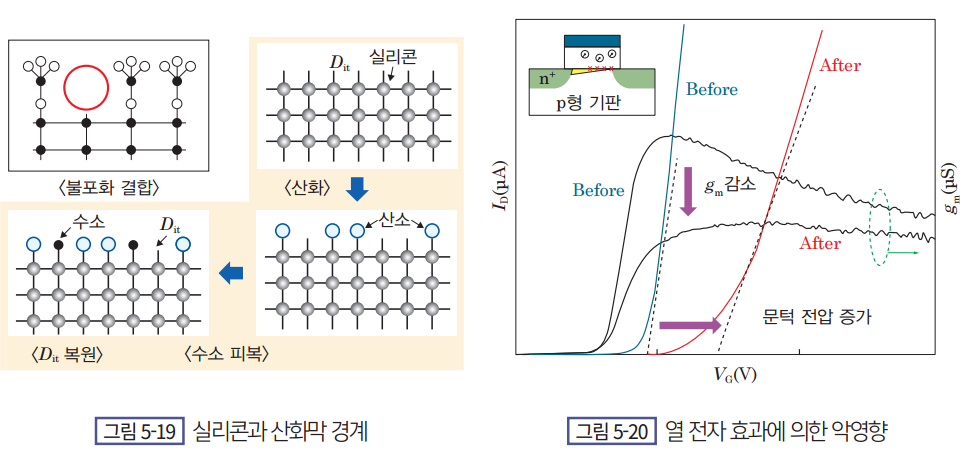

이러한 강한 전계 내에서 전자는 소스에서 드레인 쪽으로 움직이면서 높은 에너지를 받게 되고, 이 전자를 열 전자(Hot electron)라 한다. 그런데 만약 [그림 5-18]의 경우처럼, 전자가 실리콘(

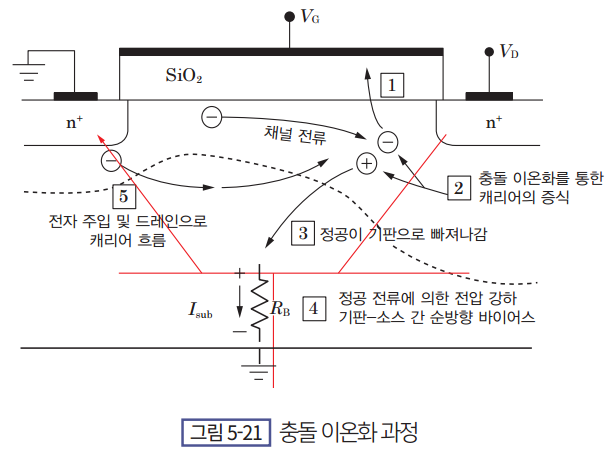

이 외에도 강한 에너지를 가진 열 전자는 [그림 5-21]과 같이 실리콘 격자와 충돌하여 실리콘 원자를 이온화시키고 전자-정공 쌍을 생성시키는 충돌 이온화(Impact ionization)를 일으킨다. 이렇게 생성된 전자-정공 쌍의 전자는 에너지를 받아 다시 열 전자가 되고, 실리콘 격자와 충돌하여 또 다른 전자-정공 쌍을 만들어 낸다. 이 과정이 반복되면서 전자와 정공이 대량 생성되고, 만들어진 전자-정공 쌍 중 전자는 양전압이 인가되어 있는 드레인으로, 정공은 기판으로 빠져 나가면서 기판 전류(Isub)를 형성한다(소스 쪽으로는 PN 접합 내부 전위 때문에 이동이 어렵다). 이때 형성된 기판 전류는 저항으로 인해 기판 내에 전위차를 발생시킨다. 이로써 0V로 접지되어 있는 소스보다 기판의 전위가 더 높아져 소스와 기판이 순방향인 PN 접합 조건이 되고, 역방향으로 바이어스되어 있는 기판과 드레인이 맞물려 기생 바이폴라 트랜지스터 동작을 하게 되어 스냅 백(Snap-back)8 및 CMOS 래치 업(Latch-up)9 등의 의도하지 않은 많은 전류가 흐르는 불량을 초래한다. 이와 같은 현상을 통틀어 열 캐리어 효과(Hot Carrier Effect, HCE)라고 한다.

스냅 백8: 드레인 전류가 정상적으로 흐르다 갑자기 증가하는 현상

래치 업9: 집적회로(IC)에서 내부 접합부 일부가 도통(전류가 흐르는 상태)되어 집적회로에 순간적으로 과전류가 흘러 파괴에 이르는 현상

한편, 캐리어 중 정공은 전자에 비해 이동도가 낮아 열 정공 발생 확률도 낮고 실리콘과 실리콘 산화막 간의 가전자대 에너지 차이가 4.7eV로 전도대역보다 커([그림 5-18] 참조) 큰 문제가 되지 않았으나, 최근 들어 소자의 미세화가 거듭됨에 따라 p채널 MOSFET에서의 열 정공 효과에 대한 연구 및 대책들이 나오고 있다.

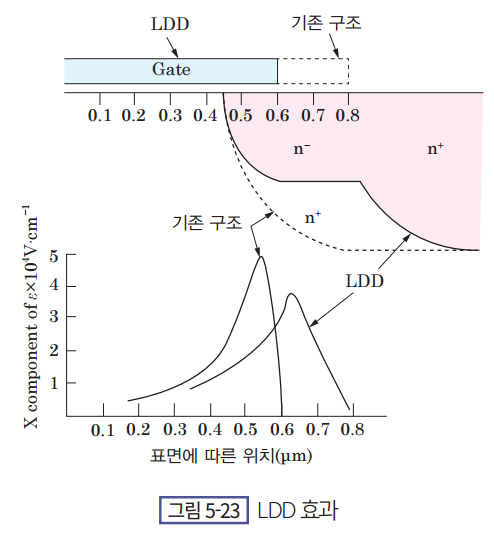

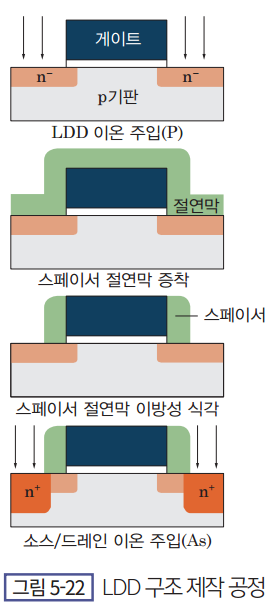

여기에서 잠깐, 열 캐리어 효과(HCE)에 대한 여러 대책 중에서 가장 효율적이고 널리 사용되는 방법인 저 농도 도핑 드레인(Lightly Doped Drain, LDD) 기술에 대해 소개하겠다. 먼저 제작 공정에 대해 설명하면, [그림 5-22]와 같이 게이트를 패터닝한 후 인(P)과 같은 V족 원소를 저농도 도즈(1013~1014/cm2)로 이온 주입한다. 그 후 산화막 또는 질화막 등의 절연막을 증착하고 이방성10 건식 식각을 통해 스페이서11를 형성한다. 그 후 소스와 드레인의 형성을 위해 고농도(~1015/cm2)의 비소(As) 등 V족 원소를 이온 주입함으로써 LDD 구조를 형성할 수 있다.

이방성10: 물체의 물리적 성질이 방향에 따라 다른 성질로, 방향에 따라 공정 진행 정도가 다름을 의미. 상세 내용은 식각 공정 단원 참고

스페이서11: [그림 5-22]에서와 같이 게이트 측면에 절연막(산화막 또는 질화막)을 붙인 것. 실리콘 기판에 도펀트(Dopant)를 주입하는 과정에서 스페이서 아래에 이온 주입이 되지 않도록 하기 위함임.

LDD는 [그림 5-23]과 같이 LDD를 적용하지 않은 기존 구조에서 전계가 가장 강한 드레인 부근의 드레인 도핑 농도를 감소시키는 것이다. LDD를 적용한 구조에서 드레인에 양의 전압이 인가되면 도핑 농도가 낮아진 LDD 영역은 공핍 영역의 폭이 커지고, 이에 따라 전계도 LDD가 끝나는 영역까지 확장된다. 인가한 드레인 전압은 LDD를 적용하지 않은 기존 구조와 동일하고, 전계를 적분한(전계 곡선의 하부 면적) 값이 같아야 하므로 LDD를 적용한 경우의 최대 전계는 낮아져야 한다. 충돌 이온화(Impact ionization)는 최대 전계에 대해 지수 함수적으로 증가하므로 열 전자 효과에 대한 최대 전계의 감소 효과는 매우 탁월하다. 그러나 LDD 영역은 기존 n+ 고농도 영역 대비 저농도이므로 소스/드레인 직렬 저항이 증가하는 부작용이 있어, ON 전류의 감소가 불가피하다. 따라서 LDD 이온 주입 공정은 열 전자 효과에 있어 전계 완화에 의한 소자 신뢰성 개선과 ON 전류 감소에 따른 소자 스피드 저하 문제, 이 양자 사이의 타협점을 찾아 적정 조건을 찾는 것이 중요하다.

심화개념 |

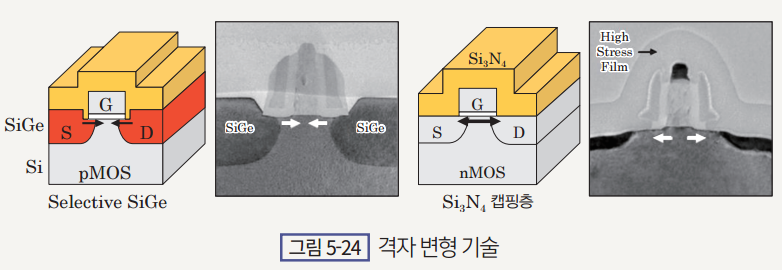

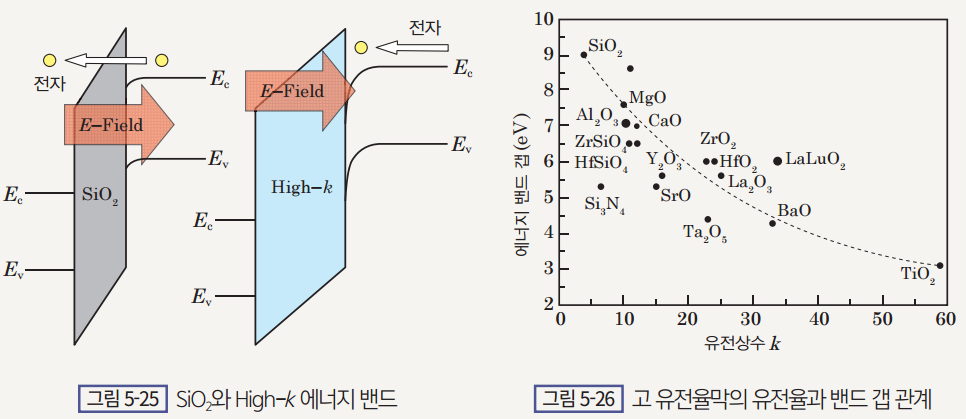

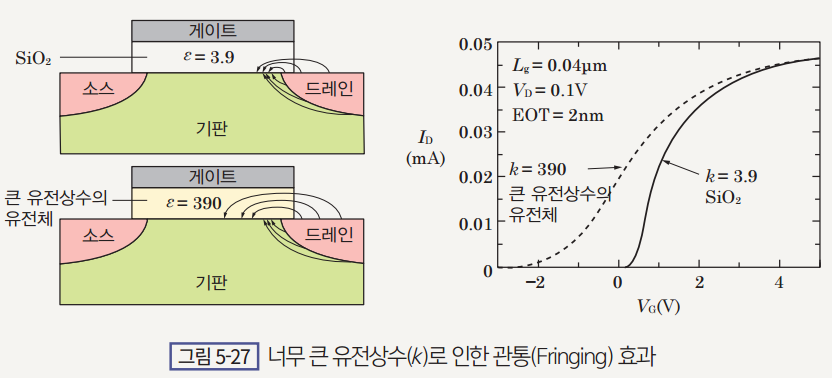

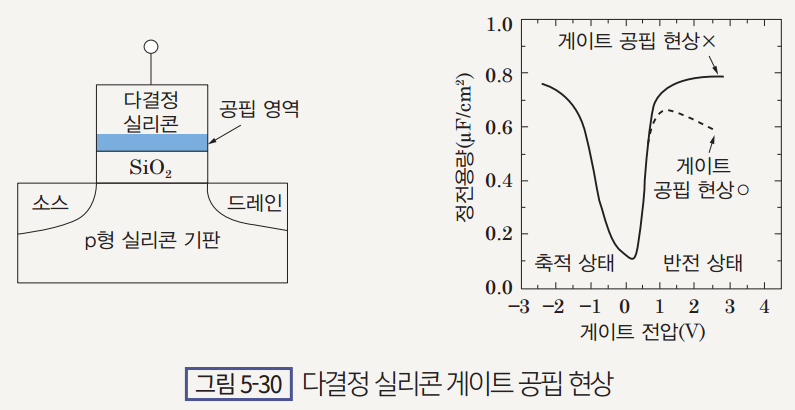

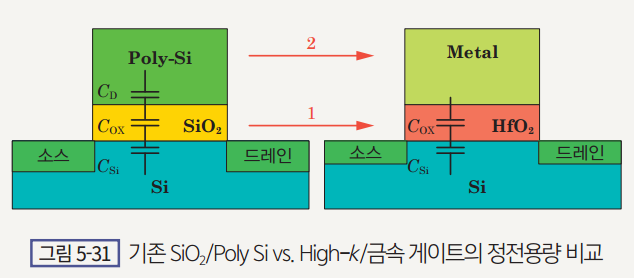

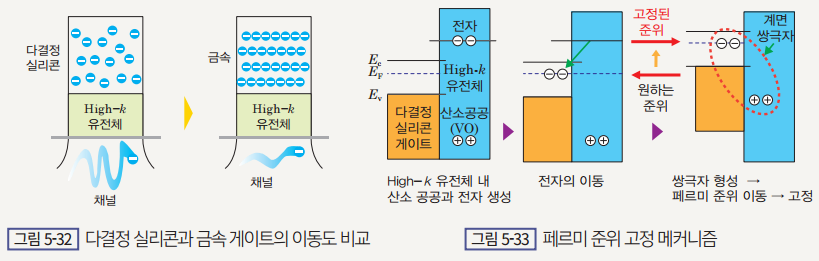

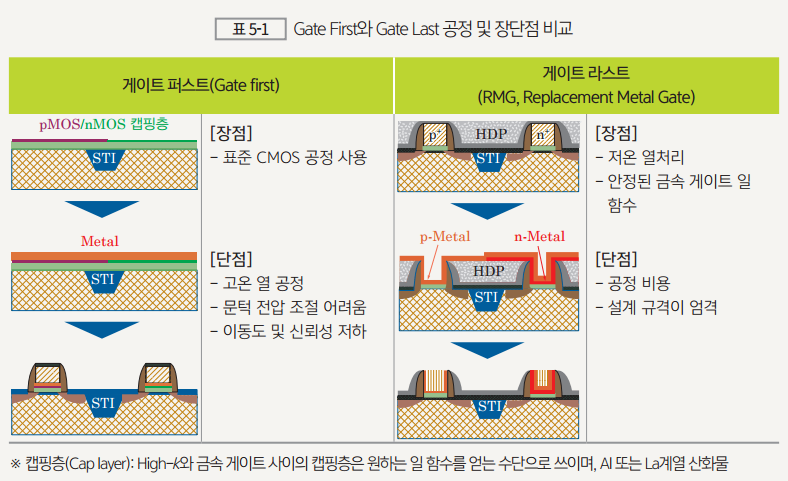

4 최신 MOSFET 소자소자가 축소(Scale-down)됨에 따라, 앞에서 살펴본 여러 가지 부정적인 현상들이 나타나게 되었고, 기존 기술 수준에서의 다양한 대책들이 제안되고 사용되어 왔다. 하지만 곧 한계에 봉착하여 완전히 새로운 구조 및 소재의 MOSFET이 등장하게 되었다. 이번 절에서는 몇 가지 대표적인 최신 소자 기술에 대해 소개하고자 한다. 이러한 신규 소자들은 우선 로직 제품에 적용되고 있지만, 점차 메모리 제품의 소자로도 확장되고 있는 추세이다. (1) 격자 변형(Strained silicon) 기술 (이동도 촉진제(Booster)) 앞 절에서 설명했듯이, 단 채널 MOSFET에서는 이동도 저하 현상이 발생하고, 이로 인해 ON전류(On-current) 감소가 생긴다고 했다. 이에 대한 대책으로는 채널에 이동도가 큰 얇은 게르마늄 막을 사용하는 방법과, 채널에 기계적 변형을 주는 변형 실리콘을 사용하는 방법이 있다. 이 중 두 번째 방법을 이용한 격자 변형 기술에 대해 알아보자. 실리콘에 기계적 응력(Stress)을 가하면 전자와 정공의 이동도가 변한다는 변형 전위(Deformation potential) 이론에 따라, 격자 변형 실리콘의 에너지 밴드 갭과 캐리어의 유효 질량은 일반 실리콘과 다른 값을 갖게 된다. 이는 곧, 이동도의 개선을 위해 캐리어의 유효 질량을 줄이거나 캐리어를 유효 질량이 좋은 곳으로 이동시키는 것을 의미한다. 전자는 인장 응력(Tensile stress)에 의해, 그리고 정공은 압축 응력(Compressive stress)에 의해 이동도가 증가한다는 사실은 이론 및 실험으로 증명되었다. 격자 변형 기술은 다양한 수단을 사용해 실리콘 결정을 물리적으로 인장 또는 압축하는 기술이며, 변형을 통해 캐리어의 이동성을 증가시켜 트랜지스터의 성능을 향상시킨다. 예를 들어, 채널에 압축 응력을 가하면 pMOS의 정공 이동도가 개선된다. 이렇게 실리콘 채널에 압축 변형을 만들기 위해서는, 소스 및 드레인 영역이 에피택시 성장12에 의해 실리콘(Si)-게르마늄(Ge)막으로 채워져야 한다. 실리콘(Si)-게르마늄(Ge)막은 전형적으로 20%의 게르마늄과 80%의 실리콘 혼합물로 구성된다. 실리콘(Si)-게르마늄(Ge)의 단위 체적당 원자 수는 원래의 실리콘 원자와 동일하지만 게르마늄 원자가 실리콘 원자보다 더 크기 때문에, 이로 인해 압축 응력이 발생하면서 채널을 미는 작용으로 정공의 이동도를 높일 수 있다. 에피택시 성장12: 웨이퍼 위에 일정한 방향성의 단결정을 성장시키는 방법. 단결정 실리콘을 씨앗층(Seed)으로 하여 손상된 실리콘층의 결정성을 회복시킴. (2) 고 유전율 금속 게이트 MOSFET(HKMG MOSFET) 앞서 문턱 전압 이하 특성에서 살펴본 바와 같이, 단 채널 효과를 줄이기 위해서는 게이트 절연막의 두께를 줄일 필요가 있다. 이로서 채널에 대한 게이트의 제어 능력을 개선하는 것이다. 그러나 [그림 5-25]와 같이 30Å 이하로 게이트 절연막( [그림 5-26]에 도시한 바와 같이 통상 High-k 유전체는 실리콘 산화막( 일반적으로 MOSFET에 적용되는 High-k 유전체는 10배 이상 큰 유전상수를 갖는 물질로 정의되며, 주기율표상 Ⅲ-Ⅴ족에 있는 란탄족(Lanthanide) 및 알루미늄의 전이 금속으로 구성된 금속 유전체(절연체) 부류를 지칭한다. 예를 들어, 산화 알루미늄(

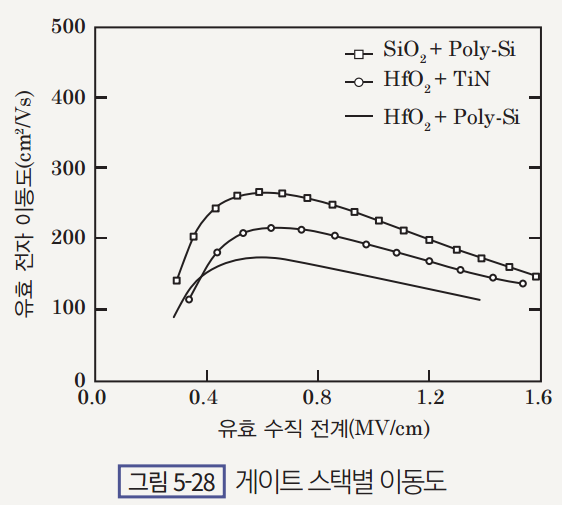

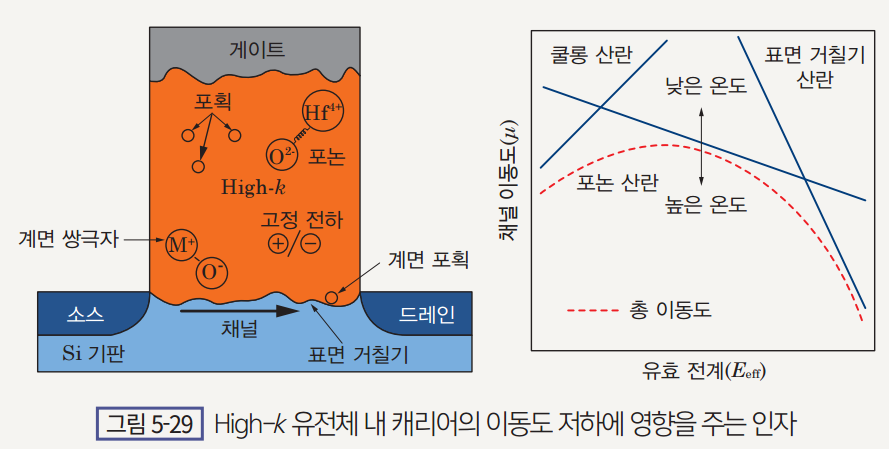

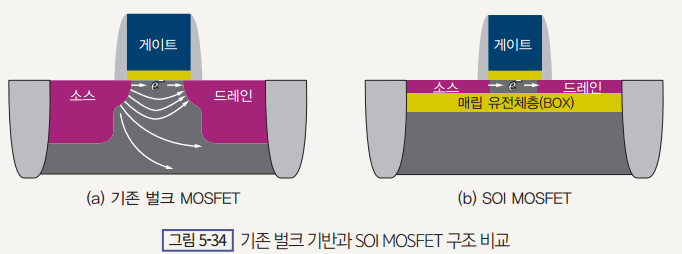

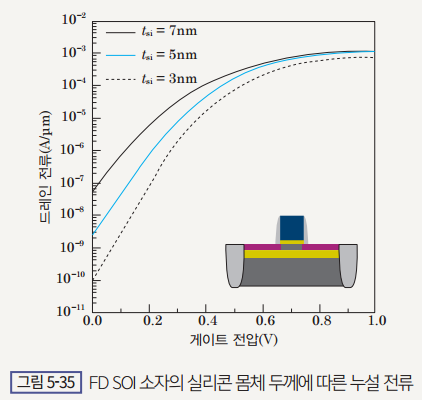

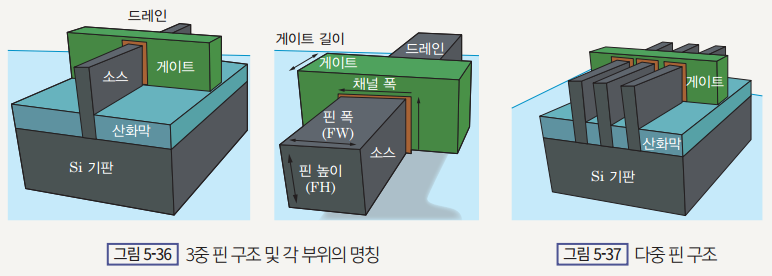

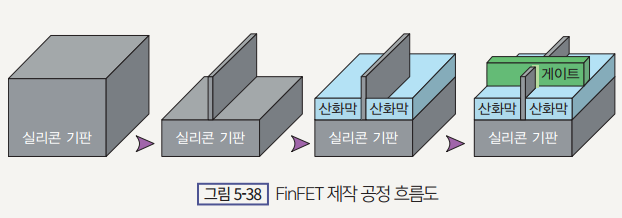

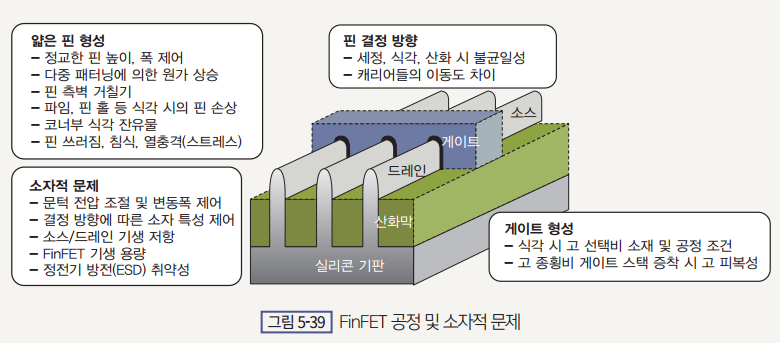

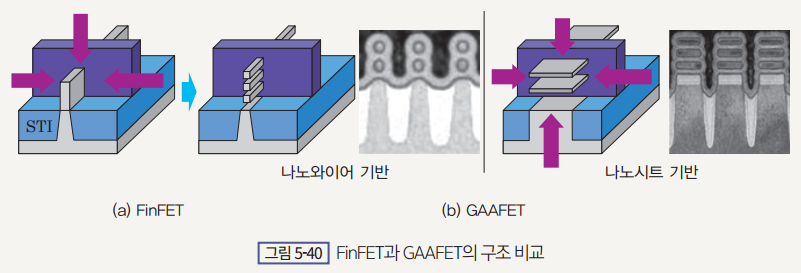

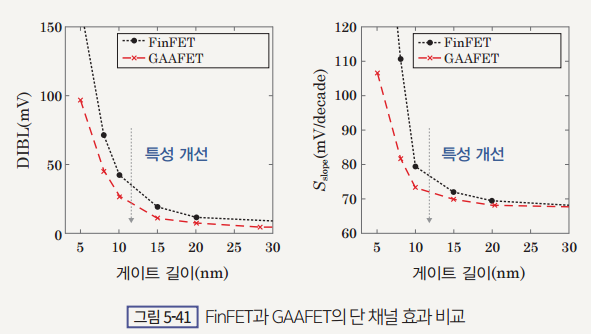

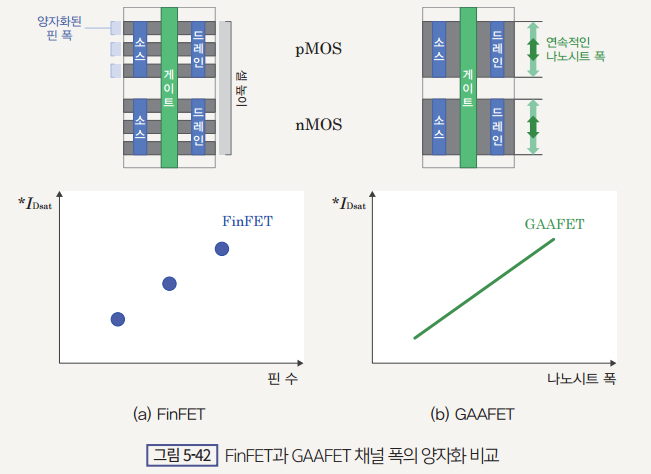

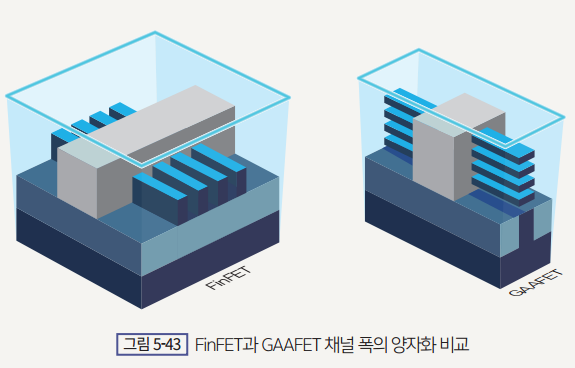

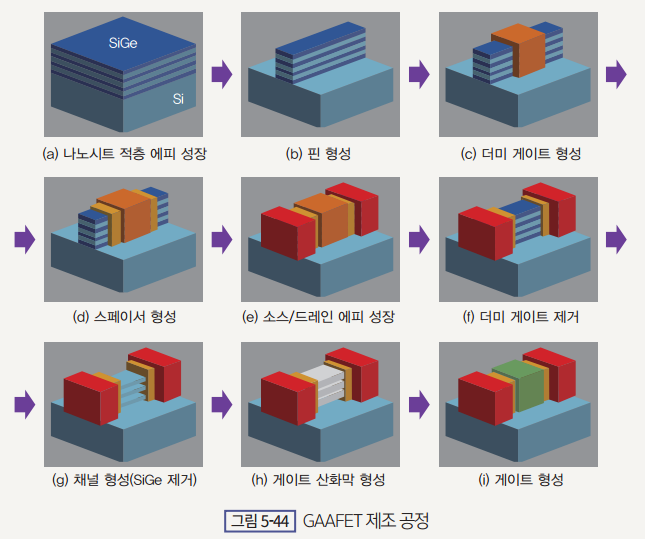

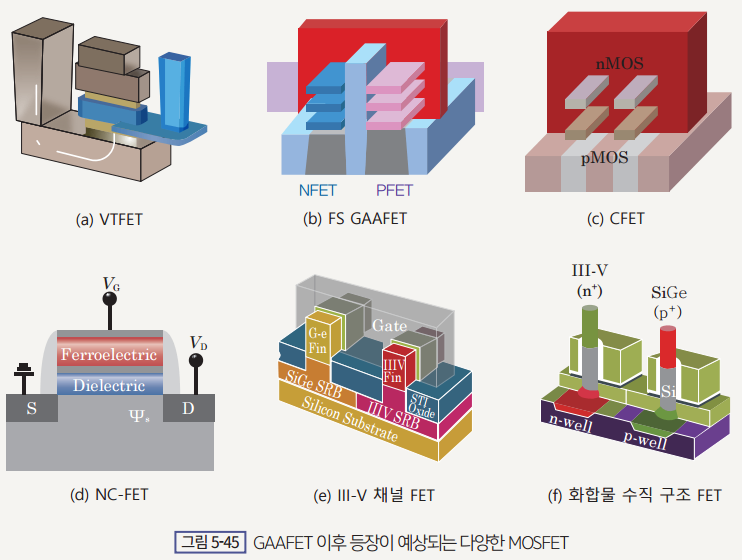

첫 번째 핵심 요구 사항은 유전상수(k)에 대한 내용으로, 금속 유전체의 적절한 유전상수(k)는 12이상 35 이하여야 한다. 그러나 [그림 5-27]과 같이 너무 큰 유전상수(k)를 가지면, 드레인에서 High-k유전체를 통한 측면 전계의 관통(Fringing)이 일어나므로, 오히려 게이트 제어성을 감소시켜 단 채널 효과가 가중될 가능성이 있다. 따라서 적정한 유전상수(k)와 두께를 가진 유전체를 선정해야 한다. High-k 물질의 증착 방법은 스퍼터링에 의한 물리 기상 증착(Physical Vapor Deposition, PVD) 및 화학 기상 증착(Chemical Vapor Deposition, CVD) 모두 가능하나, 최근에는 피복 능력(Step Coverage)과 정밀한 두께 제어가 가능한 원자층 증착(Atomic Layer Deposition, ALD) 방식을 많이 사용한다. 다음은 소자의 속도에 영향을 주는 이동도(Mobility)에 대해 논의해 보고자 한다. 반도체 기초 Ⅱ 단원에서 다뤘던 내용을 다시 상기해 보면, 이러한 캐리어의 이동도는 [그림 5-28]과 같이 High-k/Si 계면( 광학 포논13: 결정 내 원자들의 집합적인 진동(격자 진동)을 포논(Phonon)이라 하고, 격자 산란을 포논 산란(Phonon scattering)이라고도 함. 다음은 게이트 전극 물질을 다결정 실리콘에서 금속으로 변경한 이유에 대해 알아보자. 첫 번째 이유는 다결정 실리콘 게이트의 공핍 현상 때문이다. nMOS의 경우 게이트에 양전압이 인가되면, 기판은 음전하를 띤 전극의 역할을 하게 되어 [그림 5-30]과 같이, n형으로 도핑된 다결정 실리콘 게이트의 하부를 수 Å공핍시키게 된다. 이를 다결정 실리콘 게이트 공핍(Polysilicon depletion)이라 하고, 이 현상은 앞서 설명한 관통(Fringing) 효과로 인해 단 채널 MOSFET에서 더 심각하게 나타난다. 따라서 총 정전용량은 [그림 5-31]의 좌측 그림과 같이 게이트 산화막의 정전용량( 이러한 유효 게이트 산화막 두께의 증가로 인한 구동 전류 열화 및 문턱 전압 이하 누설 전류(SS)와 같은 단 채널 효과 문제는 공핍 현상이 없는 금속 게이트로 대체하여 방지할 수 있다. [그림 5-31]은 실리콘 산화막( 금속 게이트로 전환하게 된 두 번째 이유는 앞 절에서 설명한 캐리어 이동도의 감소 때문이다. 포논 산란에 의한 이동도 감소는 다결정 실리콘과 High-k 유전체 간의 전기적 상호 작용으로 인해 발생하는 문제로, 다결정 실리콘 내의 전자 밀도가 낮아서 생기는 현상이기 때문에, [그림 5-32]와 같이 전자 밀도가 매우 높은 금속 게이트로 변경 시 개선이 가능하다. 금속 게이트로 전환하게 된 또 다른 이유는 MOSFET의 문턱 전압 제어의 어려움 때문이다. 앞서 설명한 High-k 유전체 내 많은 양의 고정 전하로 인해 발생하는 전하 포획 외에도 페르미 준위 고정(Fermi level pinning) 현상으로 인한 문턱 전압 이동(Shift)이 원인이다. [그림 5-33]과 같이, High-k 유전체 내에 결함에 의한 산소 공공(Oxygen vacancy)과 전자가 형성되고 이 전자가 다결정 실리콘 쪽으로 이동함으로써 계면 분극이 생긴다. 이에 따라 페르미 준위가 고 에너지 쪽으로 이동한다는 원리이다. 금속 전극 재료는 페르미 준위 고정 효과를 완화시킬 수 있고, 적절한 일 함수를 갖는 금속 물질을 선택하여 MOSFET의 문턱 전압을 비교적 용이하게 제어할 수도 있다. 이와 같이 High-k 절연체와 금속 게이트(Metal gate)를 사용함으로써 MOSFET의 성능을 대폭 개선한 기술을 HKMG라고 칭하게 되었다. 한편, High-k 유전체 금속 게이트에 대한 두 가지 상이한 공정 접근법이 대량 생산에서 구현되었다. 이는 게이트 퍼스트(Gate first) 및 게이트 라스트(Gate last)이며, 후자는 대체 금속 게이트(Replacement Metal Gate, RMG)법이라고도 한다. 게이트 퍼스트 기술에서는 완전한 게이트 스택이 게이트 패터닝 전에 형성되므로, 도펀트 활성화를 포함한 모든 후속 공정에서 높은 열 처리량(Thermal budget)을 견뎌야 한다. 이렇게 고온에 노출되면, 게이트 스택을 위한 재료 선택에도 제한이 생긴다. 게이트 라스트 접근법의 경우, 전통적인 S (3) 완전 공핍형 절연체 기반 실리콘 MOSFET(FD SOI FET) 앞 절에서 논의한 바와 같이 소자 축소(Scaling) 시에는 다양한 단 채널 효과가 문제가 되는데, 이를 개선하기 위한 최신 소자 기술 중 하나가 바로 SOI(Silicon On Insulator)라는 기술이다. 이 기술은 절연체 위에 단결정 실리콘을 형성하고 그 단결정 실리콘에 MOSFET을 제작하는 기술이다. [그림 5-34]와같이 기존 MOSFET 구조와 SOI MOSFET 구조 간의 주요 차이점은 SOI MOSFET에 매립 유전체층(Buried OXide layer, BOX)이 있어, 소자와 기판을 분리시켰다는 점이다. 2차원 SOI MOSFET의 제조 공정은 원재료인 실리콘 웨이퍼를 제외하고는 벌크(Bulk) MOSFET(기존 MOSFET) 공정과 유사하다. SOI 웨이퍼는 [그림 5-34(b)]와 같이 ① 트랜지스터가 형성되는 표면의 얇은 실리콘 몸체(Body)층, ② 하부 절연층(BOX), ③ 기판 실리콘 웨이퍼의 3개 층으로 구성된다. SOI MOSFET는 상부 실리콘 몸체층의 두께에 따라 부분 공핍형(Partially Depleted, PD) SOI과 완전 공핍형(Fully Depleted, FD) SOI로 분류된다. PD SOI와 비교하여, FD SOI는 매우 얇은 몸체 구조를 가지므로 동작 중에 몸체가 완전히 공핍된다. 이러한 FD SOI를 초박형 몸체(Ultra-Thin-Body, UTB) SOI라고도 한다. PD SOI의 경우에는 몸체의 두께가 50~90nm이며, 매립 유전체층(BOX)의 두께는 100~200nm 수준이다. 주로 마이크로 크기의 기계 부품이나 센서 소자인 MEMS(Micro-Electro Mechanical System, 미세 전기 기계 시스템) 또는 전력소자 등의 아날로그 제품에 응용된다. 웨이퍼 제작이 쉬워 가격이 저렴하다는 장점이 있는 반면, 부유 몸체 효과(Floating body effect)로 인해 단 채널 소자에 적용하기에는 한계가 있다. 부유 몸체 효과로 인한 문제점은 매우 다양하다. 이 중 하나가 히스토리(History) 효과인데, 이는 PD SOI에서 몸체가 두꺼워지면서 몸체가 부유(Floating) 상태가 되어, 몸체 전압이 소자의 이전 상태에 따라 달라지게 되는 현상이다. 또 다른 문제점은 킹크(Kink) 효과의 발생이다. 이는 부유 몸체 효과에 의해 몸체에 정공이 쌓여 OFF 상태 전류를 증가시키거나, 드레인 전류가 드레인 전압의 어느 시점부터 갑자기 증가하는 문제이다. 이에 반해 FD SOI 소자는 매립 유전체층(BOX) 두께가 5~50nm이고, 실리콘 몸체의 두께는 약 5~20nm로(통상 채널 길이의

우물 공정14: nMOS, pMOS가 형성될 적정 농도의 기판을 형성시키는 공정

SOI의 단점에는 부유 몸체 효과 외에 또 다른 문제인 자체 가열 특성이 있다. SOI 소자의 실리콘 몸체 박막은 금속 전극과 접촉되는 영역을 제외하면 우수한 단열재인 (4) 핀 전계효과 트랜지스터(Fin Field Effect Transistor, FinFET) 2011년 Intel은 세계 최초로 3차원 반도체 소자인 벌크 FinFET의 22nm 기술 양산화에 성공하였다. 32nm 2차원 소자 대비 동일 성능 기준, 50% 이상의 전력 소모 감소는 물론, 동일한 전압에서 37%의 성능 개선이 가능하다고 발표한 바 있다. Intel 발표 이후로 현재까지, FinFET은 첨단 로직 제품의 중요 소자로 자리매김하고 있는 상태이며 일부 DRAM 제품에도 변형 적용하고 있다. 기존의 2차원 MOSFET에서는 게이트가 채널 한 면에 접촉하여 제어하는 구조였지만 FinFET 기본 구조는 적어도 2개 이상의 채널 면이 게이트에 의해 제어되는 구조이며, 실리콘 몸체가 물고기의 등 지느러미(Fin)와 유사하다고 하여 FinFET이라는 이름이 붙여지게 되었다. FinFET 구조는 기판에 돌출된 얇은 수직 돌기(Fin, 핀)가 채널이 되고, 이 채널의 3면을 게이트가 둘러쌈으로써 채널 부분에 대한 게이트의 제어 능력(Controllability)을 향상시킬 수 있다. 덕분에 MOSFET 미세화에 따른 단 채널 효과(Short Channel Effects, SCE)를 줄이고, 문턱 전압(Threshold voltage) 이하에서의 누설 전류도 줄일 수 있다. FinFET의 구동 전류는 채널의 폭과 연관이 있는데 이때 채널의 폭은 핀(Fin)의 높이에 따라 결정된다. 채널 폭( 기존의 2차원 소자에서는 채널 폭을 변경하여 소자의 전류 구동 능력을 자유롭게 선택할 수 있었지만, FinFET의 경우에는 채널 폭이 항상 핀 수(Fin number)의 배수가 되기 때문에 임의의 채널 폭을 정의할 수 없는 문제가 있다. 이는 곧, 소자의 유효 폭이 양자화되는 결과를 가져온다. 이로 인해 FinFET의 셀 설계에서는 FinFET의 핀 피치(간격)가 매우 중요하다. [그림 5-37]과 같이 핀 피치가 좁아서 더 많은 핀을 일정한 폭으로 배치할 수 있다면, 핀의 폭을 결정할 때 그만큼 소자 설계의 자유도가 증가하게 되는 것이다. 기존의 MOSFET에서는 채널에 도펀트(불순물)를 주입하여 문턱 전압을 제어하고 단 채널 효과를 감소시켰으나, FD SOI 소자와 유사하게 FinFET은 이 같은 채널 도핑이 선택 사항이 되었다. FinFET구조상 게이트가 채널(핀)을 감싸고 핀 몸 자체가 얇아 기존 MOSFET 대비 단 채널 효과가 우수하기 때문이다. 즉, 채널 도핑을 낮게 하면 채널 내부의 캐리어 이동도가 높아져 더 우수한 성능의 구현이 가능하게 됨은 물론, 도펀트 수의 변동에 따른 문턱 전압의 균일도도 개선된다. [그림 5-38]은 FinFET 제조 공정의 흐름도이다. 먼저 포토 및 실리콘 기판에 대한 식각 공정을 통해 활성 영역(Active)인 핀을 형성하고 핀 간의 절연용 산화막을 증착한다. 이후 소자 격리 공정 STI(Shallow Trench Isolation) 형성을 위해 화학적 기계적 연마(CMP) 및 식각 공정(Etch back)을 거쳐 산화막을 원하는 두께만큼 핀 아래까지 내린 후 게이트 산화막 및 게이트 전극을 형성하는 단계로 구성된다. 이번에는 FinFET에서 해결해야 할 대표적인 소자 및 공정 문제들을 살펴보도록 하자. 핀을 이용한 구조이다 보니 핀 형성에 대한 문제가 가장 큰 비중을 차지한다. [그림 5-39]를 보면 먼저 핀의 두께가 얇아 소스 및 드레인의 기생 저항이 증가할 수 있다. 이 부분은 소스/드레인에 에피층15을 성장시켜 소스/드레인을 상승시킨(Elevated) 구조를 적용하고 있다. 또한 미세한 핀의 형성을 위해서는 다중 패터닝(Multi-patterning)과 같은 고비용의 공정이 필요하게 되는 문제점이 있다. 고 종횡비 구조로 인해 핀 또는 게이트의 코너에 있는 잔류물 식각 시 고 에너지의 이온에 의한 표면 손상을 방지하기 위해 우수한 식각 선택비도 요구된다. 또한 얇고 깨지기 쉬운 핀과 게이트 구조는 습식 세정 후 웨이퍼를 건조하는 동안 핀에 손상을 주지 않아야 한다. 핀 표면의 결정 방향이 상이하여, 공정적으로는 세정 및 식각 공정 시에 모서리와 면에서의 식각률 차이가 발생하거나, 열 산화 공정 시 위치별 성장률 차이로 인한 핀의 프로파일 및 특성에 이상을 초래할 수 있다. 이 부분에 대한 공정 및 소재 측면의 최적화가 필요하다. 이 외에도 정전기 방전(Electro Static Discharge, ESD) 및 기생 용량(Parasitic capacitance) 등에 문제가 있어 이에 대한 설계, 소자적인 대책이 연구되고 있다. 에피층15: 기판과 동일한 재료 또는 상이한 재료로 성장시킨 단결정 박막 (5) 게이트 올 어라운드 트랜지스터(Gate All Around Field Effect Transistor, GAAFET) FinFET의 등장으로 10nm 이하에서도 우수한 트랜지스터 특성을 확보할 수 있었으나 3nm 이하로 미세화가 진행됨에 따라 FinFET 또한 누설 전류 제어에 있어 한계에 봉착하게 되었고, 새로운 구조의 MOSFET의 등장이 절실해졌다. 이러한 요구에 부응하는 MOSFET이 바로 게이트 올 어라운드 트랜지스터(Gate All Around Field Effect Transistor, GAAFET)이다. 최초의 GAAFET은 1988년 도시바에서 선보인 수직 나노와이어(Vertical Nanowire) GAAFET이었으며 SGT(Surrounding Gate Transistor)라고 불렸다. GAAFET 기술은 기능면에서 FinFET 트랜지스터와 유사하지만 FinFET 트랜지스터가 채널의 3면에 게이트가 접촉하는데 반해, [그림 5-40]과 같이 게이트가 4면에서 채널을 둘러 싸는 구조라는 점에 차이가 있다. 이와 같이 기존 FinFET 대비 GAAFET는 나노와이어(Nanowire) 또는 나노시트(Nanosheet)로 형성된 채널의 4면을 게이트로 둘러 싸 채널 특성을 한층 더 잘 제어함으로써 미세화에 따른 우수한 단 채널 효과 및 누설 전류 제어 특성을 확보할 수 있게 되었다([그림 5-41] 참조). GAAFET은 채널의 모양에 따라 나노와이어 및 나노시트 구조로 나눌 수 있다. 나노와이어 기반의 GAAFET은 나노시트 구조 대비 최종 형성된 채녈의 단면 구조가 원형에 가까워 채널 내의 전계 집중 현상을 완화시킬 수 있다는 장점은 있으나, 제조 공정이 상대적으로 난해하고 채널의 폭이 좁아 충분한 구동 전류의 확보가 어렵다. 때문에 대부분의 소자 제조사들은 나노시트 구조를 채택하고 있다. FinFET 대비 GAAFET의 또 다른 장점은 [그림 5-42]를 통해 알 수 있다. 앞서 설명한 바와 같이, FinFET은 채널 폭 증가를 위해 핀 수를 증가시키는 경우, 소자의 유효 폭이 양자화되는 결과를 가져오지만, GAAFET은 나노시트의 폭 증가에 따라 연속적인 채널 폭 증가가 가능하여 설계의 자유도를 올릴 수 있다. 그 외에도 [그림 5-43]과 같이 적층하는 채널 수를 증가시킴으로써 더 좁은 평면적에서 동일 채널 폭의 확보가 가능하다는 장점이 있다. GAAFET는 이러한 장점들로 인해 기존 FinFET 대비 성능, 전력소모, 면적 측면에서 대폭적인 향상을 가져 왔지만, FinFET 대비 제조 공정이 복잡해진다는 문제가 있어 이에 대한 많은 연구 및 개발이 진행되고 있다. [그림 5-44]는 논문 등에 보고된 GAAFET의 제조 공정을 단순화하여 소개하고 있다. (a) (b) MOSFET이 형성될 활성화 영역을 패터닝한다. (c) 더미 게이트(Dummy gate)를 형성한다. (d) 추후 게이트와 소스/드레인을 분리시켜 줄 스페이서(Spacer)를 형성한다. (e) 에피택시 공정을 사용, 소스/드레인 영역을 형성한다. (f) 더미 게이트를 제거한다. (g) 채널 형성을 위해 습식 식각을 통해 실리콘 게르마늄( (h) 게이트 산화막을 증착한다. (i) 게이트 물질을 증착하고 패터닝한다. 에피택시 공정16: 기판과 동일한 재료 또는 상이한 재료의 단결정 박막을 성장시키는 공정 위와 같이 GAAFET 제조 공정은 에피택시 성장 공정, 실리콘 게르마늄( GAAFET의 후속이자, 2nm 노드 이후에 적용될 MOSFET 후보로는 [그림 5-45]와 같은 기술이 있다. GAAFET의 집적도를 높이기 위한 VTFET(Vertical Transport FET) 및 FS(Fork-Sheet) GAAFET, nMOS와 pMOS를 수직으로 배치한 상보(Complementary) FET(CFET), 60mV 이하의 문턱 전압 이하 스윙(SS)을 목표로 한 NC(Negative Capacitance)-FET, 고 이동도를 위한 III-V 채널 FinFET, 고 이동도 및 고 집적도를 목적으로 하는 화합물 수직 구조 FET 등 다양한 구조의 첨단 MOSFET들이 개발 중이다. |

기출문제로 정리하기 ※ 기출문제를 읽고 스스로 답변해 본 후, 이와 관련된 ‘이론 페이지’의 내용을 확인하여 자신의 답안과 비교합니다. | 이론 페이지 |

최신 기출 1 MOSFET의 동작 원리에 대해 설명하시오. | p.129 |

최신 기출 2 MOSFET의 미세화 시 문제점과 그 해결책에 대해 설명하시오. | p.134~147 |

최신 기출 3 MOSFET의 동작 속도를 개선할 수 있는 방안에 대해 설명하시오 | p.148~149 |

최신 기출 4 고 유전율 금속 게이트(High-k Metal Gate, HKMG)에 대해 설명하시오. | p.149~154 |

최신 기출 5 FinFET과 GAAFET에 대해 설명하시오. | p.157~162 |

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기