무어의 법칙이란 무엇입니까? 그 법칙은 현재 잘 지켜지고 있습니까?

[무어의 법칙(Moore's Law)]

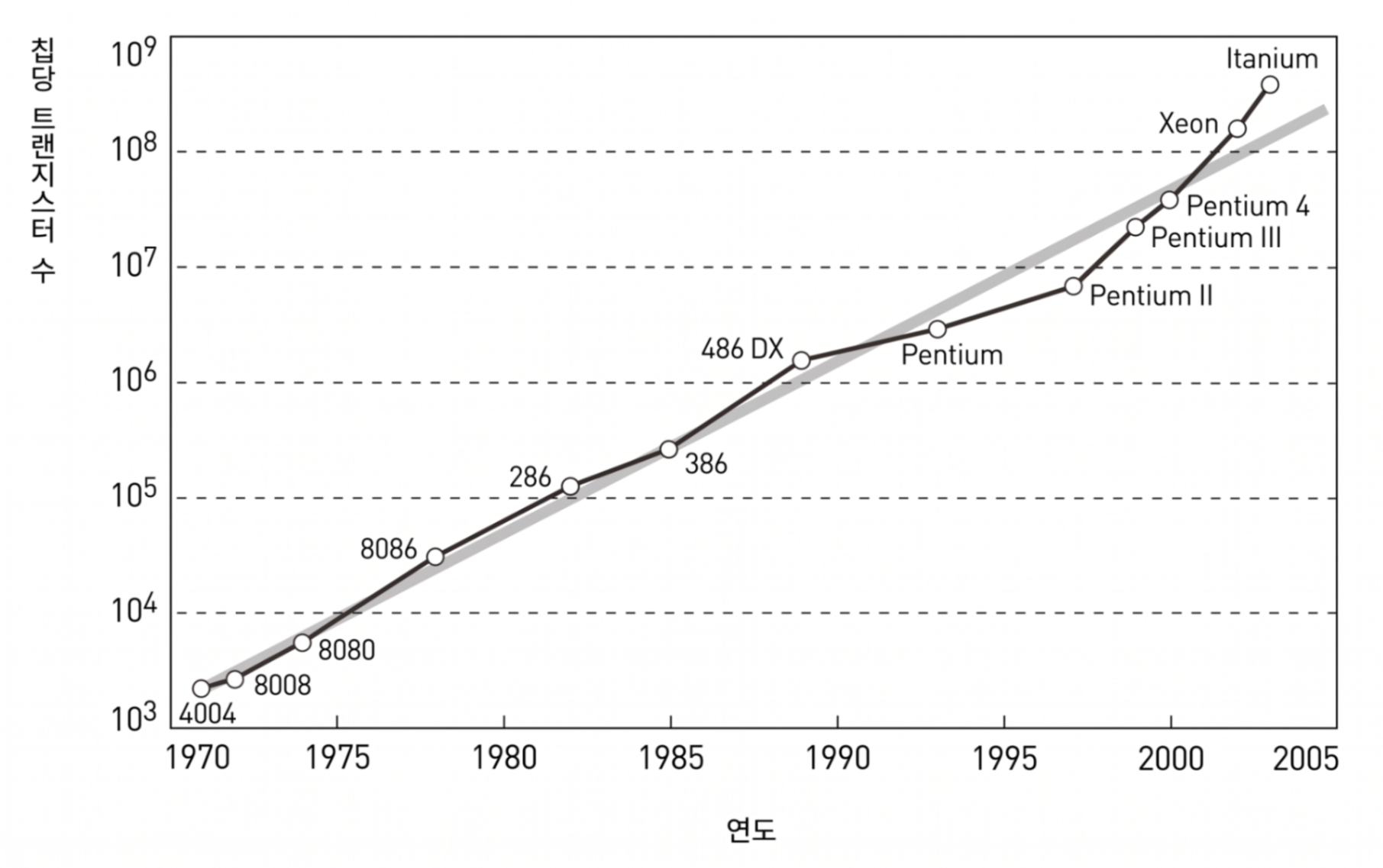

무어의 법칙은 반도체 집적회로의 성능이 18개월마다 2배로 증가한다는 법칙이다. 경험적인 관찰에 바탕을 둔 것으로 인텔의 공동 설립자인 고든 무어가 1965년에 발표한 것이다. 고든 무어의 의견은 무어 자신이 "법칙"이라고 이름을 붙인 것이 아니라 캘리포니아 공과대학의 교수와, 대규모 LSI의 파이오니아 실업가의 카버 미드에 따른 것이다. 1975년에 무어는 앞으로 2년마다 2배의 속도밖에 되지 않을 것이라고 말할 계획을 세웠다. 그는 자신이 "18개월마다"라고 한 적은 한 번도 없는데 그렇게 회자되고 있다고 주장한다.

1929년 샌프란시스코에서 태어난 고든 무어(Gordon E. Moore)는 1968년 즈음에 컴퓨터 칩 제조분야에서 가장 중요한 기업 중 하나인 인텔사의 창립에 기여함으로써 전기의 시대인 현대에 큰 발자취를 남긴다. 이로써 무어는 부와 명성을 모두 얻는다. 무엇보다도 그는 1965년에 내놓은 예언 덕분에 유명해졌다.

당시 한창 성장 중이던 컴퓨터산업의 특징을 지적한 그의 예언은 오늘날 '무어의 법칙'으로 불린다. 무어의 법칙을 간단히 표현하면 다음과 같다. “실리콘칩에 들어가는 트랜지스터의 수를 기준으로 하든, 1유로로 구입할 수 있는 저장용량을 기준으로 하던 컴퓨터의 성능(performance)은 18개월마다 항상 두 배로 높아진다.”

[무어의 법칙의 한계와 차세대 집적 기술 방향]

무어의 법칙은 오랫동안 반도체 산업의 성장 기준으로 작동해 왔지만, 미세공정이 극도로 고도화되면서 기존의 단순한 평면 스케일링만으로는 집적도와 성능을 계속 높이기 어려워지고 있다. 트랜지스터 수를 약 2년마다 2배로 늘린다는 무어의 법칙 자체는 여전히 산업의 방향성을 상징하지만, 이제는 그 목표를 달성하는 방식이 바뀌고 있다. 현재 업계는 FinFET 이후의 구조로 GAA(Gate-All-Around) FET를 도입하고 있으며, 삼성전자는 2022년부터 3nm GAA 공정 양산을 시작했고, TSMC는 2nm(N2) 공정에서 1세대 nanosheet 트랜지스터를 적용해 2025년 4분기 양산을 시작했다. 인텔 역시 RibbonFET과 PowerVia를 적용한 18A 공정을 2025년 risk production 단계에 올리며 차세대 로직 공정 경쟁에 참여하고 있다. 동시에 로직·메모리·아날로그 다이를 수직 적층하거나 고급 패키징으로 연결하는 3D 집적과 이종 집적, 여러 개의 소형 다이를 하나의 패키지로 묶는 칩렛(Chiplet) 아키텍처가 빠르게 확산되며, 성능 향상과 전력 효율 개선을 공정 미세화 외의 방식으로도 실현하고 있다. 더 나아가 차세대 구조로는 nFET과 pFET을 수직으로 적층하는 CFET가 beyond-1nm 로드맵의 유력 후보로 연구되고 있고, 2D 반도체 소재를 활용한 차세대 채널 기술도 함께 검토되고 있다. 즉, 무어의 법칙은 더 이상 단순한 선폭 축소만으로 이어지는 개념이 아니라, 새로운 트랜지스터 구조, 3D 적층, 첨단 패키징, 신소재 기술을 통해 확장적으로 계승되는 방향으로 발전하고 있다고 볼 수 있다.

▲ 인텔사 마이크로프로세서에 들어가는 트랜지스터의 개수는 무어의 법칙을 보여주는 대표적인 예다.

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기