Latch-up현상에 대해 설명해보세요.

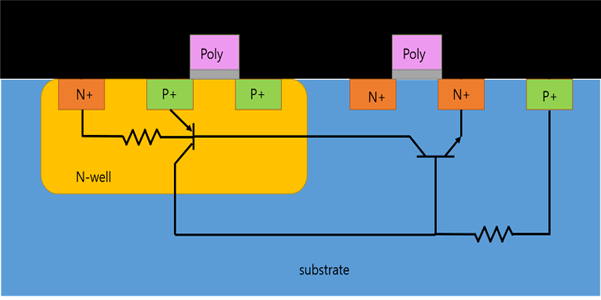

Latch-up은 CMOS에서 발생할 수 있는 고유의 자기파괴 현상이다. 이는 CMOS회로에서 발생할 수 있는 가장 큰 문제 중의 하나로, 어떤 특정한 조건에 의해 전원단과 ground단의 path가 형성되어 높은 전류가 흘러 실제 전원을 차단하기 전에 계속적으로 전류가 증가하게 되어 본 CMOS 회로를 파괴하게 하는 증상이다. 이는 CMOS 회로 구성에 따른 기생 바이폴라 트랜지스터 (parasitic bipolar transistor)에 의해 pnpn 구조가 만들어지고, 이것이 SCR(Silicon Controlled Rectifier; Thyristor) 동작이 발생하면서 VDD 및 GND에 직접적인 연결통로가 만들어지게 된다. 이는 지속적인 과전류의 통로가 되면서 소자는 파괴되는 현상이 바로 Latch-up이다.

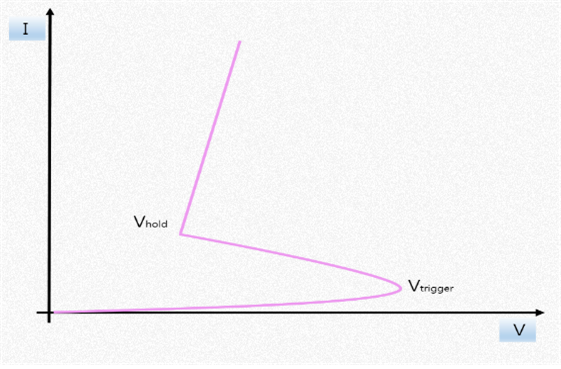

Latch-up이 발생하는데는 크게 두 가지 원인이 있다. 한 가지는 현재 advanced CMOS 기술에서 일반적인 β값은 npn이 1~5, pnp가 1~3 이 되기 때문이다. 결과적으로 βnpn X βpnp 는 일반적으로 1보다 크게 되며, 만약 여기에서 전원인 Vdd가 pnpn(SCR)이 갖는 holding voltage보다 높다면, 이것이 바로 Latch-up 문제를 만드는 주요한 원인이 되는 것이다. 만약 pnp에 순방향 bias가 걸린다면(forward biased), 여기에 substrate로 hole이 공급되게 된다. 이는 npn을 동작시키게 되는 것이다. trigger voltage에 대한 I-V 곡선은 아래 그림과 같다. 여기서, trigger voltage는 트랜지스터를 켜기 위해 p+ 전압이 n-well의 potential 전압보다 높게 되는 지점을 의미하며, holding voltage는 latchup을 발생하게 하는 전압을 의미한다. 반대로, npn에 순방향 bias가 걸린다면(forward biased), n-well에 전자(electrons)를 공급하게 되며, 이는 pnp를 동작시키게 하는 원인이 되는 것이다.

<Overshoot I-V curve of an SCR curve>

또 다른 경우는 외부에서 majority carriers가 들어올 때이다. 이 경우, holes가 p-type substrate로 들어가게 되고, 이 substrate의 전위(potential)가 크게 되며, 이는 결과적으로 순방향 bias를 만들어 Latch-up이 발생되도록 하게 되는 것이다. npn에서 p-substrate가 증가되면, 순방향 bias를 만드는 것이다. 일단 그렇게 되면 1)에서 설명하였듯이 순차적으로 서로를 triggering하게 되고 이는 다시 Latch-up을 만드는 것이다.

Latch-up 방지를 위한 방안은 다음과 같다. ① loop gain을 낮춘다. (βnpn X βpnp < ①이 되도록 한다. ② current gain을 낮춘다. p-substrate 및 n-well의 저항치를 낮추어 current gain을 낮출 수 있다. ③ 그 외 공정적인 개선안을 활용한다. (Epitaxial process), 4) 회로적인 개선안을 화룡한다. 예를 들어 CMOS 부품 전원단에 저항을 달아 공급되는 current 자체를 줄이면 Latch-up을 예방할 수 있다.

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기