시퀀셜 회로와 컴비네이션 회로에 대해 설명해보세요.

순차 회로(sequential circuit)와 조합 회로(combination circuit)는 논리 회로라고 하며 설계에 논리식이나 진리표가 사용된다.

① 조합 회로

- 입력 신호만으로 출력이 결정되는 회로이다.

- 기본적으로 논리 게이트, 셀렉터, 멀티플렉서, 가산기가 있다.

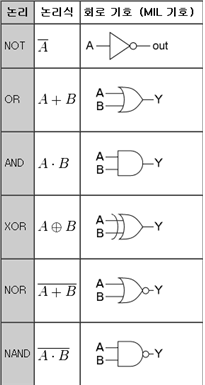

- 논리 게이트는 NOT, OR, AND, NOR등 기본이 되는 논리 연산을 수행한다.

<논리 게이트>

- 셀렉터는 출력 신호 중 하나를 선택하여 출력하는 것이고, 멀티플렉서는 입력 회로 중 하나를 선택하여 출력한다.

- 가산기는 이진수 연산(덧셈이나 뺄셈)을 처리하는 것이다.

② 순차회로

- 레지스터,카운터,시퀀서가 있다.

- 레지스터(register)(플립플롭/래치)

: 레지스터는 제어 신호에 따라 현재의 입력 신호가 저장되거나 이전의 입력 신호를 보관

유지하는 것이다.

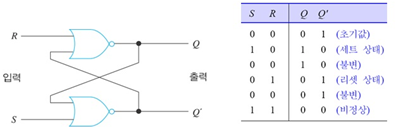

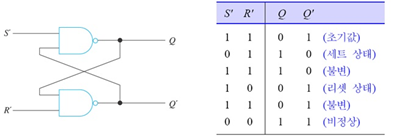

: 래치는 한 비트의 정보를 저장 하는 회로이다. 두 가지 상태의 입력(Set,Reset)에 따라 출력 상태(Q,Q`)를 가지며, nor 게이트를 이용하거나 nand를 이용해 구성할 수 있다.

- 입력 R과 S 의 상태에 따라 출력 Q,Q' 의 상태가 변하는 NOR 게이트를 이용한 SR 래치이다. S,R의 값이 모두 0(low)일 때, 출력 Q의 상태가 변하지 않으며 입력 S,R이 서로 다를 때 출력 Q의 상태가 반전 된다.

- 플립플롭

비트의 정보를 보관, 유지할 수 있는 회로이며 순차 회로의 기본 부품이다. 컴퓨터의 주기억장치나 CPU 캐시, 레지스터를 이루는 기본 회로 가운데 하나이다. 조합 회로를 단순하게 하여 조합 논리를 실현하는 회로가 아니고, 입력에 대하여 지연된 하나의 출력을 입력에 피드백하는 것으로 정보를 보관, 유지하는데 사용하는 특징이 있다. 이것을 조합 회로에서 일반적으로 음의 성질로 여겨지는 입력 신호에 대한 출력 신호의 지연을 피드백, 루프를 구성하는 것으로 반대로 사용한 것이 흥미롭다. 그 구조는 계전기(릴레이)를 이용한 자기 보관유지 회로(셀프홀드 회로)에도 비슷하게 사용되고 있다. 플립플롭은 구조상 휘발성이다. 즉 정보는 전원이 있을 때만 보관, 유지되며 전원이 차단되면 정보는 사라진다. 플립플롭으로 구성하는 램을 에스램(SRAM)이라고 부른다.

플립플롭은 내부가 논리 회로로 구성되어 있기 때문에 논리 회로에 준하는 빠른 동작속도를 얻을 수 있다. 예를 들어 컴퓨터의 기억장치를 구성하는 회로에서 주로 사용되는 방식인 디램 (DRAM)의 기억 소자와 비교했을 때 기억내용의 변경에서 축전기(캐패시터라고도 함) 충전/방전을 기다릴 필요가 없고 기억내용의 읽기에서 내용에 영향을 주지 않아서 비파괴 읽기이며 정기적인 리프레시 동작도 필요하지 않는다. 반면에 1 비트의 회로가 복잡하기 때문에 대규모가 되면 1 비트당 비용이 비싸지는 경향이 있다. 이러한 성질때문에 최근에는 플립플롭을 CPU 캐시나 중앙 처리 장치의 레지스터같은 비교적 소용량으로 고속성이 요구되는 곳에 사용하고 주기억에는 주로 디램을 이용하는 것처럼 기억 계층을 구성해서 다른 회로방식의 기억장치와 조합한 형태로 사용되는 것이 많다.

카운터는 레지스터와 게이트로 구성되어서 순서에 따라 일정한 출력이 나오고, 일정한 주기가 되면 초기상태로 되돌아간다.

시퀀서는 입력 신호에 따라서 카운터, 레지스터, 게이트 등으로 제작된 회로가 연산 및 일련의 동작을 한다.

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기