반도체 패키지의 종류와 최근 동향에 대해서 설명해 보세요.

전자부품을 제작하는 데 있어 반도체 웨이퍼에 회로를 구현하는 것을 전 공정이라 하고, 웨이퍼를 실제 제품에서 사용할 수 있는 상태로 조립하는 것을 후 공정, 또는 패키징 공정이라고 한다.

스마트폰에 사용되는 반도체 부품은 빠른 전기적 성능과 저전력 구동, 전자파를 차폐하는 것이 요구되고 있다. 전체 크기를 줄이기 위해 여러개의 칩을 PCB위에 실장한 후 한번에 패키징하는 SIP(System In Package)와 패키지를 적층하는 POP (Package On Package), WLCSP(Wafer Level Chip Scale Package)이 사용된다. 반도체 부품의 두께를 줄이기 위해 여러개의 칩을 적층한 후 패키징하는 MCP(Multi Chip Package)가 주로 사용되고 있으며, 칩을 적층한 후 곧바로 Via를 통해 연결하는 TSV(Through Silicon Via) 기술은 현재 HBM(High Bandwidth Memory)의 핵심 기반 기술로 이미 양산에 적용되어 있으며, 차세대 메모리 및 3D 이종 집적 패키지로 적용 범위가 계속 확대되고 있다.

반도체 부품을 구현하는 다양한 패키지에 대해 소개하면 다음과 같다.

① QFN (Quad Flat No lead)

QFN은 구리 리드프레임 위에 칩이 올리고 와이어 본딩을 한 후 몰딩을 한 형태로 리드가 없어서 작고 가벼우며 전기적 성능과 열적 특성이 우수하고 신뢰성이 좋다. QFN은 반도체 패키지 중 가장 저렴하면서도 지속적으로 사용되는 패키지이다.

② TSOP(Thin Small Outline Package)

PC에 사용되는 메모리 패키지로 리드프레임을 사용하는 가장 일반적으로 사용되는 TSOP는 리드프레임 위에 칩을 올리고 와이어 본딩, 몰딩을 한 후 리드를 구부려 완성한다. DRAM, SRAM, Flash 메모리 패키지로 주로 사용된다. 패키지 두께가 1mm이고, 리드간 피치가 0.5mm이다.

③ BOC(Board on Chip)

PC와 노트북에서 리드프레임이 아닌 PCB형태의 메모리 패키지로 사용되는 BOC(Board on Chip)는 기판에 메모리칩의 본딩면이 부착되며, 칩의 본딩패드와 기판의 본딩패드를 기판의 중앙에 형성된 슬롯을 통하여 와이어 본딩으로 연결하는 구조로 이루어져 있다. 와이어 본딩이 슬롯을 통해 이루어지므로 전체 크기를 TSOP에 비해 작고 얇으며, 고속화가 가능한 장점을 가지고 있다.

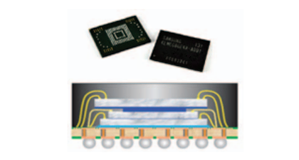

④ MCP (Multi-Chip Package)

MCP는 박판의 기판위에 50~80um의 얇은 칩을 여러 개 적층하여 용량과 성능을 증가시킨 구조로 모바일기기에 사용되는 메모리에 사용된다. 패키지 형태로는 FBGA(Fine Pitch Ball Grid Array)이다. 이와 같은 패키지를 구현하기 위해서는 웨이퍼를 얇게 하는 기술, 얇은 칩을 적층하고 와이어 본딩하는 기술이 필요하다. 메모리 소자는 칩을 2층 쌓는 DDP (Double Die Packaging), 3층 쌓는 TDP (Triple Die Packaging), 4층 쌓는 QDP (Quad Die Packaging)가 사용되고 있으며, eMMC(embedded Multi Media Card), eMCP(embedded Multi Chip Package)가 모바일 기기용 메모리 소자의 주류였으나, 현재는 고성능 스마트폰을 중심으로 더 빠른 UFS(Universal Flash Storage)로의 전환이 급격히 이루어지고 있다. 2024년 기준 6억 2천만 대 이상의 스마트폰이 eMMC에서 UFS로 전환되었으며, 중저가 기기에서도 UFS 채택 비중이 45%를 넘어섰다. 또한 LPDDR과 UFS를 하나의 패키지에 통합한 uMCP(Universal MCP)가 eMCP의 후속으로 부상하여 5G 스마트폰용 메모리 솔루션으로 채택이 확산되고 있다.

첫번째로, MCP용 핵심 package 공정 기술을 살펴보면, 박형 패키지 구현을 위해서는 얇은 PCB 기판위에 MCP형태로 메모리 칩을 적층한 후 얇게 몰딩하는 기술이 필요하다. Chip 두께를 얇게 back-grinding해야 하는데, 50um두께까지는 일반 mechanical grinding과 polishing으로 진행하고, 50um이하의 두께는 DBG (Dicing before Grinding) 공정 방식을 도입해야 한다. DBG 공정은 백 그라인딩을 하기 전에 wafer saw하고, tape를 마운팅하여 chip을 얇게 백 그라인딩 할 때 발생하는 칩 휨현상 (chip warpage)을 방지할 수 있다. 그리고 50um 이하의 얇은 칩을 saw하기 위해서는 laser를 이용하여 칩에 손상이 없도록 최적화해야 한다. 또한 얇은 칩을 웨이퍼 마운트 테이프에서 떼어 PCB에 붙이는 기술이 필요한데 이를 위해 pin을 사용하지 않는 특별한 kit 개발이 필요하다.

또한 Chip 두께를 얇게 backgrinding해야 하는데, 50um 두께까지는 일반 mechanical grinding과 polishing으로 진행하고, 50um이하의 두께는 DBG (Dicing before Grinding) 공정 방식을 도입해야 한다. DBG 공정은 백 그라인딩을 하기 전에 wafer saw하고, tape를 마운팅하여 chip을 얇게 백 그라인딩 할 때 발생하는 칩 휨현상(chip warpage)을 방지할 수 있다. 그리고 50um 이하의 얇은 칩을 saw하기 위해서는 laser를 이용하여 칩에 손상이 없도록 최적화해야 한다. 또한 얇은 칩을 웨이퍼 마운트 테이프에서 떼어 PCB에 붙이는 기술이 필요한데 이를 위해 pin을 사용하지 않는 특별한 kit 개발이 필요하다. 이후 wire bonding 공정에서는 두께가 얇아져서 와이어 본드 하기 어려운 협소한 공간에 매우 낮은 높이로 와이어 본딩을 진행하여 칩에 손상이 없도록 해야 한다.

[첨단 패키지 기술 동향]

AI 반도체 수요의 급증과 함께 2.5D·3D 이종 집적 패키지 기술이 빠르게 발전하고 있다.

CoWoS(Chip-on-Wafer-on-Substrate): TSMC의 2.5D 패키지로, HBM과 GPU 다이를 실리콘 인터포저 위에 나란히 배치한다. NVIDIA H100·H200·B200의 패키지에 적용되며, AI 반도체 수요 급증으로 CoWoS 생산 캐파가 공급 병목이 되고 있다.

SoIC(System on Integrated Chips): TSMC의 3D 이종 집적 플랫폼으로, 로직 다이와 캐시 다이를 직접 본딩(Direct Bonding)으로 적층한다. Apple A17 Pro는 InFO-PoP 패키징을 사용한 것으로 확인되었으며, SoIC는 Apple M4/M5 시리즈(2025년)에 본격 적용되어 CPU·GPU 블록의 3D 수직 연결을 가능하게 하는 기술로 채택 범위가 확대되고 있다.

Foveros(Intel): 로직 다이 위에 액티브 인터포저를 탑재하는 3D 스태킹 방식으로, Intel Meteor Lake(2023년)에 적용되었다.

X-Cube(삼성전자): HBM 위에 로직 다이를 직접 탑재하는 3D 스태킹 패키지로, 차세대 AI 메모리 적용을 목표로 개발 중이다.

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기