패키지 공정에 대해서 설명해보세요.

[패키지 공정이란]

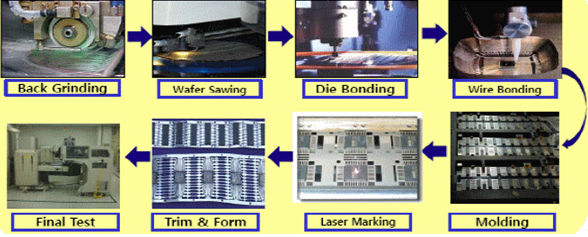

패키지 공정(후공정)은 웨이퍼 공정(전공정) 완료 후 진행되는 단계로, ① 웨이퍼 다이싱(Dicing) → ② 다이 어태치(Die Attach) → ③ 와이어 본딩 또는 플립칩 범핑 → ④ 몰딩(Mold Compound) → ⑤ 솔더볼 어태치 → ⑥ 최종 테스트(Final Test) 순으로 진행된다. 각 공정에서 칩의 전기적 연결, 기계적 보호, 열 방출 기능이 구현된다.

[자세한 과정]

반도체 Package 공정은 크게 반도체 Chip의 종류에 따라 두 가지의 형태로 분류된다. 즉 기존의 대부분을 차지하는 Lead Frame 형태의 Normal Type, 그리고 Input, Output의 증가에 따른 Pin 수의 증가를 보장하기 위한 BGA Type이 있다. 일반적인 Normal Type의 Package 공정을 살펴보면 아래와 같다.

① Back grind 공정

FAB 업체에서 만들어진 Wafer의 뒷면을 연마하는 Back Grind를 실시한다. Back Grind의 목적은 28mm에 가까운 Wafer의 두께를 8mm(8" wafer) 혹은 4mm (6")까지 grinding 함으로써 경박 단소의 요구에 충족하고 wafer의 균일한 표면 거칠기 제공, 제품의 전기적 특성 향상, saw 공정에서의 로드를 줄일 수 있는 등의 장점으로 부각된다.

② Lamination공정

Back Grind 공정이 끝나면 wafer mount 공정이 진행된다. 이러한 과정을 Lamination 과정이라 부른다. Wafer mount의 목적은 sawing 후 die가 떨어지는 것을 방지하기 위하여 시행되며 blue Tape를 붙이는 것이다.

③ Saw 공정

Saw 공정에 중요한 영향을 끼치는 요인들에 대해 살펴보면 다음을 꼽을 수 있다.

Cut placement accuracy and Variability cutting depth.

Dicing blade : spindle RPM, Feed speed, cooling water control

Tape의 특성 및 wafer의 특성, blade damage 등이다. Saw 공정이 완료되면 Second Inspection이 진행된다.

④ Second inspection

이 단계에서 발견되는 Defects들의 대표적인 예는 saw 공정에서 발생하는 Blade와 Kerf width에 영향을 미치는 것들이 많다. 그 예로 contamination, die mix/silicon dust, chip & scratch, mis -scribe, blade damage (chip out), chip & crack 등이 있다. Second inspection 완료 후 Die Attach 공정이 실시된다.

⑤ Die attach 공정

adhesive를 이용해 die를 frame pad 위에 붙이는 과정으로 전기적 특성 및 신뢰성을 결정하는 결정적인 중요한 요소가 된다. 이때 사용되는 adhesive는 epoxy가 사용된다. Epoxy는 열경화성 수지로 열을 가하면 굳어지는 특성을 가지는 것으로 Resin과 Ag를 혼합한 material이다. 여기에서 사용되는 Ag는 전기적 특성을 향상시키는 역할을 한다.

Die attach 과정이 완료되면 adhesive를 경화시키기 위해 oven에 cure의 과정을 거친다. 이때 적용되는 온도 profile은 spec에 의해 정해진 것으로 material에 따른 각 온도의 상승과 유지시간을 철저하게 지키는 것이 중요하다. Oven에서 cure가 후 Wire bonding 공정을 한다.

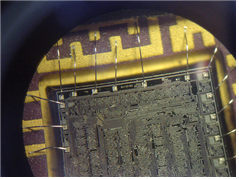

⑥ Wire bonding

Die 내의 회로와 frame pad와의 전기적 신호를 연결하기 위해 Au를 이용해 선을 연결하는 공정이다. Wire bonding에서 중요한 기본적인 요소는 온도, 수직으로 눌러주는 힘, 그리고 수평으로 문질러 주는 힘, 시간(dwell time, process time)의 4가지이다.

(Normal Type의 경우는 wire bonding 이 끝난 후 Mold 공정이 진행되고, BGA Type에서는 encapsulation 공정이 진행된다.)

⑦ Mold 공정

반도체 소자를 원하는 형태의 패키지 형태로 성형시키는 공정으로 고체 형태의 EMC를 175도의 열을 가한 후 Gel 상태로 변화시켜 원하는 형태의 틀에 투입하여 성형한다. 이러한 mold의 목적은 열 및 습기 등의 물리적인 환경으로부터 제품을 보호하고 Package의 외관을 형성하는 공정이다. 여기에서 사용되는 EMC(Epoxy Molding Compound)는 Resin을 주성분으로 각종 배합제를 가하여 성형하기 쉽게 만든 수지로 필러(60~65%) + Epoxy 수지( 5~20%) + 경화제 (5~10%)로 구성된다.

Mold의 3요소는 온도, 시간, 압력이다. 온도는 금형 표면 온도로 Auto M/C인 경우 180+-5°, 수동 M/C인 경우 170+-5°c, 시간은 EMC 이송과 경화되는데 필요한 초 단위 시간, Pressure 등이다. Mold 가 끝나면 Oven에서 Post Cure를 한다. 이때의 oven temperate와 경화시간은 spec에 따른다.

⑧ Trim 공정

Package Body와 Damber Lead 사이에 생기는 Mold Flash(Junk)를 Dejunk machine으로 제거하는 공정이다. 즉 mold 시 gel 상태의 epoxy molding compound가 extern lead 쪽으로 새어 나오지 못하도록 Dam 역할을 하는 dambar를 제거시키는 공정으로 punch의 외 측면과 die의 내 측면 사이에서 발생하는 전단력에 의해 dambar를 판단한다.

이 때 flash window에 채워져 있는 emc 일부분을 동시에 제거함으로써 dejunk 기능을 수행하게 된다. Trim 공정을 통하여 각 lead가 개별화되며 die bar cutting 후 전기적으로 독립된 단자가 된다. Trim 공정이 완료되면 plating 공정이 실시된다.

⑨ Plating 공정

solder coat 즉 표면에 SNPB 금속 이온을 입혀 주는 공정이다. 완성된 제품을 외관상으로 보기 좋게 하고 전기적 전도력을 향상시키며 leed에 부식을 방지한다. 또한 장시간 보관에도 용이하다. Plating 공정이 완료되면 Marking 공정이 진행된다.

⑩ Marking 공정

제품의 표면에 I.C의 고유 명칭, 제조 년 월 일, 제품의 특성, 일련번호 등을 고객 요구에 맞게 인쇄하는 공정으로 방법으로는 제품 표면에 표시하는 T.S.S 제품 뒷면에 표시하는 B.S.S 방법이 있다. Marking 재질에 의한 분류는 Ink Marking, laser Marking 방법이 있다. Marking 공정에서 확인해야 할 사항으로는 marking block과 marking pad의 적절한 사용 등을 고려하고 또한 marking pad에 의한 pressure가 chip에 미치게 될 영향 등을 고려해 chip에 손상이 가지 않을 정도의 pressure를 가하는 것이 중요하다.

⑪ Form 공정

프레임 잔여 부분을 자르고 리드를 구부려 준 다음 제품을 하나씩 분리하여 Tube/ Tray에 넣어주는 공정이다. 이때 굽히는 형태에 따라 gurl form, J form 등이 있다. Form 공정이 완료되면 option에 의한 test 공정이 진행된다. Test 공정에서는 RVSI를 주목할 필요가 있다.

⑫ Singulation 공정

제품의 사양 용도에 적합하도록 PCB의 불필요한 부분을 제거하는 작업으로 각각의 Unit으로 분리한다.

⑬ Test 공정

제품의 전기적인 Function을 테스트하는 것이다. 간단히 말해 Short와 open을 테스트한다고 생각하면 된다.

⑭ Packing 공정

Customer가 원하는 type으로 선적된다.

[반도체 패키징 제품]

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기