기출문제 풀이

기출문제 ❶

MOS 커패시터의 동작을 에너지 밴드 다이어그램으로 설명하시오.

STEP 1 접근 전략

설명형 문제로 난이도는 중상 수준이며 출제 빈도가 높다.

MOS 커패시터의 정의, 구조 등을 MOSFET과 비교하여 설명한다.

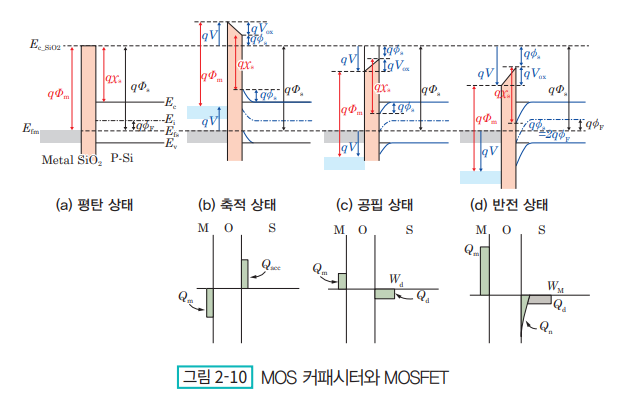

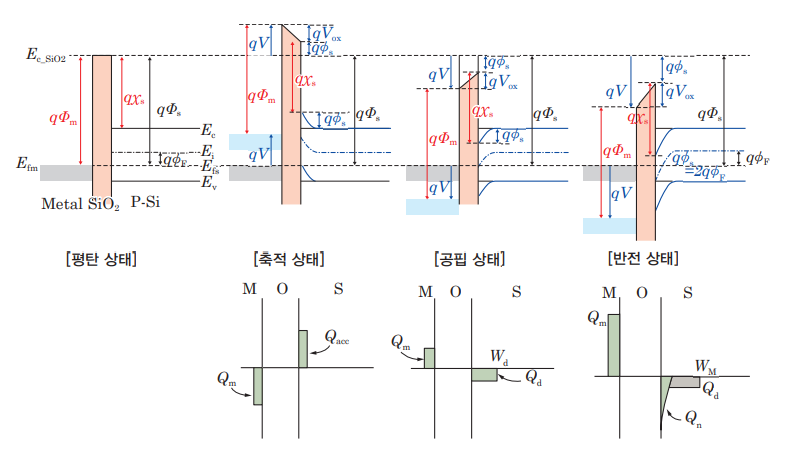

이상적인 n형 MOS 커패시터로 가정하고 게이트 전압에 따른 4가지 동작 모드를 에너지 밴드 다이어그램을 이용해 설명한다.

에너지 밴드 다이어그램은 기준 준위 상태에서 고유의 물성 인자들이 유지되기 위해 에너지 밴드가 변형되는 것임을 설명하고, 이 결과를 가지고 전하의 분포를 설명할 수 있도록 한다(거꾸로 전하의 분포에 의해 에너지 밴드의 변형이 오는 것으로 설명하지 않도록 한다).

STEP 2 답안 구조화 TIP

Q MOS 커패시터 동작 원리?

MOS 커패시터 → 게이트/산화막/반도체

2단자 커패시터 소자

이상적 n형 MOS 커패시터 → Φms = 0, Qi = 0

EBD* → 산화막 EC 기준 → Φm, Φs, χs, uF → 고유 특성

평탄, 축적, 공핍, 반전 상태 → 강 반전 → VTh

* EBD: Energy Band Diagram

STEP 3 모범답안

금속 산화막 반도체 커패시터(Metal Oxide Semiconductor Capacitor, MOS Capacitor)는 게이트(Gate), 소스(Source), 드레인(Drain), 기판(Body)으로 구성된 MOS 트랜지스터에서 소스와 드레인 없이 게이트, 절연막, 그리고 기판으로 구성되어 게이트에 인가하는 전압에 따라 특성이 변하는 2단자 소자입니다.

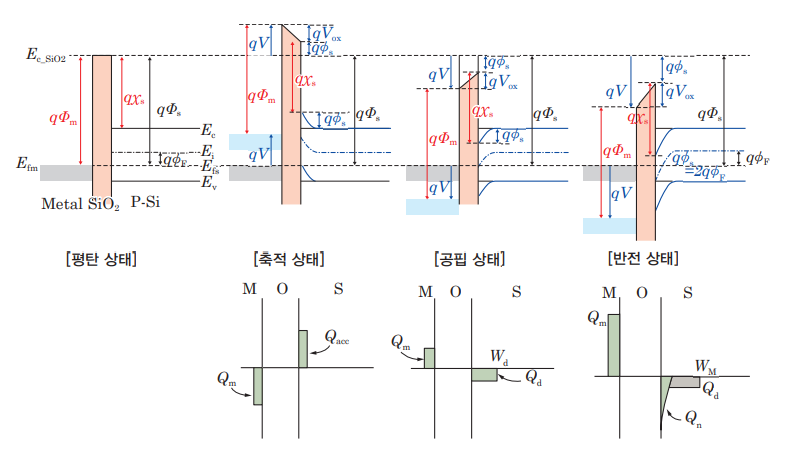

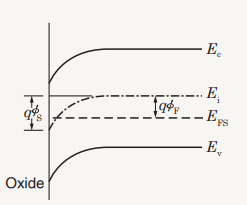

기판이 p형 실리콘인 n형 MOS 커패시터를 예로 들어 MOS 커패시터의 동작을 설명하겠습니다. 편의를 위해 MOS 커패시터의 에너지 밴드 다이어그램에서 진공 준위(Vacuum level) 가 아닌 산화막의 전도대를 기준으로 하여 금속(Φ_m)과 실리콘(Φ_s )의 수정된 일 함수(Work function), 그리고 실리콘의 전자 친화도(Electron affinity, qχs) 및 진성 에너지 준위(E_i)와 페르미 준위(E_{Fs})의 차이 Φ_F를 정의합니다.

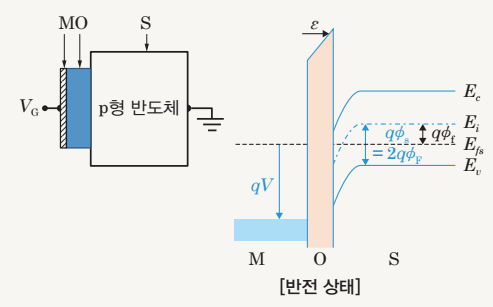

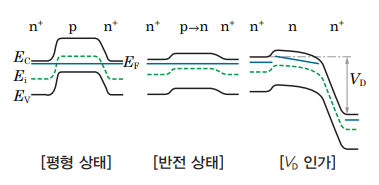

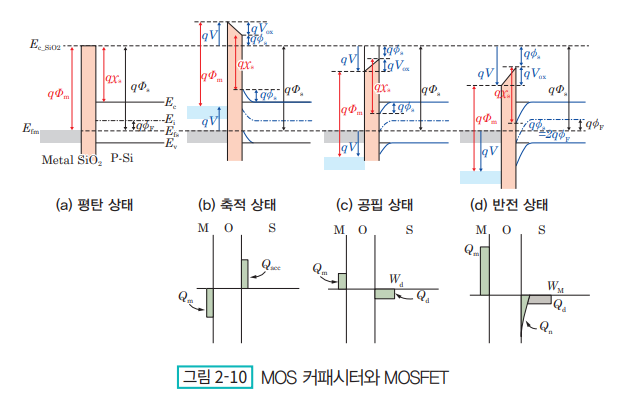

① 금속과 반도체의 일 함수가 동일하고 산화막 내 전하가 전혀 없는 이상적인 MOS 커패시터의 평탄 밴드(Flat band) 상태에서, ② 게이트에 음 전압이 인가되면 금속의 페르미 준위 (E_{Fm})는 가해준 전압(qV)만큼 올라가고 고유 특성인 qΦ_m값의 유지를 위해 금속 쪽에 접한 산화막의 E_C도 qV만큼 상승하게 됩니다. 인가한 전압 V는 게이트 산화막(V_{Ox})과 실리콘(Φs) 에 나누어 걸리게 됩니다. 기판과 접한 산화막의 E_C는 qΦs 만큼 상승하게 되어 고유 특성인 실리콘의 전자 친화도(qχ_s)를 유지하기 위해서는 실리콘 표면의 에너지(실리콘 표면과 벌크 실리콘 내의 에너지 차이)가 qΦs 만큼 위쪽으로 휘게 됩니다. 이때 전체 MOS 커패시터에는 전류가 흐르지 않으므로 E_{Fs}는 위치에 따라 일정하고 에너지 밴드의 변화는 표면에서만 일어나므로 기판 내부(Bulk)에서의 에너지 밴드는 평탄 상태와 동일하게 유지됩니다. 이렇게 에너지 밴드의 휨이 일어나면 실리콘 표면은 E_{Fs}와 E_V의 차이가 감소하여 정공인 양전하가 표면에 축적 되는 축적(Accumulation) 상태가 됩니다.

③ 게이트에 양의 전압이 인가되면 E_{Fm}은 가해준 전압(qV)만큼 내려가고 고유 특성인 qΦ_m값의 유지를 위해 금속 쪽에 접한 산화막의 E_C도 qV 만큼 하강하게 됩니다. 인가한 전압 V는 게이트 산화막(V_{Ox})과 실리콘(Φs)에 나누어 걸리게 되고, 기판과 접한 산화막의 E_{C}가 qΦ_s 만큼 내려가게 되어 역시 고유 특성인 실리콘의 전자 친화도(qχ_s)를 유지하기 위해서는 실리콘 표면의 에너지 밴드가 qΦ_s 만큼 아래로 휘게 됩니다. 이렇게 에너지 밴드의 휨이 일어나면 실 리콘 표면은 E_{Fs}와 E_i 의 차이가 감소하여 정공(캐리어)이 없고 음의 억셉터 이온만 공간 전하 (Space charge) 형태로 존재하는 공핍(Depletion) 상태가 됩니다.

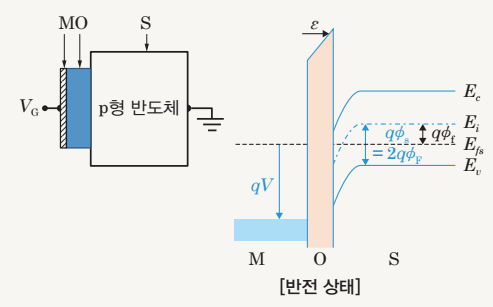

④ 게이트에 더 큰 양의 전압을 인가하면 공핍 상태보다 실리콘 표면의 에너지 밴드가 아래로 더 휘게 되는데, 이때 E_i 가 E_{Fs}보다 아래로 내려가 ΦS › ΦF 상태가 되면 실리콘 표면이 n형 반도체로 반전되는 반전(Inversion) 상태가 됩니다. 표면 에너지 qΦ_s가 qΦ_F의 2배가 되는 순간을 강 반전 상태라 하며, 이때의 게이트 전압을 문턱 전압(Threshold voltage, VTh)이라고 합니다.

고득점 답안 강 반전 이후에 게이트에 더 큰 전압을 인가하여도 공핍 영역이 더 이상 증가하지 않는 이유에 대해 설명한다. |

강 반전 상태 이후(Φ_s ≥ 2Φ_F)에는 게이트 전압에 따른 표면 전위(Φ_s)의 변화가 거의 없는데 그 이유는 Φ_s가 조금만 증가해도 반전층의 전자 농도가 지수 함수적으로 증가하게 되고 이로 인해 인가된 게이트 전압의 대부분이 게이트 산화막(V_{ox})에 걸리게 되기 때문입니다(V_G = V_{FB} + Φ_s + V_{OX}). Φ_s가 크게 증가하지 않으면 공핍 영역의 폭도 거의 변동이 없기 때문에 Φ_s = 2Φ_F 에서 공핍 영역의 폭은 최대(W_M)가 되어 더 이상 증가하지 않게 됩니다. |

꼬리 질문 MOSFET의 문턱 전압을 Φ_s=2Φ_F일 때로 정의하는 이유를 설명하시오. |

Φ_s › Φ_F인 조건부터 실리콘 표면에 반전층이 생기는 것은 사실이지만, 확실히 전기적으로 유효한 전도성을 갖는 반전층의 형성 여부를 기술하기 위해서는 실질적인 기준이 필요한데, 기존의 p형 반도체를 형성했던 억셉터 이온 농도(Na)만큼의 높은 표면 전자 농도로 반전층이 형성되는 조건을 그 기준으로 합니다. 이는 Φ_s = 2Φ_F가 되는 조건이고, 이를 강 반전(Strong inversion) 상태라 합니다. 또 이때 게이트에 인가된 전압을 문턱 전압(V_\text{Th})이라 정의합니다. |

|

기출문제 풀이

기출문제 ❷

MOSFET의 문턱 전압이 변동되었다고 할 때, 가능한 변동 원인과 해결책을 제시하시오.

STEP 1 접근 전략

설명형과 솔루션형의 복합적인 문제로 난이도는 중 수준이며 출제 빈도가 높다.

문턱 전압(V_\text{Th})의 정의와 문턱 전압을 구성하는 인자들을 설명한다.

문턱 전압(V_\text{Th})의 변동 원인을 각 인자별로 나열하고 해결책을 제시한다.

STEP 2 답안 구조화 TIP

Q MOSFET 문턱 전압의 변동 원인과 해결책?

- Ф_{ms}, Q_i → 변동폭↓

- 공핍 영역 → Q_d(∝기판 농도)^{{1}/{2}}, L_g, 기판 바이어스 효과

- C_i → T_{GOX}

- Ф_F ∝ ln(기판 농도) → 변동폭↓

→ 이온주입, T_{ GOX}, L_ g 변동 여부 확인 후 조치

STEP 3 모범답안

MOSFET의 문턱 전압은 소스와 드레인 간에 전류가 흐르기 시작할 때의 게이트 전압으로 정의되며, 수식으로는 V_\text{Th} = V_\text{FB} - Q_d/C_i + 2Φ_F = (Φ_{ms} - Q_i /C_i ) - Q_d/C_i + 2Φ_F로 표현 됩니다. 이 식의 Φ_{ms}는 게이트와 반도체의 일 함수 차이로서 게이트 전극의 소재가 바뀌지 않 으면 크게 변동되지 않는 인자이며, 도핑된 다결정 실리콘의 경우에도 도핑에 의한 E_{Fm}의 변 동에 따른 변화가 크지 않습니다. 두 번째 항인 Q_i /C_i 는 게이트 산화막 성장 시 발생될 수 있는, 유동성 이온 전하 등의 각종 원치 않는 산화막 내 전하로 인한 인자로서, 현대 반도체 공정에서는 그 양이 매우 적고 게이트 산화막의 두께도 얇아(C_i 증가) 무시할 수 있는 수준입니다. 세 번째 항인 Q_d/C_i 에서 Q_d는 공핍 영역 전하량으로 기판 농도와 게이트 길이(L_g), 기판 바이어스의 함수입니다. 따라서 문턱 전압(V_\text{Th})이 변동되는 경우에는 기판의 농도 변화, 즉 이온주입 또는 후속 열처리 공정에 문제가 없는지 확인 후 조치해야 합니다. 또한 공핍 영역의 면적은 채널의 길이와 폭의 곱이므로 이 두 값의 변동 여부를 확인해야 하며, 특히 단채널 MOSFET의 경우는 채널 길이에 따른 소스, 드레인의 기생 공핍층의 영향이 크므로 게이트 길이(Critical Dimension, CD)의 이상 여부를 확인해야 합니다. 또한 C_i 는 게이트 산화막에 의한 정전 용량으로 게이트 산화막의 두께에 반비례하므로 게이트 산화막 두께를 공정 결과나 (전기적)정전 용량 측정 결과로 확인해야 합니다. 마지막으로 2Φ_F 항목은 강 반전을 시키기 위 한 표면 전위이므로 역시 기판 농도와 관련은 있으나, Φ_{ms}의 경우와 유사하게 도핑에 의한 E_{Fs} 의 변동에 따른 변화는 둔감한 편입니다.

|

통상 MOSFET의 기판은 소스 전압과 동일한 전압을 인가하지만 소스나 드레인에 대해 역 방향 바이어스를 기판에 인가할 경우가 있는데, 이를 기판 바이어스(또는 몸통 바이어스) 라고 하며 이러한 기판 바이어스에 따라 MOSFET의 문턱 전압이 변화하는 것을 기판 바이어 스 효과라고 합니다. 기판 바이어스를 인가하면 채널에 형성되는 공핍 영역의 폭이 넓어져 공 핍 영역 전하(Depletion charge)의 양이 증가하게 되고 이를 보상하기 위해 게이트에 인가되는 전압을 증가시켜줘야 하므로 문턱 전압(V_\text{Th})은 증가하게 됩니다. 이 공핍 영역의 전하량(Q_d)은 기판 농도의 제곱근에 비례하므로 기판 바이어스에 따른 문턱 전압의 변화량도 기판 농도의 제곱근에 비례합니다. 따라서 이러한 특성을 이용해 기판 바이어스를 적절히 인가함으로써 문 턱 전압(V_\text{Th})을 제어할 수 있습니다. |

꼬리 질문 문턱 전압의 측정 방법에 대해 설명하시오. |

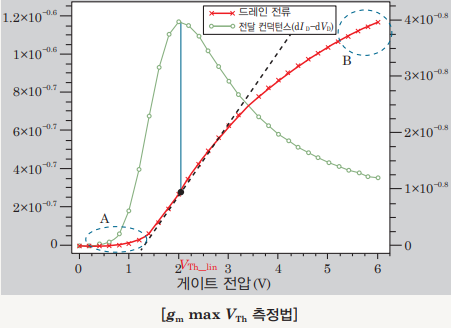

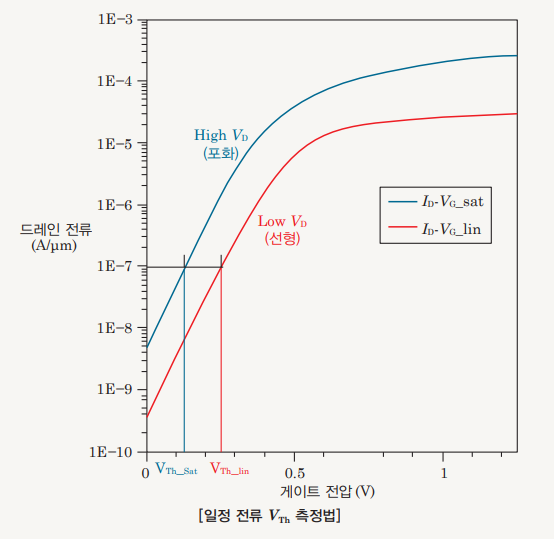

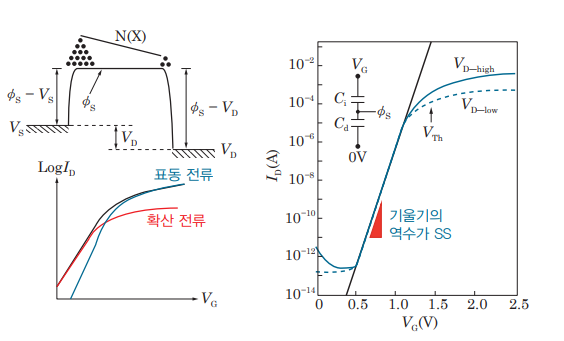

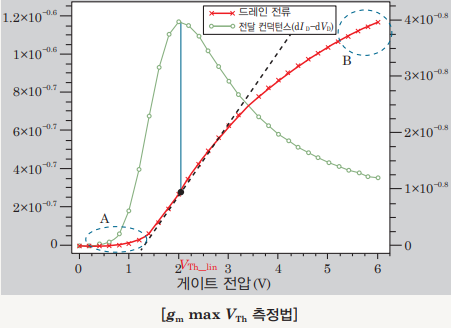

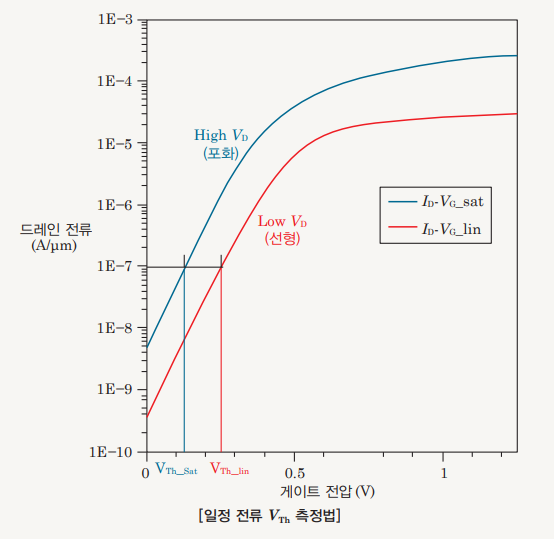

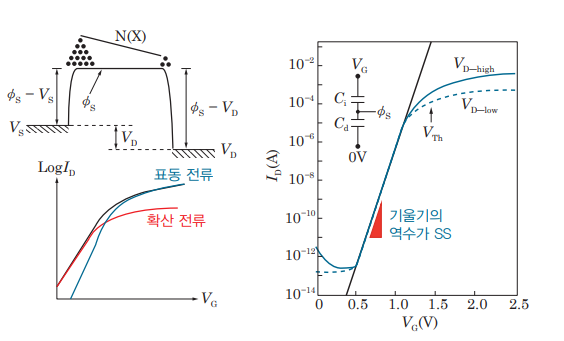

MOSFET의 전달(V_G - I_D) 특성 곡선에 전달 컨덕턴스(g_m)를 같이 그려보면, I_D는 V_G가 낮은 영역과 높은 영역에서 비선형적이며, 중간 지점에서는 거의 선형적으로 변하고 있다는 것을 알 수 있습니다. 따라서 드레인 전류가 흐르기 시작하는 게이트 전압을 정의하기가 쉽지 않아, 실험적으로 드레인 전류 곡선의 각 점에서의 기울기가 가장 큰 지점, 즉 전달 컨덕턴스 {\partial I_{DS}}/{\partial V_{GS}} 의 최고점에서 접선을 그어 그 접선이 V_G축과 만나는 절편을 문턱 전압(V_\text{th\_lin})으로 정의하는 방법을 많이 사용하는데, 이를 최대 전달 컨덕턴스(g_m \ \text{max}) 측정법이라 합니다.  문턱 전압을 측정하는 또 다른 방법은 일정 전류(Constant current) 문턱 전압 측정법입니다. 최대 전달 컨덕턴스(g_m \ \text{max}) 측정법에서는 I_D축을 선형 스케일(Linear scale)로 사용하는 반면, 이 방법은 로그 스케일(Log scale)을 사용하고 MOSFET의 폭(Width)으로 전류값을 나누어 정규화(Normalize)하여 사용합니다. 문턱 전압 측정 전류값은 업체별로 다를 수 있으나, 통상 10 \sim 100\text{nA}/\mu\text{m} 수준이며 드레인 전압을 매우 낮은 전압(예를 들어 50\text{mV})과 높은 전압(동작 전압)에서 측정하고 각각 선형 문턱 전압과 포화 문턱 전압으로 부릅니다. 문턱 전압을 측정하는 또 다른 방법은 일정 전류(Constant current) 문턱 전압 측정법입니다. 최대 전달 컨덕턴스(g_m \ \text{max}) 측정법에서는 I_D축을 선형 스케일(Linear scale)로 사용하는 반면, 이 방법은 로그 스케일(Log scale)을 사용하고 MOSFET의 폭(Width)으로 전류값을 나누어 정규화(Normalize)하여 사용합니다. 문턱 전압 측정 전류값은 업체별로 다를 수 있으나, 통상 10 \sim 100\text{nA}/\mu\text{m} 수준이며 드레인 전압을 매우 낮은 전압(예를 들어 50\text{mV})과 높은 전압(동작 전압)에서 측정하고 각각 선형 문턱 전압과 포화 문턱 전압으로 부릅니다.

|

|

기출문제 풀이

기출문제 ❸

MOSFET의 동작 원리에 대해 설명하시오.

STEP1 접근 전략

설명형 문제로 난이도는 중하 수준이며 빈출 문제이다.

MOSFET의 정의, 구조 및 용도 등에 대해 설명한다.

게이트와 드레인 전압 관계로부터 세 영역에서의 MOSFET 동작 원리를 설명한다.

STEP2 답안 구조화 TIP

Q MOSFET 동작 원리?

MOSFET → 금속 산화막 반도체 전계효과 트랜지스터

4단자 소자 (게이트 - 소스 - 드레인 - 기판)

nMOSFET, pMOSFET •응용 → 증폭기, 스위치

차단 영역, 선형 영역, 포화 영역(핀치 오프 현상)

STEP3 모범답안

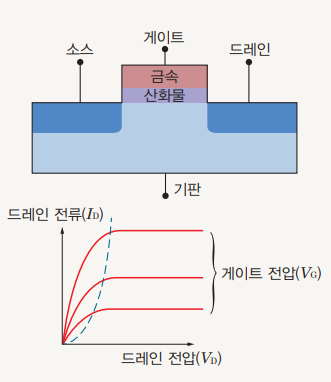

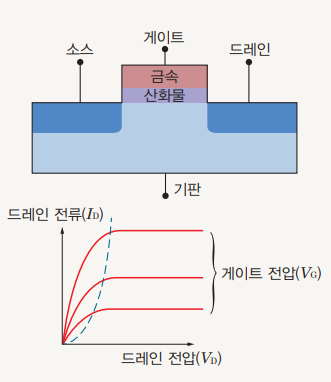

금속 산화막 반도체 전계효과 트랜지스터(Metal-Oxide-Semiconductor Field Effect Transistor, MOSFET)는 금속 또는 도핑된 다결정 실리콘 재질의 게이트와 그 하단의 \text{SiO}_2 등의 절연막, 그리고 실리콘 기판으로 구성된 MOS 커패시터의 양단에, 기판과는 반대 극성을 가진 소스(Source)와 드레인(Drain) 접합의 2단자를 추가한 4단자 소자입니다. 증폭기 또는 스위치 등으로 사용되고 있습니다. 게이트에 문턱 전압(\text{V}_{Th}) 이상의 전압을 인가하여 반도체 표면을 반전시켜 채널을 형성하고 드레인과 소스 사이에 전압을 인가하면 전류가 흐르게 되는 원리로, 이때 게이트에 인가한 전압이 증가하면 채널 내 캐리어 수가 증가하여 더 높은 전류가 흐르게 됩니다. p형 기판을 사용하여 n형의 채널이 생기는 트랜지스터를 nMOSFET(nMOS), 이와 반대의 경우를 pMOSFET(pMOS) 이라고 하며 캐리어를 공급하는 단자를 소스, 빠져 나가는 단자를 드레인이라고 합니다. MOSFET의 동작은 게이트와 드레인에 인가되는 전압 관계에 따라 세 영역에서 구동됩니다. 먼저 문턱 전압( \text{V}_{Th} ) 이하의 게이트 전압(V_G)에서는 드레인 전압(V_D) 이 인가되더라도 드레인 전류(I_D)가 흐르지 않는데 이 영역을 차단 영역이라 합니다. V_G > V_{th},\; V_D < V_G - V_{th} 조건에서는 V_D가 채널에 미치는 영향이 미미하여 채널이 단순 저항 역할을 하기 때문에I_D가 V_D에 따라 선형적으로 증가하는 선형 영역(linear region)에서 동작하게 됩니다. V_G > V_{th},\; V_D = V_G - V_{th} 조건에서는 V_G에 의해 생성된 반전층이 V_D에 의해 상쇄되므로 드레인과 접하는 위치에서 채널이 사라지는 핀치 오프(Pinch-Off) 현상이 발생하고, 이때부터는 V_D가 증가하더라도 I_D가 일정하게 포화됩니다. 이 때문에 V_G - V_{th}와 같게 되는 V_D를 포화 드레인 전압(Saturation drain voltage, V_{DSAT})이라고 합니다. V_D \ge V_{DSAT} 조건이 되면 I_D는 V_D에 더 이상 의존하지 않고 일정하게 포화되며, 이렇게 동작하는 영역을 포화 영역(Saturation region)이라 합니다.

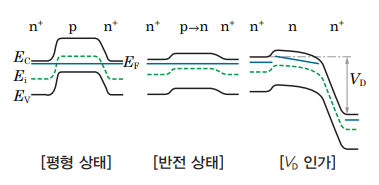

고득점 답안 (판서 가능 시) MOSFET 동작을 설명할 때 다음과 같이 평형 상태 \rightarrow 반전 상태 \rightarrow 드레인 전압(V_D) 인가 상태의 에너지 밴드 다이어그램을 그려 설명하고, 선형 영역과 포화 영역에서의 드레인 전류(I_D) 식과 함께 L가 게이트 산화막 두께, 문턱 전압, 캐리어 이동도 등의 함수임을 설명한다. |

I_D=\dfrac{W}{L}\mu_n C_{OX}\left[\left( V_G - V_{Th} \right) V_D-\dfrac{1}{2} V_D^2\right] 선형 영역 I_D=\dfrac{W}{L}\mu_n C_{OX}\left[\left( V_G - V_{Th} \right) V_D-\dfrac{1}{2} V_D^2\right] 선형 영역

I_D=\dfrac{W}{2L}\mu_n C_{OX}\left( V_G - V_{Th} \right)^2 포화 영역 |

꼬리 질문 1 MOSFET의 채널이 핀치 오프된 후 드레인 전류가 포화되는 이유에 대해 설명하시오. |

핀치 오프 이후에 드레인 전압을 높여 핀치 오프 지점이 소스 쪽으로 이동하더라도 핀치 오프 지점과 소스 간 전위차는 \displaystyle V_{DSAT}로 유지되고, 장채널(Long channel) MOSFET에서는 핀치 오프 지점과 드레인 사이의 거리(\displaystyle \Delta L)가 전체 채널의 길이 대비 매우 짧으므로 게이트 전압에 의해 생성되어 이동하는 전자의 양은 같습니다. 핀치 오프 지점과 드레인 사이에 걸리는 전압(\displaystyle V_D - V_{DSAT})은 단순히 핀치 오프 지점까지 도달한 전자를 드레인 쪽으로 끌어당기는 역할만 하게 되므로 전체 전류의 양은 일정하게 유지됩니다. |

|

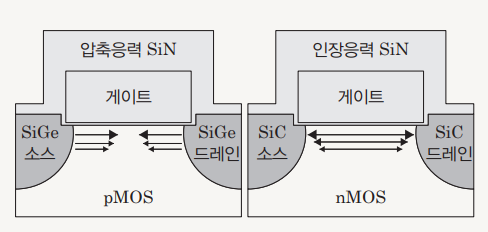

꼬리 질문 2 nMOS대비pMOS의 동작 속도가 느린 이유와 대책에 대해 설명하시오. |

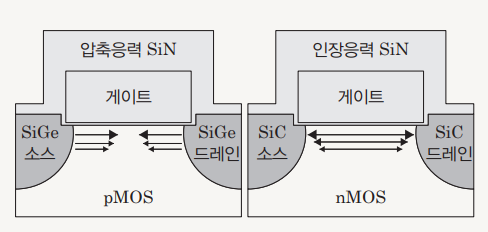

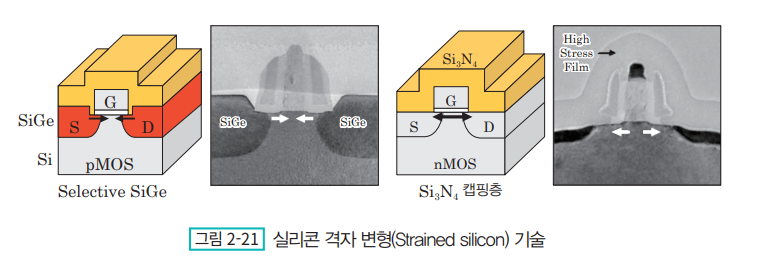

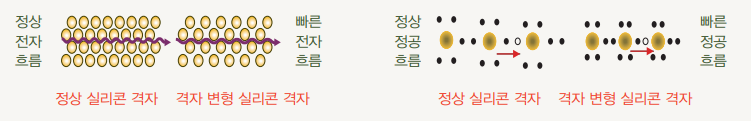

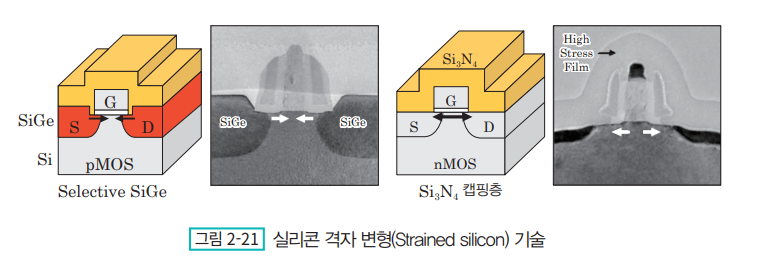

pMOS 대비 nMOS의 속도가 빠른 이유는 nMOS의 캐리어인 전자의 이동도(Mobility)가 pMOS의 정공(Hole)에 비해 2배 이상 크기 때문이며, 이러한 이동도의 차이는 정공의 유효질량이 전자보다 무겁기 때문에 발생합니다. 이동도의 차이는 전류의 구동 능력(\displaystyle I_D) 차이로 나타나고 이것이 곧 트랜지스터 속도의 차이라고 할 수 있습니다. 그럼에도 불구하고 pMOS와 nMOS로 구성된 CMOS 구조를 반도체 회로에 사용하는 이유는 nMOS로만 구성된 회로 대비 전력소모가 작기 때문이며, 통상 이러한 CMOS의 최적화된 동작을 위해 pMOS와 nMOS의 전류 구동 능력을 비슷하게 맞추게 됩니다. 이를 위해 두 가지 해결 방안이 있는데, ① pMOS의 채널 폭(Width)을 nMOS보다 2배 정도 크게 만들어 구동 전류를 증가시키거나, ② pMOS 소스 및 드레인에 격자 상수가 큰 SiGe 등을 삽입하여 채널에 압축응력(Compressive stress)을 주어 정공의 이동도를 개선하는 격자 변형(Strained silicon) 기술을 이용하는 것입니다. |

|

기출문제 풀이

기출문제 ❹

MOSFET의 미세화 시 문제점과 그 해결책에 대해 설명하시오.

STEP1 접근 전략

솔루션형 문제로 난이도는 중상 수준이며 최근 자주 출제되는 문제이다.

MOSFET의 미세화의 필요성과 문제점(단채널 효과)에 대해 설명한다.

nMOS를 예로 들어 단채널 효과의 종류별 발생 이유를 설명하고, 대책을 제시한다.

시간이 부족할 시에는 대표적인 3~4가지(모범답안의 ①, ②, ③, ⑥) 정도만 발표한다.

STEP2 답안 구조화 TIP

Q MOSFET 미세화 문제와 해결책?

소자 미세화 → 생산성↑, 성능↑

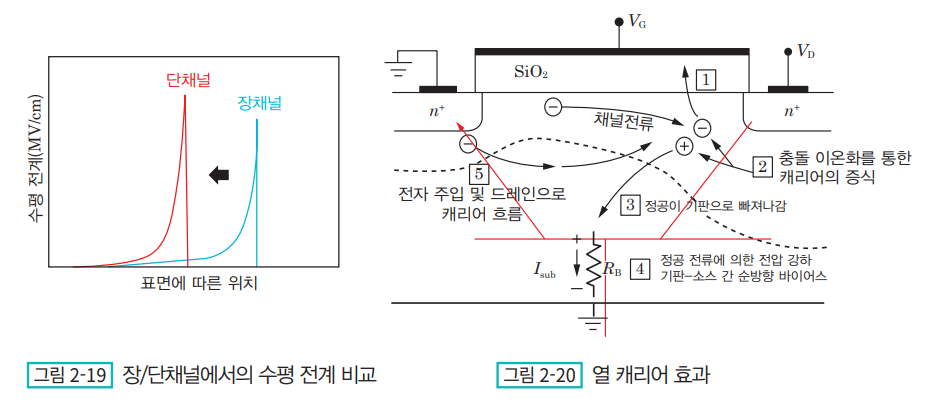

전력소모↓, 전계 유지 → 전원 전압↓, 전원 전압 감소 어려움 → 전계↑ → SCE↑

SCE: VTh roll-off, DIBL, PT. 속도 포화, GIDL, HCE 등

STEP3 모범답안

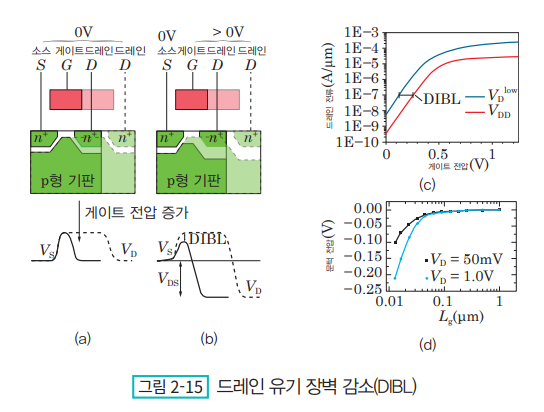

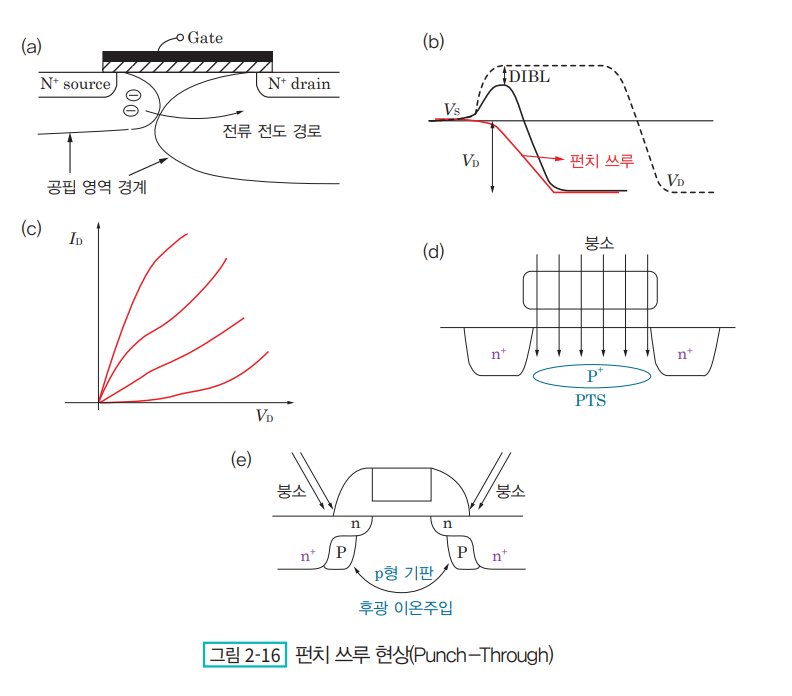

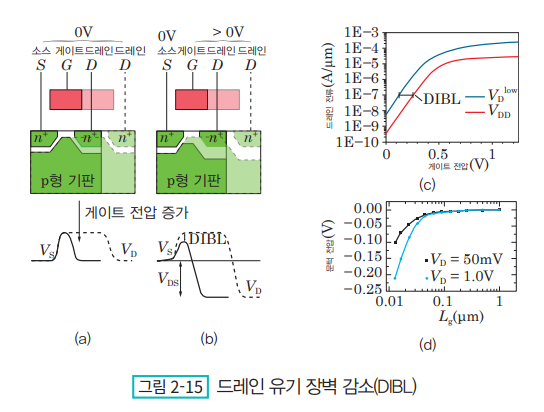

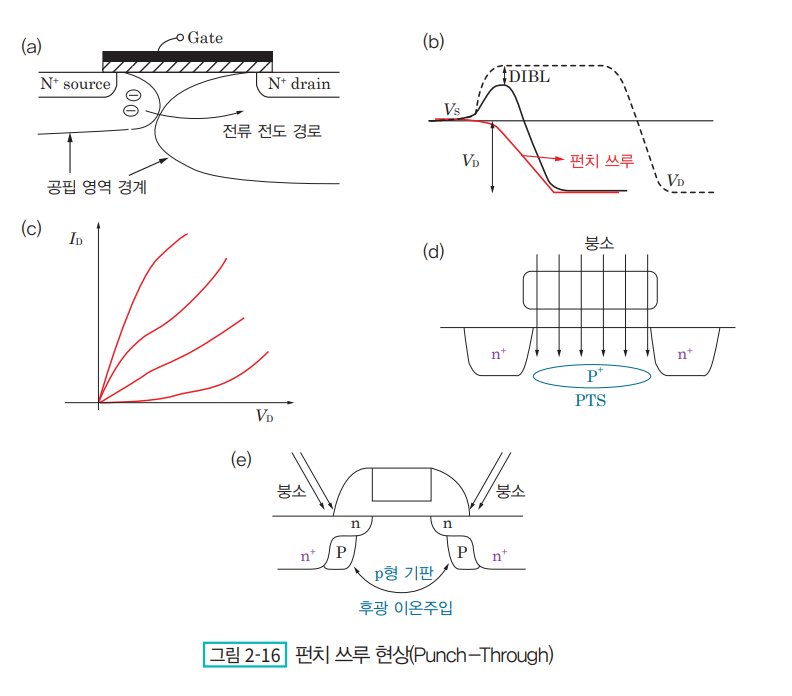

소자의 미세화는 실리콘 기판 위에 제작되는 반도체 칩의 집적도 증가를 통한 생산성 향상과 소자의 성능 개선을 목표로 합니다. 소모 전력 감소와 소자 내 일정한 전계의 유지를 위해 동작 전압 또한 감소되어야 하나, 전원 전압의 감소는 소자 미세화를 따르지 못해 소자 내 전계 증가로 인한 문제가 발생하는데, 대표적으로 채널 길이가 감소하여 발생하는 단채널 효과(Short channel effect)가 있습니다. 먼저, 게이트 전압(\displaystyle V_{G})에 의해 형성되어야 할 채널의 공핍 전하가 소스와 드레인의 공핍 영역의 영향을 받아 채널 길이가 감소하면, 문턱 전압(\displaystyle V_{Th})이 내려가는 ① 문턱 전압(\displaystyle V_{Th}) 감소 현상(\displaystyle V_{Th} roll-off)이 발생하는데 이는 채널에 주입하는 불순물 농도의 조절을 통해 해결할 수 있습니다. 다음은 드레인 전압(\displaystyle V_{D})에 의해 채널과 소스 간의 전위 장벽이 낮아져 문턱 전압(\displaystyle V_{Th})이 감소되는 ② 드레인 유기 장벽 감소(Drain Induced Barrier Lowering, DIBL) 와 이 DIBL 현상이 심화된 것으로 볼 수 있는 ③ 펀치 쓰루(Punch-through) 문제입니다. 펀치 쓰루는 \displaystyle V_{D} 인가 시 드레인과 소스의 공핍 영역이 서로 맞닿아 게이트 전압(\displaystyle V_{G})의 제어를 받지 못하고 실리콘 표면이 아닌 하부로 큰 \displaystyle I_{D}가 흘러버리는 문제이며, 이들 문제는 소스/드레인 접합 깊이의 감소, 펀치 쓰루 방지(Punch-Through Stop, PTS) 또는 후광(Halo) 이온주입과 같이 국부적으로 기판 농도를 증가시키는 방법 등으로 제어가 가능합니다.

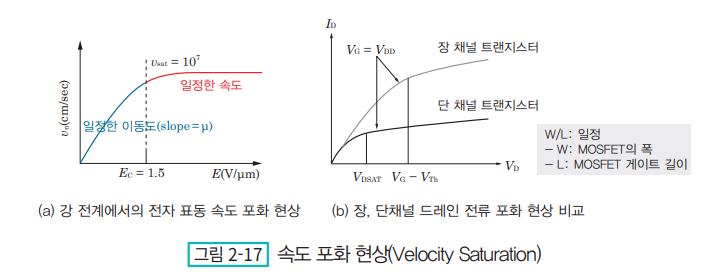

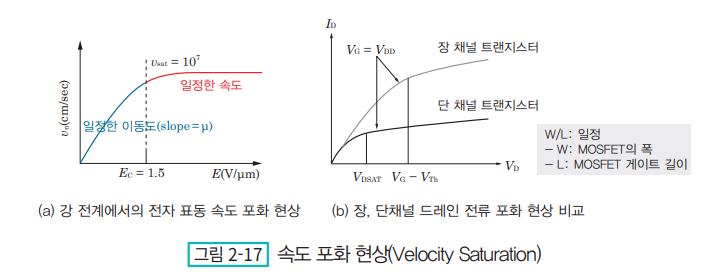

한편, 채널 길이의 감소로 소스와 드레인 간의 전계가 강해지면 특정 전계(\displaystyle \sim 10^{4} \text{V/cm}) 이상에서 캐리어의 속도가 인가한 전계에 비례(\displaystyle v = \mu E(\displaystyle \mu: v 캐리어 이동도))하지 않고 격자와의 상호 작용으로 캐리어가 에너지를 잃어 속도가 더 이상 증가하지 않아 핀치 오프(Pinch-Off) 이전에 \displaystyle I_{D}가 포화되어 버리는 ④ 속도 포화(Velocity saturation) 현상이 발생합니다. 이는 캐리어의 이동도 개선 목적의 격자 변형 기술(Strained silicon) 등의 방법으로 대응하고 있습니다.

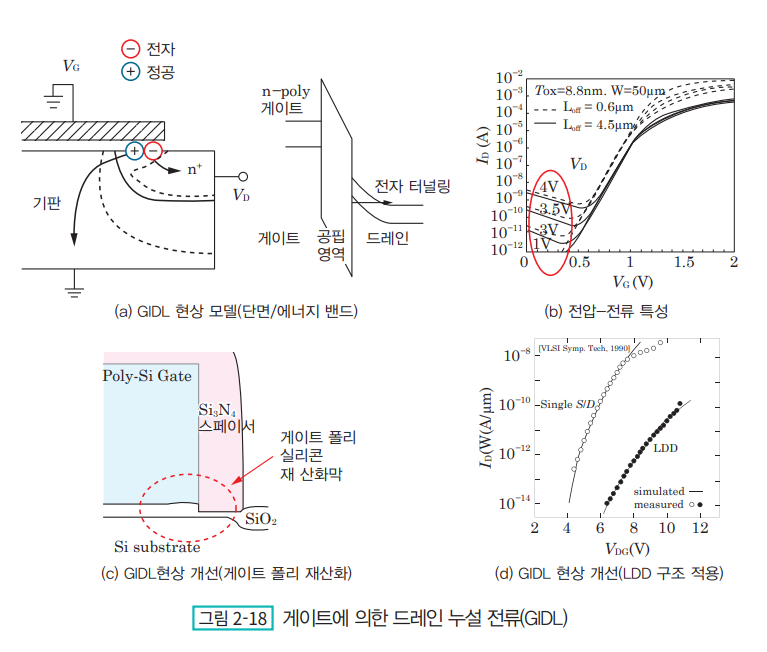

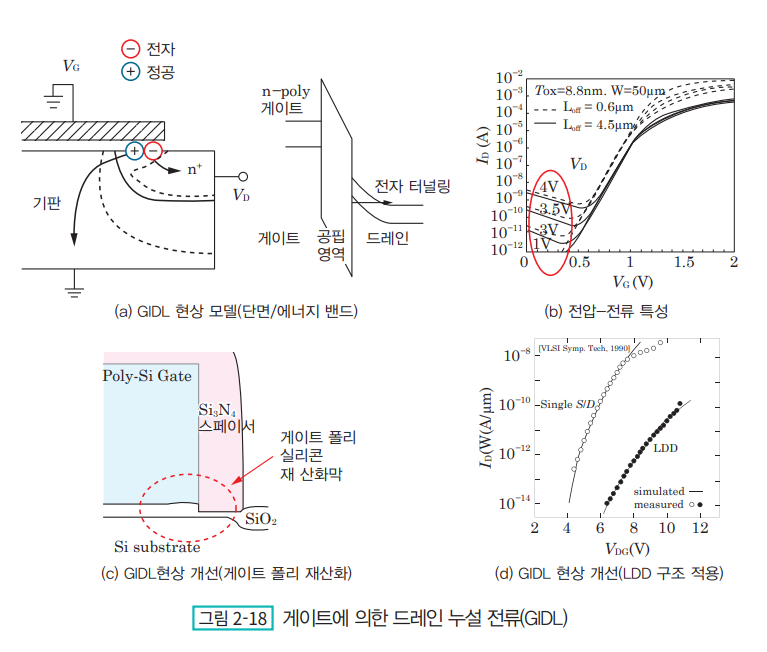

오프(Off) 상태의 MOS 트랜지스터의 게이트와 드레인 간 전압 차이가 클 경우(\displaystyle V_{G} \ll 0\text{V}), 게이트와 중첩되는 드레인의 표면에는 매우 얇은 공핍 영역이 만들어지고, 드레인 표면에서의 에너지 밴드가 많이 휘어 가전자대역의 전자가 얇아진 밴드를 뚫고 터널링에 의해 전도대역으로 이동하게 됩니다. 이동한 전자는 드레인으로, 가전자대역에 생성된 정공은 기판으로 이동하여 ⑤ 게이트 유기 드레인 누설 전류(Gate Induced Drain Leakage, GIDL)라고 하는 드레인에서 기판으로의 누설 전류가 발생합니다.

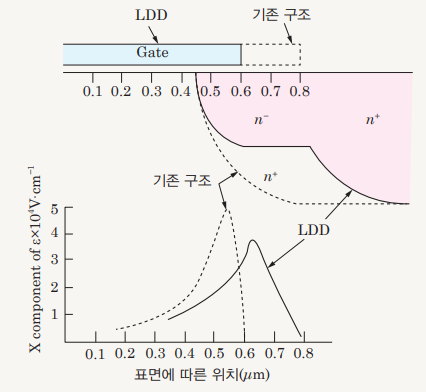

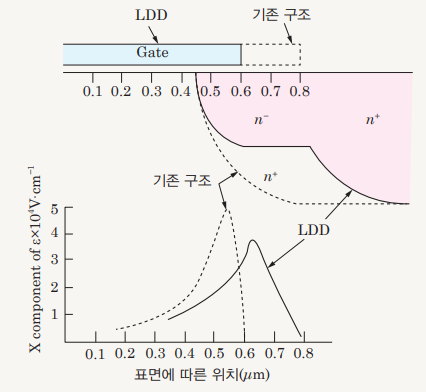

한편, 단채널화에 따른 전계 증가로, 채널을 이동하는 전자는 높은 에너지를 얻게 되는데 이러한 전자를 열 전자(Hot electron)라고 합니다. 열 전자들은 인가된 \displaystyle V_{G}에 의해 게이트 절연막을 통과하기도 하고 절연막에 포획되어 소자의 문턱 전압(\displaystyle V_{Th}) 변동 및 산화막의 파괴를 야기하기도 합니다. 또한 고전계의 드레인 부근에서 실리콘 격자와 충돌하여 전자-정공 쌍을 생성시켜(충돌 이온화) 기생 바이폴라 트랜지스터 동작에 의한 CMOS 래치업(Latch-Up) 등의 불량을 초래할 수 있는 ⑥ 열 전자 효과(Hot Electron Effect, HCE)를 발생시킬 수 있습니다. 이러한 HCE는 드레인의 불순물 도핑 농도를 국부적으로 줄인 LDD(Lightly Doped Drain) 구조를 사용하여 전계를 감소시킴으로써 완화할 수 있습니다.

고득점 답안 상온에서 Sub-Threshold Swing(SS)을 이론상 60mV/dec 이하로 낮출 수 없는 이유에 대해서도 알고 있다면 당 신은 이미 소자의 달인! |

공핍 또는 약 반전 상태, 즉 문턱 전압 이하에서도 미량의 전류가 흐르는데 이 전류를 문턱 전압 이하 누설 전류(Sub-Threshold leakage current)라고 합니다. 문턱 전압 이상에서는 드레인 전압(\displaystyle V_{D})에 의한 표동(Drift)으로 드레인 전류(\displaystyle I_{D})가 흐르지만, 강 반전층이 생기지 않은 상태에서는 캐리어의 확산에 의해 전류가 흐르게 됩니다. 게이트 전압(\displaystyle V_{G})이 증가(\displaystyle > V_{Th})하게 되면 채널의 표면 전위(Surface potential, \displaystyle \phi_{s})가 증가하고 이에 따라 소스에서 채널 쪽으로 이동하는 캐리어의 수가 지수 함수적으로 증가(\displaystyle n \propto \exp({q\phi_{s}}/{kT}))하게 됩니다. \displaystyle I_{D}는 캐리어의 농도에 비례하므로 \displaystyle I_{D} = A \cdot \exp({q\phi_{s}}/{kT}) (A: 비례상수)로 쓸 수 있습니다. 게이트 전압에 따른 \displaystyle \phi_{s}는 게이트 산화막(\displaystyle C_{i})과 실리콘의 공핍 영역(\displaystyle C_{d})에 의한 정전 용량의 전압 분배 관계로부터 \displaystyle \phi_{s} = [{C_{i}}/({C_{i} + C_{d}})] \cdot V_{G}가 됩니다. 공핍 또는 약 반전 상태, 즉 문턱 전압 이하에서도 미량의 전류가 흐르는데 이 전류를 문턱 전압 이하 누설 전류(Sub-Threshold leakage current)라고 합니다. 문턱 전압 이상에서는 드레인 전압(\displaystyle V_{D})에 의한 표동(Drift)으로 드레인 전류(\displaystyle I_{D})가 흐르지만, 강 반전층이 생기지 않은 상태에서는 캐리어의 확산에 의해 전류가 흐르게 됩니다. 게이트 전압(\displaystyle V_{G})이 증가(\displaystyle > V_{Th})하게 되면 채널의 표면 전위(Surface potential, \displaystyle \phi_{s})가 증가하고 이에 따라 소스에서 채널 쪽으로 이동하는 캐리어의 수가 지수 함수적으로 증가(\displaystyle n \propto \exp({q\phi_{s}}/{kT}))하게 됩니다. \displaystyle I_{D}는 캐리어의 농도에 비례하므로 \displaystyle I_{D} = A \cdot \exp({q\phi_{s}}/{kT}) (A: 비례상수)로 쓸 수 있습니다. 게이트 전압에 따른 \displaystyle \phi_{s}는 게이트 산화막(\displaystyle C_{i})과 실리콘의 공핍 영역(\displaystyle C_{d})에 의한 정전 용량의 전압 분배 관계로부터 \displaystyle \phi_{s} = [{C_{i}}/({C_{i} + C_{d}})] \cdot V_{G}가 됩니다.

한편 SS는 \displaystyle V_{G}에 따른 \displaystyle \log I_{D}의 변화량의 역수로 정의되는 값으로, \displaystyle I_{D}가 10배 증가하는 데 필요한 \displaystyle V_{G}를 의미합니다. 즉, \displaystyle \text{SS} = [{d(\log I_{D})}/{dV_{G}}]^{-1} = [{d(\log I_{D})}/{d\phi_{s}}] \cdot [{d\phi_{s}}/{dV_{G}}]^{-1}의 관계가 성립합니다. 여기에서 \displaystyle \log I_{D} = \log A + ({q\phi_{s}}/{kT}) \log e가 되고, \displaystyle {d(\log I_{D})}/{d\phi_{s}} = ({q}/{kT}) \cdot \log e, \displaystyle {d\phi_{s}}/{dV_{G}} = {C_{i}}/({C_{i} + C_{d}})가 됩니다. 따라서 \displaystyle \text{SS} = ({kT}/{q}) \ln(10) [1 +( {C_{d}}/{C_{i}})] \text{ (mV/dec)}로 정리할 수 있습니다. 상온에서 \displaystyle ({kT}/{q}) \ln(10) \approx 60 \text{mV/dec}이므로 이론적으로 MOSFET의 SS는 60 \text{mV/dec}가 최솟값이 되는 것입니다. SS는 \displaystyle \log I_{D} - V_{G} 직선의 기울기의 역수이므로, 값이 작을수록 직선의 기울기가 급해져 트랜지스터의 On/Off 특성이 좋아지고 오프 전류(\displaystyle I_{off})도 감소합니다. 따라서 SS값을 감소시키기 위해서는 \displaystyle C_{d}는 최소, \displaystyle C_{i}는 최대화해야 하고 \displaystyle C_{i} 증가를 위해서는 게이트 산화막의 두께를 감소시키거나, 고유전율의 산화막을 사용하는 방법 등이 있으며, 공핍 영역의 두께를 증가시켜 \displaystyle C_{d}를 최소화하기 위해서는 채널의 도핑 농도를 감소시킬 필요가 있습니다. |

꼬리 질문 1 GIDL특성은 채널 길이와 상관 없이 발생하는데,왜SCE라고 하는지 설명해 보시오. |

GIDL은 게이트와 드레인이 중첩되는 영역에서 일어나는 현상으로, SCE와 직접적인 관계는 없지만 소자가 미세화되면서 게이트 산화막의 두께가 감소하고 소스와 드레인의 기생 저항 감소를 위한 소스/드레인 도핑 농도는 증가하며, \displaystyle I_{off} 감소를 위해 게이트에 0\text{V}가 아닌 부(Negative) 전압을 인가하는 등 GIDL 측면에서 모두 열화되는 조건이 적용되므로 SCE의 한 종류로 보는 것입니다. 또한 단채널 효과로 인해 \displaystyle I_{off}가 높아진 상태에서 GIDL 전류까지 더해진다면 대기 상태 전력소모가 심각해지기 때문이기도 합니다. |

|

꼬리 질문 2 HCE완화를 위한LDD구조의 원리에 대해 설명하시오. |

LDD(Lightly Doped Drain)는 LDD를 적용하지 않은 기존의 구조에서 전계가 가장 강한 드레인 부근의 드레인 도핑 농도를 감소시키는 방법으로, LDD를 적용한 구조에서 \displaystyle V_{D}가 인가되면 도핑이 낮은 LDD 영역은 공핍 영역의 폭이 넓어지고 이에 따라 전계도 LDD가 끝나는 영역까지 확장됩니다. 인가한 드레인 전압은 LDD를 적용하지 않은 기존 구조와 같으므로, 전계를 적분한(전계 곡선의 하부 면적) 값이 동일해야 합니다. 따라서 LDD를 적용한 경우의 최대 전계는 낮아져야 하는데 충돌 이온화(Impact ionization)는 최대 전계에 대해 지수 함수적으로 비례하므로 열 전자 효과에 대한 최대 전계의 감소 효과는 매우 탁월하다고 볼 수 있습니다. 그러나 LDD 영역은 기존 \displaystyle n^{+} 고농도 영역 대비 저농도로 인해 소스, 드레인 직렬 저항이 증가하는 부작용이 있어 동작 전류(\displaystyle I_{on})의 감소가 불가피하므로, LDD 이온주입 공정은 열 전자 효과에 있어 전계 완화에 의한 소자 신뢰성 개선과 \displaystyle I_{on} 감소에 따른 소자 동작 속도 저하 문제, 이 양자 사이의 타협점을 찾아 적정 조건을 찾는 것이 중요합니다.

|

|

기출문제 풀이

기출문제 ❺

MOSFET의 동작 속도를 개선할 수 있는 방안에 대해 설명하시오.

STEP1 접근 전략

설명형 문제로 난이도는 중상 수준이며 최근 자주 출제되는 문제이다.

단채널 MOSFET에서 캐리어 이동도의 개선 필요성을 설명한다.

압축응력(pMOS, SiGe S/D)과 인장응력(nMOS, SiC S/D 또는 Si_3N_4 박막)을 이용하는 실리콘 격자 변형 기술을 통한 이동도를 개선하는 방법에 대해 설명한다.

STEP2 답안 구조화 TIP

Q MOSFET 동작 속도 개선 방안?

- 밴드 갭, 캐리어의 유효 질량 변화

- 압축응력(pMOS) → SiGe S/D → μ_{hole}↑

- 인장응력(nMOS) → SiC, Si_3N_4 → μ_{electron}↑

STEP3 모범답안

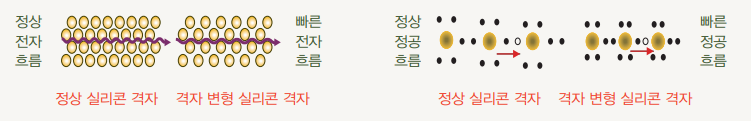

단채널 MOSFET의 캐리어 속도 포화(Velocity saturation) 현상으로 발생하는 이동도 저하에 의한 동작 전류(On-Current) 감소의 대책으로, 채널에 기계적 변형을 주어 변형 실리콘을 사용하는 방법이 있습니다. 실리콘에 기계적 응력(Stress)을 가하면 전자와 정공의 이동도가 변한다는 변형 전위(Deformation potential) 이론에 따르면, 격자 변형 실리콘의 밴드 갭(Band- Gap)과 캐리어의 유효 질량(Effective mass)은 일반 실리콘의 값과 달라집니다. 즉, 이동도의 개선을 위해서 실리콘의 유효 질량을 줄이거나 캐리어를 유효 질량이 좋은 곳으로 이동시키는 것입니다. 전자는 인장응력(Tensile stress)에 의해, 정공은 압축응력 (Compressive stress)에 의해 이동도가 증가하는데, 격자 변형 기술은 다양한 수단을 사용하여 실리콘 결정을 물리적으로 인장 또는 압축하는 기술이며, 캐리어의 이동성을 증가시켜 트랜지스터의 성능을 향상시키는 기술입니다. 예를 들어, 채널에 압축응력을 가하면 pMOS의 정공 이동도가 개선되는데, 실리콘 채널에서 압축 변형을 만들기 위해 소스 및 드레인 영역을 에피택시(Epitaxy) 성장에 의해 실리콘-게르마늄(Si-Ge) 막으로 채웁니다. Si-Ge의 단위 체 적당 원자의 수는 원래 Si 원자와 동일하나 Ge 원자는 Si 원자보다 커, 이에 의한 응력이 만들 어지면 채널을 미는 작용이 일어나 정공의 이동도를 높일 수 있는 것입니다. nMOS의 경우는 트랜지스터 주위에 높은 인장응력의 실리콘 질화막(Si_3N_4) 캡핑(Capping)층을 추가하거나 소스, 드레인에 Si보다 격자 상수가 작은 SiC를 성장시켜 채널에 인장응력을 줌으로써 전자의 이동도를 개선할 수 있습니다.

꼬리 질문 격자 변형이 되면 전자와 정공의 이동도가 높아지는 이유에 대해 설명하시오. |

(그림에서와 같이) 전도대역에서 자유롭게 이동하는 전자가 다수 캐리어로 작용하는 nMOS의 경우, SiC 소스/드레인 또는 Si_3N_4 박막으로부터 인장응력을 받으면 채널 내 실리콘 격자의 공간이 넓어져 전자들이 실리콘 격자와의 충돌이나 전기적인 상호 작용 없이 자유롭게 움직일 수 있습니다. 한편 가전자대역에서 인접 전자가 이동하고 남은 빈 구멍이 다수 캐리어(정공)가 되는 pMOS는 SiGe 소스/드레인 혹은 압축응력을 가진 Si_3N_4 박막으로부터 인장응력을 받으면 격자 간 공간이 좁아져 정공이 빠르게 이동할 수 있으므로 이동도가 커지게 됩니다.

|

|

기출문제 풀이

기출문제 ❻

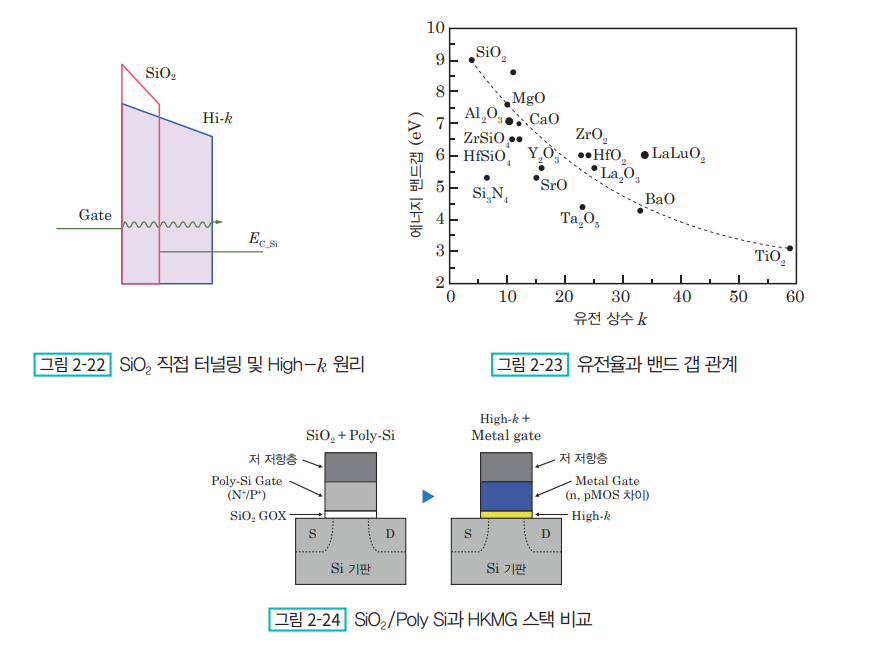

게이트 산화막의 박막화에 따른 누설 전류에 대한 대책을 설명해 보시오.

STEP1 접근 전략

솔루션형으로 난이도는 중상 수준이며, 최신 기술과 관련된 문제이다.

게이트 산화막의 두께를 감소시켜야 하는 당위성에 대해 설명한다.

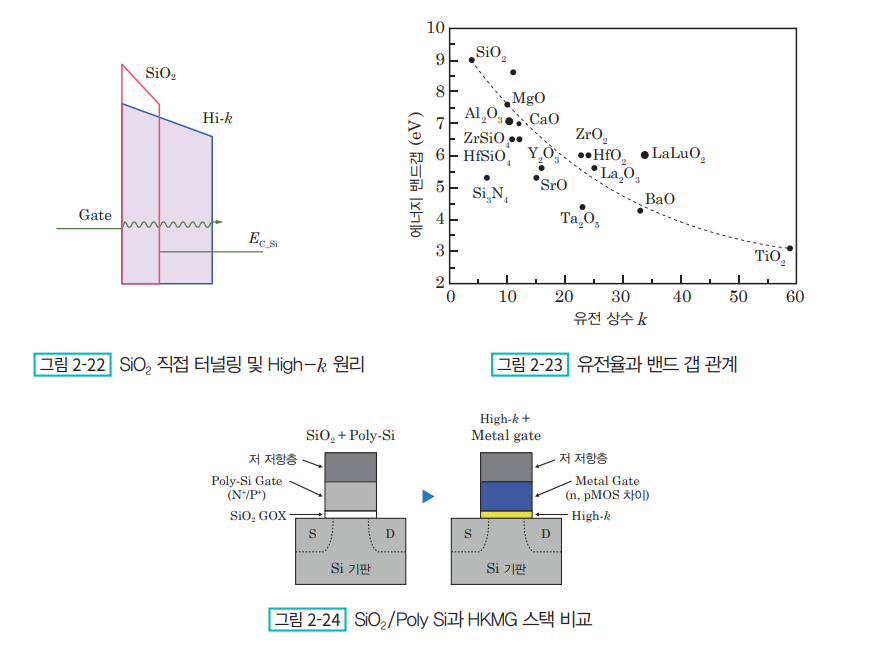

기존 SiO_2 절연막의 두께 감소 시 발생하는 누설 전류 등의 문제와 이 문제의 극복을 위해 High-k 물질이 도입되었음을 설명하고, High-k 물질이 갖추어야 할 요건에 대해 설명한다.

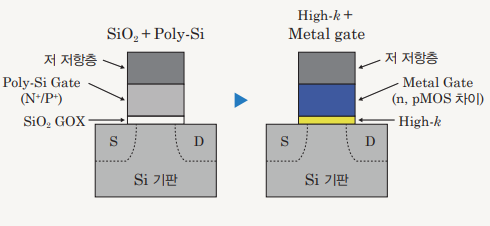

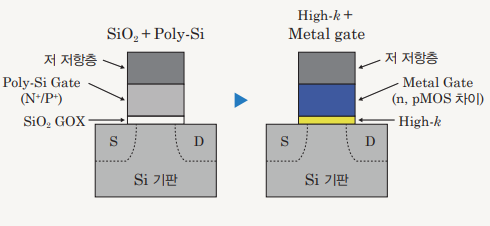

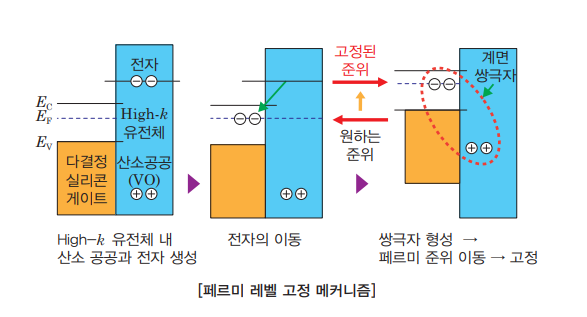

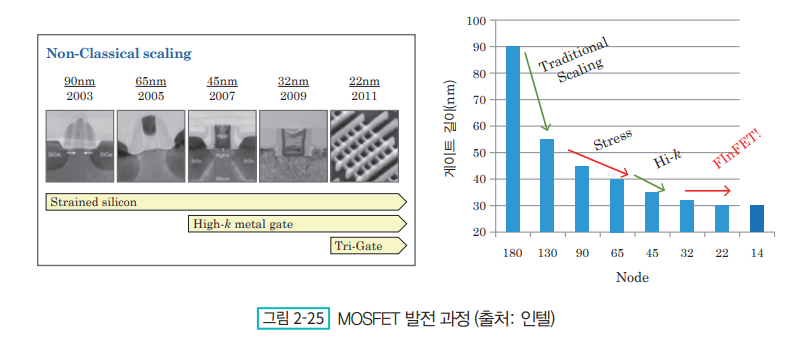

기존의 다결정 실리콘 게이트 전극과 High-k 게이트 산화막을 함께 사용하는 경우의 문제 점을 제시하고, 이에 대한 대안으로 금속 게이트의 도입 필요성 및 효과를 피력한다.

STEP2 답안 구조화 TIP

I_{on} \uparrow, SCE \downarrow \rightarrow T_{GOX} \downarrow \rightarrow GOX 직접 Tunneling \rightarrow 누설 전류 \uparrow

High-k \rightarrow C_{ox} \uparrow \rightarrow EBG \downarrow \rightarrow T_{GOX} \uparrow

Si 반응성 \downarrow, \mu \uparrow, 결함 밀도 \downarrow

Al_2O_3, ZrO_2, HfO_2 \rightarrow ALD

Gate 전극: Poly Si \rightarrow Metal

Poly depletion, \mu \downarrow, V_{Th} Control

Metal gate \rightarrow 공정 Step \uparrow

HKMG \rightarrow I_{off} \downarrow, I_{GOX} \downarrow, I_{on} \uparrow

STEP3 모범답안

동작 전류(I_{On})를 높여 회로의 동작 속도를 향상시키고 단채널 효과를 저감시키기 위해서 는 게이트 절연막의 두께 감소를 통한 채널에 대한 게이트의 제어 능력을 개선할 필요가 있습 니다. 하지만 30Å 이하로 게이트 절연막(SiO_2)을 얇게 하면, 직접 터널링(Direct tunneling)에 의한 게이트 누설 전류가 발생하고 이에 따라 칩의 전력 소비가 급증하며 게이트 절연막의 신뢰성도 담보할 수 없게 됩니다. 이에 SiO_2보다 더 높은 유전 상수(High-k)를 갖는 새로운 물질의 게이트 절연막 도입이 필요하게 되었는데, 통상, High-k 유전체는 SiO_2보다 작은 밴드갭을 가지므로 유전체의 물리적 두께를 증가시키지 않으면 전극 사이에 더 많은 누설 전류가 흐를 수 있습니다. High-k 유전체의 요건은 적정 k값(\sim 30)과 높은 에너지 밴드 갭(5eV 이상)을 가지며, Si과의 반응성이 낮아야 하고 결합 밀도가 낮고 채널에서의 캐리어 이동성의 손실이 최소화되어야 합니다. 이러한 기준을 만족하는 유전체는 Al_2O_3, ZrO_2, HfO_2 등이며 통상 피복 능력이 우수한 원자층 증착(Atomic Layer Deposition, ALD) 공정을 이용합니다. 기존에 사용되었던 다결정 실리콘 게이트 전극을 High-k 유전체와 함께 사용할 경우, 먼저 게이트 전압 인가 시 다결정 실리콘의 공립 영역 형성으로 인해 게이트 산화막의 유효 두께가 증가하여 구동 전류의 열화 문제와 포논 산란에 의한 이동도 감소 문제를 야기할 수 있고 페르미 준위 고정(Fermi level pinning)에 의한 문턱 전압 제어에 심각한 문제를 초래할 수 있습니다. 이러한 문제들을 해결하기 위해 제안된 것이 금속 게이트 전극이지만 nMOS와 pMOS의 적절한 문턱 전압의 제어를 위해 서로 다른 일 함수(Work function)를 갖는 금속을 적용함으로써 공정 단계가 증가하는 문제가 있을 수 있습니다. 이렇게 High-k 물질과 금속 게이트를 합쳐 HKMG(High-k Metal Gate)라고 부르며, 이를 적용 시 I_{off} 및 게이트 산화막 누설 전류의 감소는 물론, I_{on} 또한 20% 이상이 개선되는 결과를 보였습니다.

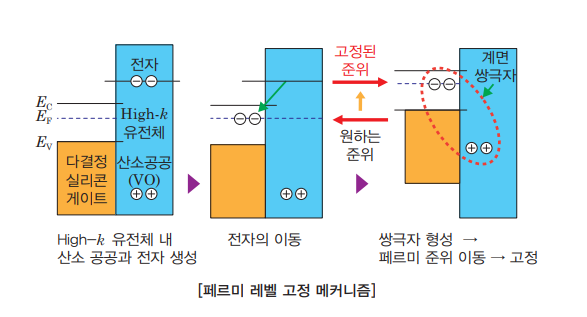

고득점 답안 High-k와 다결정 Si 게이트 사용 시 V_{Th} 제어를 어렵게 하는 페르미 레벨 고정(Fermi level pinning)에 대해 설명한다. |

High-k 유전체 사용 시 다결정 실리콘에서 금속 게이트로 전환하게 된 이유 중 하나는 MOSFET의 문턱 전압 제어의 어려움 때문입니다. Poly Si 게이트의 유효 일 함수(Effective Work Function, EWF)*는 High-k 유전체와 함께 사용될 때 도핑으로 쉽게 바뀌지 않는데, 이는 EWF가 Poly Si 게이트의 페르미 준위 대신 Si-Hf(High-k) 결합에 의해 결정되기 때문입니다. 그 결과, 소자는 실제 범위를 넘어서는 매우 높은 V_{Th}를 갖는데, 이는 Poly Si의 EWF가 Si 전도대 가장자리 근처의 특정 지점에 고정되기 때문이며 이를 페르미 레벨 고정이라고 합니다. 발생 메커니즘은, High-k 유전체 내 결함에 의한 산소 공공(Oxygen vacancy)과 전자가 형성되고 이 전자가 다결정 실리콘 쪽으로 이동함으로써 계면 분극이 생기는데, 이에 따라 페르미 레벨이 고에너지 쪽으로 이동하여 고정된다는 원리입니다. 자유 전자가 풍부한 금속 전극 재료는 이러한 페르미 준위 고정 효과를 완화시킬 수 있습니다. * 금속 고유의 진공 기준의 일 함수가 아닌 금속과 유전체 등의 다른 물질 사이의 상호 관계로부터 수정된(Modified) 일 함수로 정의됨(EWF=ΦM - 산화막 내 고정 전하에 의한 전위 + 계면 쌍극자에 의한 전위).

|

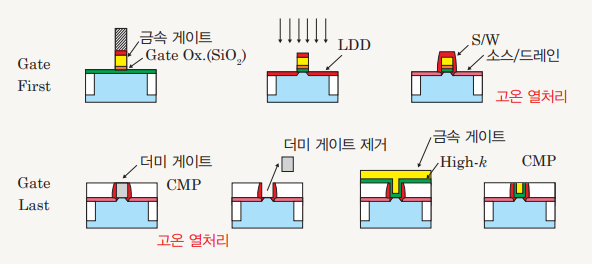

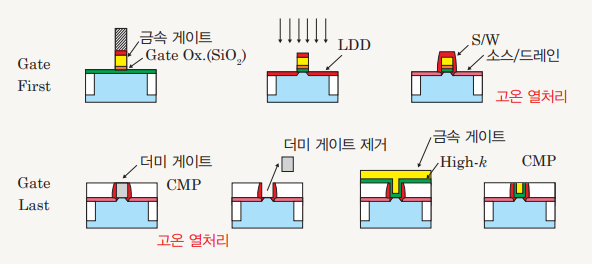

꼬리 질문 HKMG공정에 대해 설명하시오. |

HKMG 공정은 게이트 퍼스트(Gate first) 및 게이트 라스트(Gate last)로 나눌 수 있습니다. 게이트 라스트는 대체 금속 게이트(Replacement metal gate)법이라고도 하며, 두 방식 모두에서 nMOS 및 pMOS 소자에 적합한 문턱 전압을 얻는 것이 어려워 일 함수가 서로 다른 물질을 적용해야 합니다. 게이트 퍼스트 기술에서는 완전한 게이트 스택(Stack)이 게이트 패터닝 전에 형성되므로, 도펀트 활성화를 포함하여 트랜지스터 형성에 필요한 모든 후속 공정의 높은 열 처리량(Thermal budget)을 견뎌야 하는데 고온에 노출되게 되면 게이트 스택을 위한 재료 선택이 제한되는 단점이 있습니다. 게이트 라스트 접근법의 경우, 다결정 실리콘 더미(Dummy) 게이트가 형성되며, 이 더미 게이트를 사용하여 열 처리량이 높은 모든 공정 단계가 수행된 후, 더미 게이트는 제거되고 High-k 금속 게이트 전극으로 교체됩니다.

|

|

기출문제 풀이

기출문제 ❼

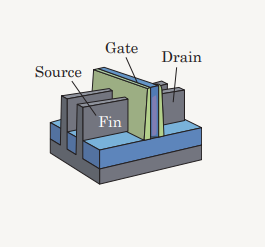

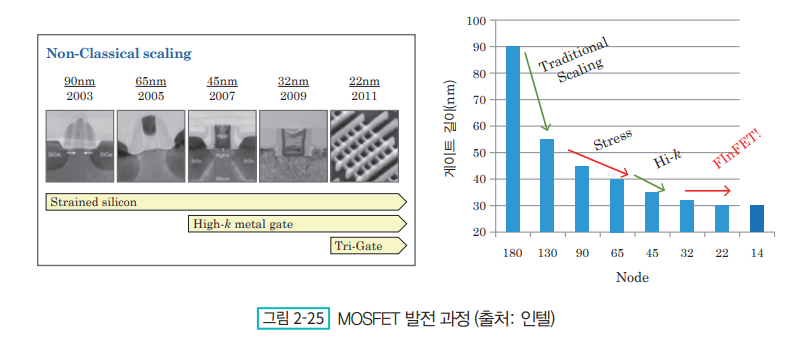

FinFET에 대해 설명하시오.

STEP1 접근 전략

STEP2 답안 구조화 TIP

Q FinFET?

STEP3 모범답안

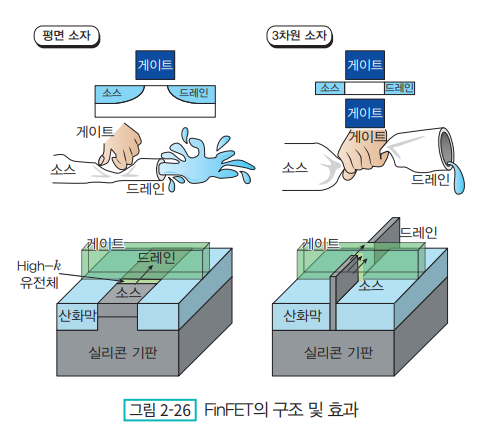

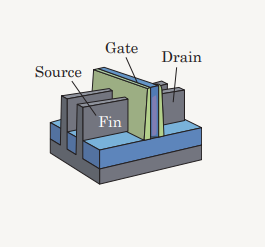

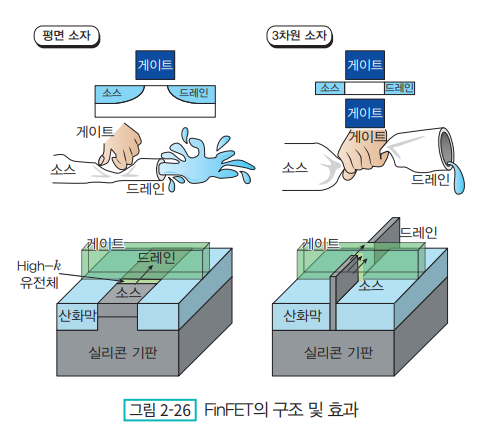

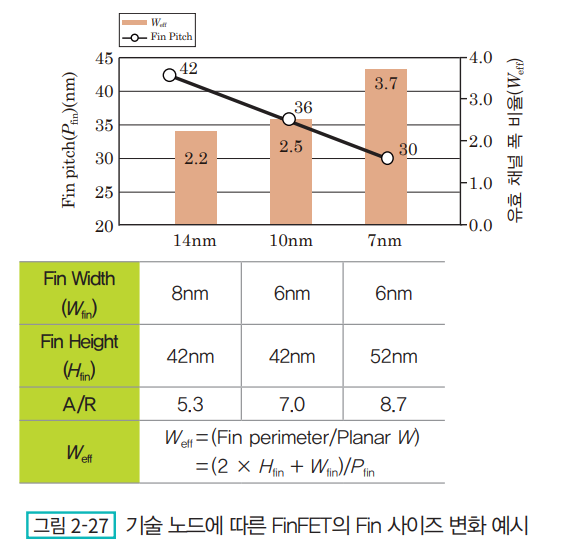

FinFET은 기판으로부터 돌출된 물고기의 등 지느러미 모양과 흡사한 얇은 수직 돌기(Fin)가 채널이 되고, 이 채널의 3면을 게이트가 감싸 채널에 대한 게이트의 높은 제어 능력을 갖게 되었습니다. 이는 2차원 MOSFET의 한계였던 단채널 효과를 감소시킬 수 있는 3차원 구조의 MOSFET으로, Fin의 높이가 소자의 폭이 되므로 동일 평면적에서 2차원 소자 대비 전류 구동 능력도 증가되는 장점이 있습니다. 또한 FinFET은 우수한 단채널 효과로 채널 도핑을 낮출 수 있어 캐리어의 이동도 개선 및 도펀트 수의 변동에 따른 문턱 전압(V_{Th})의 산포도 개선할 수 있습니다.

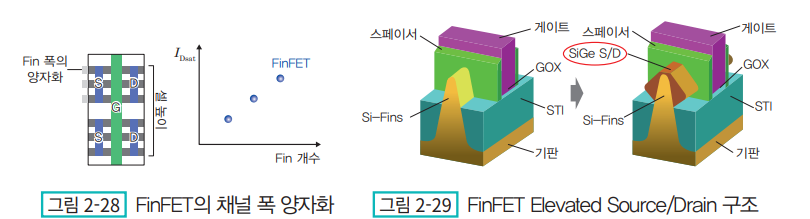

그러나 미세화에 따른 Fin의 폭과 높이의 산포에 의한 문턱 전압(V_{Th})의 변동폭(\Delta V_{Th}) 감소를 위해 Fin 패턴을 형성할 때 매우 정밀한 공정 제어가 필요하고, 게이트 스페이서(Spacer)와 같은 식각에 있어 고에너지 이온에 의한 손상을 최소화하면서 Fin 코너의 잔류물을 말끔히 제거해야 하므로 우수한 선택비를 갖는 식각 공정이 요구됩니다. 3차원 Fin 접합 형성 시의 등방성 도핑을 위한 플라즈마 도핑 등의 요소 공정 기술도 필요합니다. 또한 채널 폭이 항상 Fin 높이의 배수가 되어, 소자의 유효 채널 폭이 양자화되어 발생하는 설계의 자유도 저하 문제는 Fin 피치(Pitch)의 감소로 대응하고 있으며, 이 외에 Fin의 두께가 얇아 소스/드레인의 기생 저항이 증가되는 문제는 부상(Elevated) 소스, 드레인 구조를 채택하여 극복하고 있습니다.

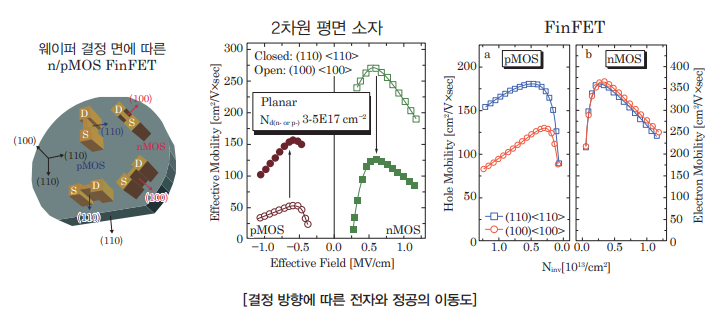

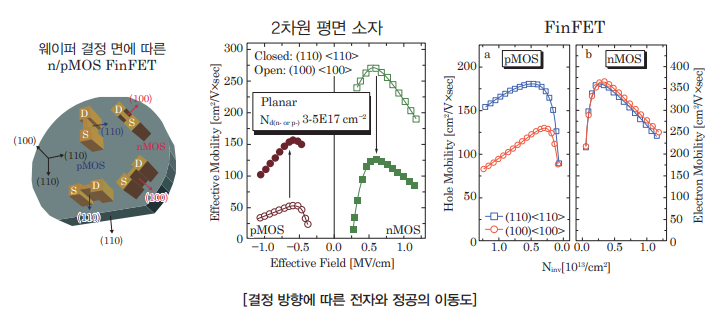

고득점 답안 FinFET의 웨이퍼 결정면에 따른 nMOS 및 pMOS의 특성 차이에 대해 설명한다. |

FinFET은 (100)면의 웨이퍼를 사용하는 경우, (100) 방향의 플랫 존(Flat zone)에 수직이거나 수평인 핀의 측면(Sidewall)은 (110)면이 됩니다. 평면 소자의 각 면에서는 전자와 정공의 이동도가 달라 nMOS와 pMOS 간의 성능 차이가 발생하는데, FinFET의 pMOS는 원래 유리한 방향이고 nMOS에서는 이동도에 거의 차이가 없어 전체적으로 큰 문제가 없는 것으로 보고되었습니다. 평면 소자에서 결정면에 따라 많은 차이를 보이던 전자의 이동도가 FinFET에서 다른 양상을 보이는 이유는, 전원 전압의 감소에 따른 낮아진 전계 및 도핑 농도 감소로 인한 전자와 불순물 간의 산란(Scattering)이 감소되었기 때문인 것으로 알려져 있습니다.

|

꼬리 질문 채널 3면을 게이트가 감싸는 구조인 FinFET에서, 게이트 제어 능력이 좋아지는 이유에 대해 설명해 보시오. |

물이 흐르는 고무관을 위에서 누르는 것 대신 손으로 움켜쥐었을 때 물의 흐름을 더 잘 제어할 수 있는 원리에 비유할 수 있습니다. 좀 더 정량적으로는 게이트 전압(V_G)에 의해 얇은 Fin 채널이 완전 공핍되면서 채널의 공핍 정전 용량(C_d)이 무시할 수 있을 만큼 감소하여 채널 하부의 누설전류 경로를 원천 차단함으로써 문턱 전압 이하 스윙(Sub-Threshold Swing, SS), 누설 전류(I_{off}) 및 DIBL 등의 SCE가 대폭 감소하기 때문입니다. |

|

핵심 이론 정리

1. MOS 커패시터(Metal-Oxide-Semiconductor Capacitor, MOSCAP)

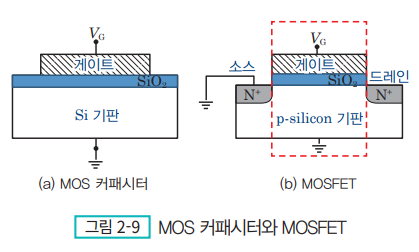

(1) MOS 커패시터의 구조

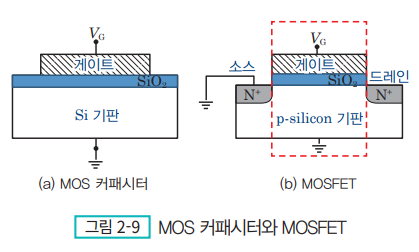

MOS 커패시터는 금속 산화막 반도체 커패시터를 의미하는 말로서, MOSFET의 가장 핵심적인 부분이다. MOS 커패시터의 형태는 [그림 2-9(a)]와 같으며, 마치 [그림 2-9(b)]의 게이트(Gate), 소스(Source), 드레인(Drain), 기판(Body) 등 4단자 소자로 구성된 MOSFET에서 중앙부만을 따로 떼어낸 2단자 소자의 모습이다.

(2) MOS 커패시터의 동작 원리

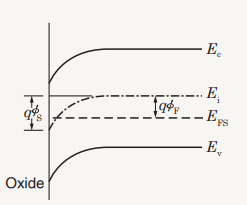

금속(\Phi_m)과 반도체(\Phi_s)의 일 함수(Work function)가 동일하고 실리콘 산화막(SiO_2)의 계면 전하가 없는 이상적인 p형 실리콘 기판의 n형 MOSCAP을 예로 들어, 에너지 밴드 다이어그램을 통한 MOSCAP의 동작을 설명한다. 편의를 위해 진공 준위(Vacuum level)가 아닌 산화막의 전도대를 에너지 밴드의 기준으로 하여 수정된 \Phi_m과 \Phi_s, 그리고 실리콘의 전자 친화도(Electron affinity, \chi_s)를 정의하고 진성 에너지 준위(E_i)와 페르미 준위(E_{Fs})의 차이를 페르미 준위(\phi_F)로, Bulk 실리콘 내의 진성 준위(E_{ib})와 실리콘 표면에서의 진성 준위(E_{is})의 차(E_{ib} - E_{is})/q를 표면 전위(\phi_s)로 명명한다.

① 평탄 밴드 상태(Flat band mode)

① 평탄 밴드 상태(Flat band mode)

[그림 2-10(a)]와 같이 게이트(V_G)에 0V를 인가한 상태에서 금속과 반도체의 페르미 준위(E_{Fm}, E_{Fs})를 일치시켜 \Phi_m과 \Phi_s를 동일하게 맞춰 에너지 밴드를 평탄하게 만드는 조건을 평탄 밴드 조건(Flat band condition) 이라 한다.

② 축적 상태(Accumulation mode)

V_G에 음의 전압을 인가하면 [그림 2-10(b)]와 같이 E_{Fm}이 가해준 전압(qV)만큼 증가하고, 고유 특성인 q\Phi_m값의 유지를 위해 금속 쪽에 접한 산화막 E_c도 qV만큼 상승하게 된다. 인가한 전압 V는 게이트 산화막(V_{Ox})과 실리콘(\phi_s)에 나누어 걸리게 되고, 기판과 접한 산화막의 E_c가 \phi_s만큼 상승하게 되어 역시 고유 특성인 실리콘의 전자 친화도(q\chi_s)를 유지하기 위해서는 실리콘 표면의 에너지(실리콘 표면과 벌크 내의 에너지 차이)가 q\phi_s만큼 위쪽으로 휘게 된다. 이때 전체 MOSCAP에는 전류가 흐르지 않으므로 페르미 준위는 위치에 따라 일정하고 에너지 밴드의 변화는 표면에서만 일어나므로 기판 내부(Bulk)에서의 에너지 밴드는 평탄 상태와 동일하게 유지된다. 이렇게 에너지 밴드의 휨이 발생하면 실리콘 표면은 E_{Fs}와 E_v의 차이가 감소하여 정공인 양 전하가 표면에 축적되는 축적(Accumulation) 상태가 되며 이때의 실리콘 표면 전위는 \phi_s < 0의 값을 갖는다(\because E_{ib} < E_{is}). 이러한 현상은 평탄 조건에서 V_G에 음의 전압을 인가하면, 게이트에는 음전하(Q_m)가 생성되고 이와 극성이 반대이면서 크기가 같은 p형 기판의 다수 캐리어인 정공이 양전하(Q_{acc})로서 반도체 표면에 유기되는 전하 모델로도 설명이 가능하다.

③ 공핍 상태(Depletion mode)

양의 V_G가 인가되면 [그림 2-10(c)]와 같이 E_{Fm}이 가해준 전압(qV)만큼 내려가고 고유 특성인 q\Phi_m값의 유지를 위해 금속 쪽에 접한 산화막 E_c도 qV만큼 하강하게 된다. 역시 인가한 전압 V는 게이트 산화막(V_{Ox})과 실리콘(\phi_s)에 나누어 걸리게 되고, 산화막의 E_c가 \phi_s만큼 감소하게 되어 고유 특성인 실리콘의 전자 친화도(q\chi_s)를 유지하기 위해서는 실리콘 표면의 에너지가 q\phi_s만큼 아래로 휘게 된다. 이렇게 에너지 밴드의 휨이 일어나면 실리콘 표면은 E_{Fs}와 E_i의 차이가 감소하여 정공(캐리어)이 없고 음의 억셉터 이온만 공간 전하(Space charge) 형태로 존재하는 공핍(Depletion) 상태가 되고, 이때의 표면 전위는 0 < \phi_s < \phi_F 범위이다. 이 역시 전하 모델로 설명 가능하다. V_G에 양의 전압을 인가하면 게이트에 양전하(Q_m)가 생성되고, 이에 대응하는 음전하(Q_d)가 실리콘 표면에 유기된다. 이때 음전하는 p형 반도체의 다수 캐리어인 정공이 게이트의 양전하와의 척력에 의해 실리콘 표면에서 밀려나고, 그 자리에 남은 억셉터 음이온(N_A^-)에 의한 공간 전하(Space charge)이다.

④ 반전 상태(Inversion mode)

큰 양의 V_G가 인가되면 [그림 2-10(d)]와 같이 공핍 상태보다 실리콘 표면의 에너지 밴드가 아래로 더 휘게 되는데, 이때 E_i가 E_{Fs}보다 아래로 내려가 \phi_s > \phi_F 상태가 되면 실리콘 표면이 n형 반도체로 반전되는 반전(Inversion) 상태가 되고 표면 에너지 q\phi_s가 q\phi_F의 2배가 되는 순간을 강 반전 상태라 하여 이때의 게이트 전압을 문턱 전압(Threshold voltage, V_{Th})으로 정의한다. 전하 모델 측면에서는 공핍 상태에서 게이트에 인가하는 양의 전압을 계속 증가시키면, p형 기판의 소수 캐리어인 전자가 게이트의 양전하에 대응하기 위해 표면에 유기된다. 따라서 p형 표면은 이제 정공보다 전자의 농도가 더 높아져 원래 p형 반도체이던 표면이 n형으로 바뀌게 된다.

2. 문턱 전압(Threshold voltage)

(1) 문턱 전압의 정의 및 고찰

문턱 전압(V_{Th})은 강 반전 상태를 만들기 위해 게이트에 인가되는 전압(\phi_s = 2\phi_F을 말하며, ① 평탄대 전압(V_{FB}), ② 공핍 영역 전하 수용 전압(Q_d/C_i), ③ 반전층 형성 전압($2\phi_F$)의 세 항으로 구성되고 다음과 같은 관계를 가진다. 물리적으로는 채널에 캐리어를 만들어내기 위한 최소한의 전압을 의미한다.

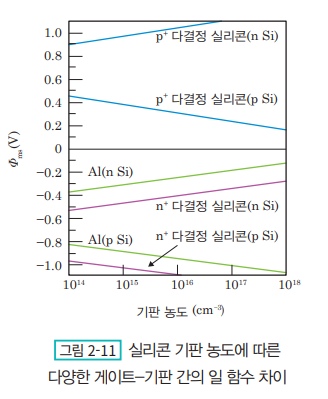

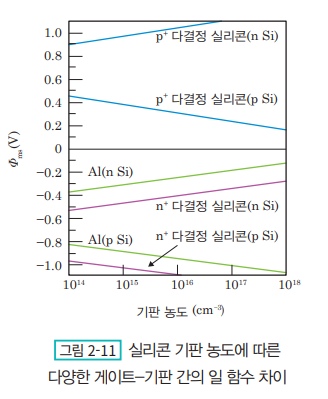

V_{Th} = V_{FB} - Q_d/C_i + 2\phi_F = (\Phi_{ms} - Q_i/C_i) - Q_d/C_i + 2\phi_F

먼저 산화막 계면 전하(Q_i)와 함께 평탄대 전압(V_{FB})을 구성하는 일 함수의 차(\Phi_{ms})는 [그림 2-11]과 같이 p^+ 다결정 실리콘과 같은 경우(\Phi_{ms} > 0)를 제외하면 n, p 채널 소자에 대해 모두 음의 값을 가진다. 두 번째 항의 산화막 계면 전하 또한 양의 유효 등가 전하(Q_i)로 정의하였으므로 전체적으로는 역시 음이다. 세 번째 항인 공핍 영역의 전하(Q_d)는 p형 기판(n-채널)의 억셉터 이온의 경우에 양의 값을 가지고, n형 기판(p-채널)의 도너 이온의 경우에는 음의 값을 가지게 된다. 마지막으로 강 반전에 필요한 전압 2\phi_F의 \phi_F는 (E_i - E_{Fs})/q로 정의되는 항으로, n 채널 소자의 경우 양의 값을 가지고, p 채널의 경우 음의 값을 갖는다. 한편, 문턱 전압 수식에서 Q_i/C_i를 제외한 모든 항목은 도핑 농도의 함수로서, 이 중 일 함수의 차(\Phi_{ms})와 반전층 형성 전압(\phi_F)은 농도 변화에 비교적 둔감한 편이고, 농도 변화에 가장 민감한 항목인 공핍 영역의 전하(Q_d)는 도핑 농도의 제곱근에 비례한다. 최근 산화 공정 기술의 발전에 따라 Q_i 값 자체가 많이 감소하였고, 산화막 두께의 감소로 C_i 값도 증가하여 Q_i/C_i 항은 거의 무시할 수 있게 되었다.

함수의 차(\Phi_{ms})와 반전층 형성 전압(\phi_F)은 농도 변화에 비교적 둔감한 편이고, 농도 변화에 가장 민감한 항목인 공핍 영역의 전하(Q_d)는 도핑 농도의 제곱근에 비례한다. 최근 산화 공정 기술의 발전에 따라 Q_i 값 자체가 많이 감소하였고, 산화막 두께의 감소로 C_i 값도 증가하여 Q_i/C_i 항은 거의 무시할 수 있게 되었다.

(2) 문턱 전압(VTh)의 제어 방법

(2) 문턱 전압(VTh)의 제어 방법

먼저 ① 적정한 일 함수를 갖는 게이트 물질을 선택하여 문턱 전압(V_{Th})의 조절이 가능하다. ② 문턱 전압(V_{Th})은 기판 농도에 의존하므로, 기판 계면에 정확한 깊이(에너지)와 농도(도즈)의 도핑을 위한 이온주입 공정을 적용함으로써 문턱 전압(V_{Th})을 제어할 수 있다. 또한 ③ 게이트 산화막 두께(T_{ox}) 또한 문턱 전압(V_{Th})에 영향을 미치므로 고려 대상이다. 마지막으로 ④ 기판에 인가하는 바이어스에 의한 문턱 전압 제어 방법이 있다. 이는 기판에 역방향 바이어스를 인가하면 소스와 동일 전압(V_{BS} = 0V) 인가할 때보다 실리콘 표면(채널)의 공핍 영역이 확장되고, 이 때문에 증가한 공핍 영역의 전하를 보상하기 위해, 게이트 전압이 더 필요하게 되어 문턱 전압의 상승을 가져오게 되는 원리이다.

3. MOSFET의 동작 원리

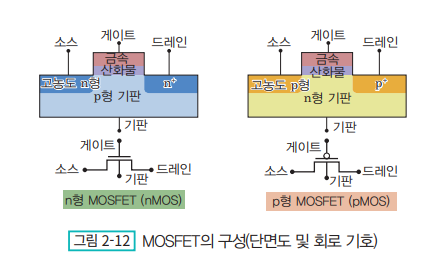

(1) MOSFET의 구조

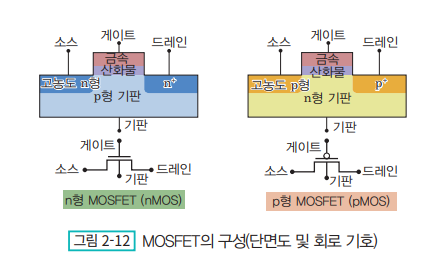

MOSFET은 금속 산화막 반도체 전계효과 트랜지스터(Metal-Oxide-Semiconductor Field Effect Transistor)의 약자로서, [그림 2-12]와 같이 MOS 커패시터의 양단에 2단자(소스, 드레인)를 추가하여, 게이트(Gate), 기판(Substrate), 소스(Source), 드레인(Drain)의 4단자로 구성되며 주로 증폭기 또는 스위치 등으로 사용된다. MOSFET은 기판의 종류와 채널에 따라 n형 MOS트랜지스터(nMOS)와 p형 MOS트랜지스터(pMOS)가 있다.

(2) MOSFET의 동작 원리(nMOS 기준)

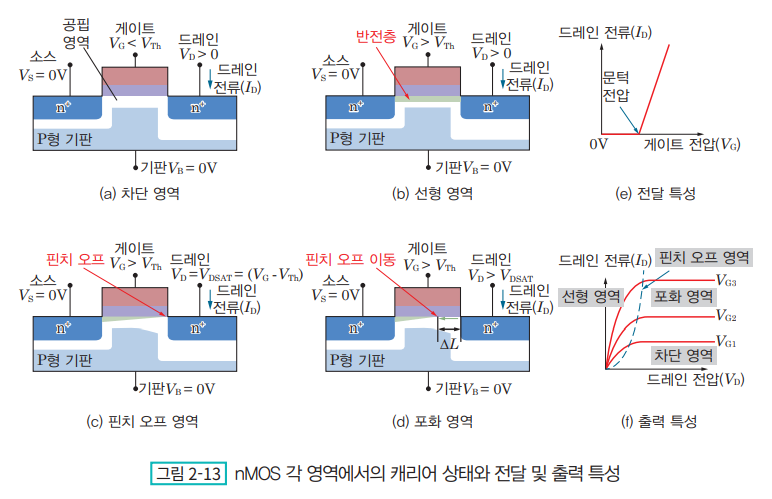

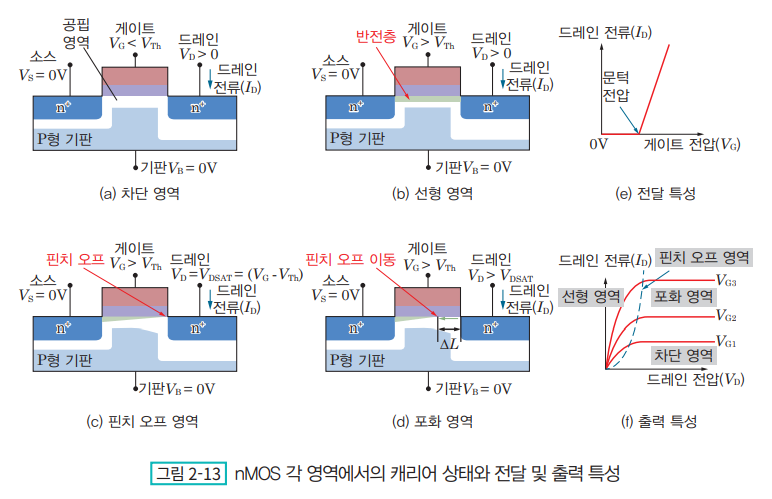

MOSFET의 동작은 게이트와 드레인에 인가되는 전압에 따라 3가지 영역으로 나뉜다.

① 차단 영역(Cut-Off region) (V_G \le V_{Th})

[그림 2-13(a)]와 같이, 게이트에 문턱 전압(V_{Th}) 이하의 전압(V_G \le V_{Th})이 인가되면 채널은 공핍 또는 약 반전 상태가 되어, 드레인에 전압(V_D)이 인가되더라도 소스에서 드레인으로의 전자 이동이 일어나지 않는다. 이렇게 드레인 전류(I_D)가 흐르지 않는 영역을 차단 영역(Cut-Off region)이라고 한다.

② 선형 영역(Linear region) (V_G > V_{Th}, V_D < V_G - V_{Th})

[그림 2-13(b)]와 같이 V_G > V_{Th}면서 V_D < V_G - V_{Th}인 경우, 강 반전 상태가 되어 채널이 형성되고 소스에서 드레인으로의 전자 이동이 일어나 드레인 전류가 흐르게 된다. 이때 V_D가 낮아 채널에 미치는 영향이 미미하여 반전층(채널)은 소스와 드레인 사이에서 저항의 역할을 하게 되므로, I_D가 드레인 전압에 대해 선형적으로 흐르게 되고 이 영역을 선형 영역(Linear region)이라 한다. 이때의 I_D는 다음과 같다.

I_D = (W/L) \cdot \mu_n \cdot C_{ox}[(V_G - V_{Th})V_D - 1/2V_D^2]

(W: 채널 폭, L: 채널 길이, \mu_n: 전자 이동도, C_{ox}: 게이트 산화막 정전 용량)

* 핀치 오프(Pinch-Off) 현상 (V_G > V_{Th}, V_D = V_{DSAT} = V_G - V_{Th}) 역시 V_G > V_{Th}인 상황에서 V_D가 점차 증가하여 V_G - V_{Th}와 같아지면 [그림 2-13(c)]와 같이 드레인 부분의 채널의 전위가 V_G - V_{Th}(\le V_{Th})가 되면서 V_G에 의해 생성되었던 채널이 사라지게 되는 핀치 오프(Pinch-Off) 현상이 발생하게 되는데, 이때 V_G - V_{Th}와 동일하게 되는 V_D를 포화 드레인 전압(Saturation drain voltage, V_{DSAT})이라고 하며 이 값은 V_G의 증가에 따라 증가한다.

③ 포화 영역(Saturation region) (V_G > V_{Th}, V_D > V_{DSAT})

포화 영역은 핀치 오프 영역 상태에서, [그림 2-13(d)]와 같이 V_D가 더 증가해 V_{DSAT} 이상이 된 상황이다. 이 상황에서는 핀치 오프되는 지점이 드레인에서 소스 쪽으로 계속 밀리며 I_D가 더 이상 V_D에 의존하지 않고 일정하게 포화된다. 이는 핀치 오프 이후에 V_D를 높여 핀치 오프 지점이 소스 쪽으로 이동하더라도 핀치 오프 지점과 소스 간 전위차는 V_{DSAT}로 유지되고 장 채널(Long channel) MOSFET에서는 핀치 오프 지점과 드레인 사이의 거리(\Delta L)는 전체 채널의 길이 대비 매우 짧으므로 V_G에 의해 생성되어 이동하는 전자의 양은 같고, 핀치 오프 지점과 드레인 사이에 걸리는 전압(V_D - V_{DSAT})은 단순히 핀치 오프 지점까지 도달한 전자를 드레인 쪽으로 끌어당기는 역할만 하게 되어 전체 전류의 양이 일정하게 유지되기 때문이다. 이 영역에서의 I_D 식은 다음과 같다.

I_D = (W/2L) \cdot \mu_n \cdot C_{ox}[(V_G - V_{Th})^2] = (W/2L) \cdot \mu_n \cdot C_{ox} \cdot V_{DSAT}^2

4. 소자 미세화의 장애물-단채널 효과(Short Channel Effect, SCE)

트랜지스터의 미세화(Scale-Down)는 집적도 증가를 통한 원가 절감은 물론, 저전력화와 고속화와 같은 성능의 향상을 도모하기 위해 꾸준히 진행되어 왔다. 그러나 트랜지스터 크기의 미세화 속도에 비해 사용되는 전원 전압의 감소는 그에 미치지 못해 소자 내부의 전계가 증가하게 되어 대표적으로 채널 길이가 소스 및 드레인 pn 접합의 공핍층 폭에 비견될 수 있을 만큼 작아졌을 때 발생하는 다음과 같은 다양한 단채널 효과(Short Channel Effect, SCE)로 인해 소자 미세화에 장애가 되고 있다.

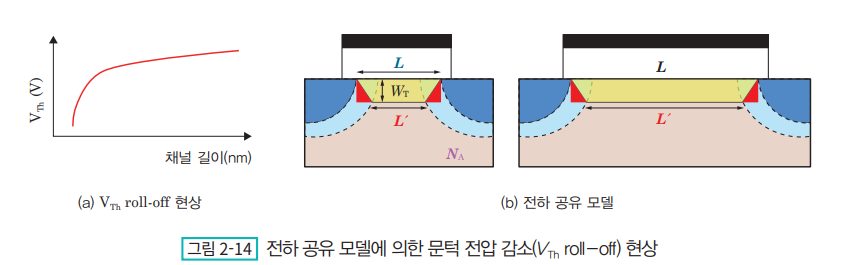

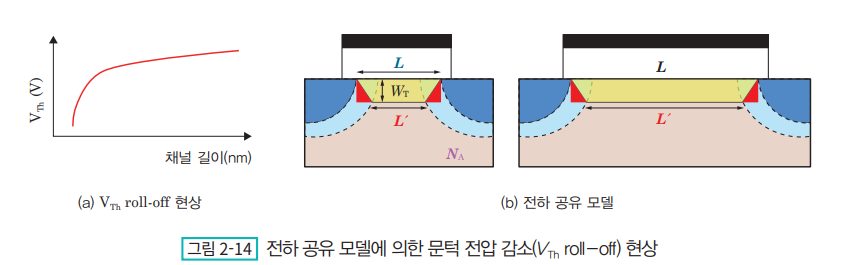

(1) 문턱 전압 감소 현상(V_{Th} roll-off)

V_{Th} roll-off는 [그림 2-14(a)]와 같이 채널 길이가 짧아짐에 따라 문턱 전압이 낮아지는 현상을 말한다. 이는 V_{Th}(= V_{FB} - Q_d/C_i + 2\phi_F)를 구성하는 공핍층 전하 수용 전압(Q_d/C_i)과 관계되는데, [그림 2-14(b)]의 삼각형 영역은 소스와 드레인에 의해 만들어진 공핍 영역 전하에 영향을 받고 있다. 장채널에서는 공핍 영역 전하에 대한 영향(삼각형 영역)이 전체 공핍 영역 전하량에 비해 무시할 수 있는 수준이지만, 채널의 길이가 감소함에 따라 삼각형 영역의 공립 영역 전하에 대한 영향이 상대적으로 더 커지게 되므로 이를 무시할 수 없게 된다. 이러한 효과를 전하 공유(Charge sharing) 현상이라고 한다. 이로 인해 최대 공립 영역을 형성하기 위해 산화막에 인가해 주는 게이트 전압이 감소하게 되고 이것이 바로 문턱 전압의 감소로 나타나는 것이다.

(2) 드레인 유기 장벽 감소(Drain Induced Barrier Lowering, DIBL)

드레인 전압에 의한 장벽 저하 효과는 소스에서 드레인 쪽으로의 전자 이동을 위해 넘어야 하는 내부 장벽의 모양에 의존한다. [그림 2-15(a)]와 같이 드레인 전압(V_D) 및 게이트 전압(V_G)이 0V인 경우에는 내부 전위 장벽이 존재하는데 이상적으로 게이트 전압은 전자의 이동을 위해 내부 전위 장벽을 낮추는 유일한 전압이어야 한다. 그러나 [그림 2-15(b)]와 같이 채널이 짧아지고 V_D이 증가하게 되면, 공핍 영역이 소스와 채널 사이의 전위 장벽에 영향을 미치는 지점까지 확장된다. 궁극적으로 V_G가 아닌 V_D에 의해 채널과 소스 간의 내부 전위 장벽이 낮아지고, 이로 인해 [그림 2-15(c), (d)]와 같이 I_D의 증가로 문턱 전압(V_{Th})이 감소되는 현상이 발생한다. 이를 드레인 유기 장벽 감소(Drain Induced Barrier Lowering, DIBL)라 한다.

(3) 펀치 쓰루(Punch-Through)

[그림 2-16(a)] 및 [그림 2-16(b)]와 같이, V_D 인가 시에 드레인 공핍 영역이 소스 공핍 영역과 만나 게이트의 제어를 전혀 받지 못하는 영역이 생긴다. 그렇게 되면 실리콘 표면이 아닌 하부에 전류 전도 경로가 형성되어 드레인에서 소스 쪽으로 [그림 2-16(c)]와 같은 큰 전류가 흐르는 펀치 쓰루(Punch-Through) 현상이 발생한다. 앞서 설명한 DIBL 현상이 심화된 경우로 볼 수 있으며, 대책으로는 소스, 드레인 접합 깊이(Junction depth, X_j)의 감소와 펀치 쓰루가 발생하는 깊이에서의 기판 농도 증가 등의 방법이 있다. 이 중 기판 농도 증가를 위해, [그림 2-16(d)]와 같이 적정 깊이를 목표로 전체적으로 도핑 농도를 증가시키는 펀치 쓰루 방지 이온주입(Punch-Through Stop ion implant, PTS)이나, [그림 2-16(e)]와 같은 후광 이온주입(Halo ion implantation) 방법을 사용한다. V_D가 증가하면 소스와 드레인 접합 아래 모서리의 공핍 영역이 확장되는데, 후광 이온주입은 이 영역의 농도를 올려 공핍 영역의 확장을 억제하는 원리이다.

(4) 속도 포화(Velocity saturation)

캐리어의 속도는 [그림 2-17(a)]와 같이 전계에 비례(v = μE, μ: 캐리어 이동도)하여 증가하다가, 강 전계(10^4V/cm 이상)가 되면 캐리어의 평균 열적 속도(v_{sat}, 전자의 경우 10^7cm/s) 부근에서 속도가 포화되는 모습을 보인다. 이는 캐리어가 격자와의 산란 등의 상호 작용으로 에너지를 잃어 속도가 더 이상 증가하지 않는 현상으로, 핀치 오프(Pinch-Off) 이전에 I_D가 포화되어 버려 더 이상 증가하지 않는 원리이다. 이를 속도 포화(Velocity saturation)라 하며 실리콘 격자 변형 기술(Strained silicon) 등의 방법으로 대응하고 있다.

(5) 게이트에 의한 드레인 누설 전류(Gate Induced Drain Leakage, GIDL)

오프(Off) 상태의 MOSFET에서 게이트와 드레인 간의 전압 차이가 큰 경우는, nMOS를 기준으로 봤을 때, V_G에 0V 또는 음의 전압이 인가되고, V_D에는 양의 전압이 걸리는 상황에 해당한다. 이 경우에는 [그림 2-18(a)]와 같이 드레인 쪽의 페르미 준위가 내려가 드레인 표면에서의 에너지 밴드가 아래로 휘게 되고, 게이트와 드레인이 서로 중첩되는 드레인의 표면에는 전자가 표면으로부터 밀려나 공핍 영역이 형성된다. 드레인은 고농도로 도핑되므로 이 공핍 영역은 두께가 매우 얇다. 가전자대의 전자는 이 얇아진 밴드를 터널링(Band To Band Tunneling, BTBT)하여 전도대로 이동해 양전압이 인가된 드레인으로 빠져나가고, 가전자대에 생성된 정공은 가장 전위가 낮은 기판으로 이동하여 [그림 2-18(b)]와 같이 드레인에서 기판으로의 누설 전류가 발생하게 된다. 이를 게이트에 의한 드레인 누설 전류(Gate Induced Drain Leakage, GIDL)라 한다. 이를 개선하기 위해 다음과 같은 전계 완화 방법이 사용된다.

PN 접합 시 드레인의 농도를 경사지게(Graded junction) 형성시키는 방법

게이트 폴리 재산화(Gate poly re-oxidation): 게이트 식각 후 얇은 산화막을 성장시키고, 게이트 양 끝단의 산화막 두께를 증가시키는 방법

일 함수(Work function) 조절을 위한 게이트 물질 변경(DRAM Cell Tr 또는 HKMG 구조)

동일 게이트-드레인 중첩(Overlap)의 경우, 저농도 도핑 드레인(LDD, Lightly Doped Drain) 구조 사용

(6) 열 캐리어 효과 (Hot Carrier Effect, HCE*)

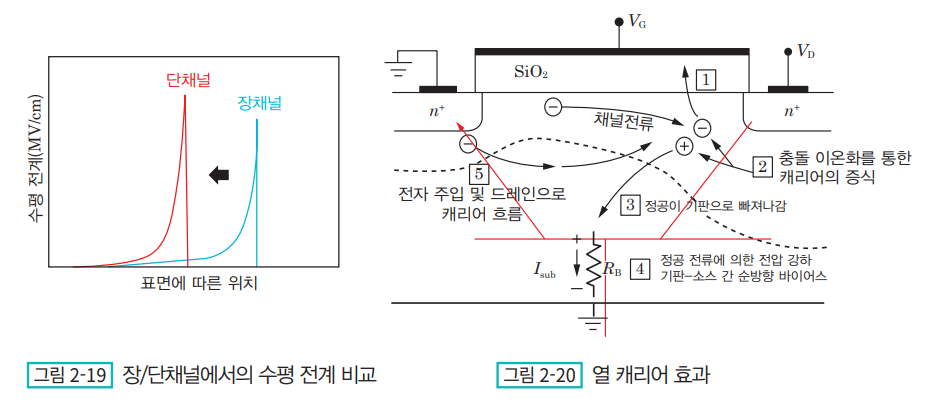

[그림 2-19]와 같이 동일 V_D에 대해 MOSFET의 채널 길이가 짧아지면, 드레인 근처에서 발생하는 채널 방향의 전계는 더욱 증가하게 되고 소스에서 드레인으로 움직이는 전자는 이 전계에 의해 높은 에너지를 받게 된다. 이때의 전자를 열 전자(Hot electron)라 한다. 열 전자는 [그림 2-20]의 ①번 과정과 같이 V_G에 이끌려 SiO_2로 주입되어 게이트 전류를 형성하거나, 게이트 산화막에 포획되어 문턱 전압(V_{Th})의 상승을 초래하게 된다. 이러한 현상을 채널 열 전자 주입(Channel Hot Electron(CHE) injection)이라 한다.

또한 열 전자는 [그림 2-20]의 ②번 과정과 같이 실리콘 격자와 충돌해 실리콘 원자를 이온화시킴으로써 전자-정공 쌍을 생성하는 충돌 이온화(Impact ionization)를 일으킨다. 이렇게 생성된 전자는 에너지를 받아 다시 충돌 이온화 과정을 반복하면서 전자와 정공이 대량 생성되고, 이들 중 전자는 드레인으로, 정공은 기판으로 빠져 나가면서(③) 기판 전류(I_{sub})를 형성한다. 이때 형성된 기판 전류는 기판의 저항(④)으로 인해 기판 내에 전위차를 발생시키고 접지되어 있는 소스보다 기판의 전위가 더 높아져 소스와 기판이 순방향 PN 접합 조건이 된다. 역방향으로 바이어스되어 있는 기판과 드레인은 서로 맞물려 기생 바이폴라 트랜지스터 동작을 하고 스냅 백(Snap-Back) 및 CMOS 래치-업(Latch-Up) 등의 의도하지 않은 많은 전류(⑤)가 흐르는 불량을 초래한다. 이를 드레인 눈사태 열 캐리어 주입(Drain Avalanche Hot Carrier(DAHC) injection)이라 하며 CHE 주입과 함께 통틀어 열 캐리어 효과(Hot Carrier Effect, HCE)라고 한다. 이러한 열 캐리어 효과에 대한 대책으로, 저농도 도핑 드레인(Lightly Doped Drain, LDD) 기술을 적용하여 드레인 부근의 최대 전계를 완화시키는 방법을 적용하고 있다.

* 캐리어 중 정공(Hole)은 전자에 비해 이동도가 낮아 열 정공 발생 확률도 낮고 실리콘과 실리콘 산화막과의 가전자대 에너지 차이가 4.7eV로 전도대역(3.1eV)보다 커 큰 문제가 되지 않았으나, 최근 들어 소자의 미세화가 거듭됨에 따라 pMOS에서의 열 정공 효과에 대한 연구 및 대책들이 나오고 있다.

5. 실리콘 격자 변형(Strained silicon) 기술 (이동도 촉진제(Booster))

단채널 MOSFET에서는 캐리어 속도 포화(Velocity saturation) 현상으로 캐리어의 이동도가 저하되고, 이로 인해 동작 전류(I_{on})의 감소가 발생한다. 이에 대한 대책으로 채널에 기계적 변형을 주는 실리콘 격자 변형(Strained silicon) 기술이 있다. 실리콘에 기계적 응력(Stress)을 가하면 전자와 정공의 이동도가 변한다는 변형 전위(Deformation potential) 이론에 따라, 격자 변형 실리콘의 에너지 밴드 갭과 캐리어의 유효 질량은 일반 실리콘과 다른 값을 갖게 된다. 이는 곧, 이동도의 개선을 위해 캐리어의 유효 질량을 줄이거나 캐리어가 유효 질량이 좋은 곳으로 이동시키는 것을 의미한다.

전자는 인장응력(Tensile stress)에 의해, 그리고 정공은 압축응력(Compressive stress)에 의해 이동도가 증가한다는 사실은 이론 및 실험으로 증명되었다. 예를 들어, 채널에 압축응력을 가하면 pMOS의 정공 이동도가 개선된다. 이렇게 실리콘 채널에 압축변형을 만들기 위해서는, 소스 및 드레인 영역이 에피택시 성장(웨이퍼 위에 일정한 방향성의 단결정을 성장시키는 방법)에 의해 실리콘-게르마늄(Si-Ge)막으로 채워져야 한다. Si-Ge의 단위 체적당 원자의 수는 원래의 Si 원자와 동일하지만 게르마늄 원자(Ge)가 실리콘 원자보다 더 크기 때문에, 이로 인해 채널에 압축응력이 발생하면서 채널을 미는 작용으로 정공의 이동도를 높일 수 있다. nMOS의 경우는 트랜지스터 주위에 높은 응력의 실리콘 질화막(Si_3N_4) 캡핑(Capping)층을 추가하거나 소스 및 드레인에 Si보다 격자 상수가 작은 SiC를 성장시켜 채널에 인장응력을 줌으로써 전자의 이동도를 개선할 수 있다.

6. 고유전율, 금속 게이트 MOS 트랜지스터(HKMG MOSFET)

소자의 동작(On) 전류를 높여 회로의 성능을 향상시키거나, 채널에 대한 게이트의 제어 능력을 올려 단채널 효과를 개선하기 위해서는 게이트 절연막 두께의 감소가 필요하다. 하지만 게이트 절연막(\text{SiO}_2)을 30Å 이하로 얇게 하면, [그림 2-22]와 같이 직접 터널링(Direct tunneling)에 의한 게이트 누설 전류가 발생하여 칩의 전력 소비가 급증하고 게이트 절연막의 신뢰성도 담보할 수 없게 된다.

이에 실리콘 산화막(\text{SiO}_2)보다 더 높은 유전상수(High-k)를 갖는 새로운 물질의 게이트 절연막 도입이 필요하게 되었다. 통상, High-k 유전체는 [그림 2-23]과 같이 \text{SiO}_2보다 작은 밴드 갭을 가지므로, 유전체의 물리적 두께를 증가시키지 않으면 더 많은 누설 전류가 흐를 수 있다. 따라서 소자의 누설 전류를 감소시키고 채널에서의 동일한 전기장을 유지하려면 [그림 2-22]와 같이 High-k 절연막의 두께를 증가시켜야 한다. 여기서 등가 산화물 두께 “EOT(Equivalent Oxide Thickness)”라는 것을 정의하는 것이 편리한데, EOT는 \text{SiO}_2와 동일한 정전 용량을 가질 때의 High-k 유전체의 두께를 의미하며, \text{SiO}_2의 두께로 환산한 값이다(\varepsilon_{\text{Hi-}k} = k, \varepsilon_{\text{SiO}_2} = 3.9).

\text{EOT} = t_{\text{SiO}_2} = (\varepsilon_{\text{SiO}_2} / \varepsilon_{\text{High-}k}) \cdot t_{\text{High-}k} = (3.9 / k) \cdot t_{\text{High-}k}

High-k 유전체는 적정한 k 값(~30, 너무 큰 k 값은 드레인에서 High-k 유전체를 통한 측면 필드의 관통(Fringing)으로 오히려 게이트 제어성을 감소시켜 단채널 효과가 가중될 가능성이 있음)과 높은 밴드 갭(5eV 이상)을 가져야 하고, Si과의 반응성과 결함 밀도가 낮아야 하며 채널에서의 캐리어 이동성의 손실도 최소화되어야 한다. 이러한 기준을 만족시키는 유전체는 \text{Al}_2\text{O}_3, \text{ZrO}_2, \text{HfO}_2 등이며 통상 피복 능력이 우수한 원자층 증착(Atomic Layer Deposition, ALD) 공정을 이용하여 증착한다.

기존의 불순물이 도핑된 다결정 실리콘 게이트 전극을 High-k 유전체와 함께 사용할 경우, 게이트 전압 인가 시 다결정 실리콘의 공핍 영역이 형성되어 게이트 산화막의 유효 두께 증가로 인한 구동 전류의 열화 문제가 발생한다. 또한 포논 산란에 의한 이동도 감소 문제를 야기할 수 있고 페르미 준위 고정(Fermi level pinning)에 의한 문턱 전압 제어에 심각한 문제를 초래할 수 있다. 이러한 문제들을 해결하기 위해 제안된 것이 금속 게이트 전극이다. nMOS와 pMOS의 적절한 문턱 전압 제어를 위해 서로 다른 일 함수(Work function)를 갖는 금속을 적용하기 때문에 공정 단계가 증가하는 문제가 있을 수 있다. 이렇게 High-k 물질과 금속 게이트를 합쳐 HKMG라고 부르며, 이를 적용 시 I_{\text{off}} 및 게이트 산화막 누설 전류의 감소는 물론, I_{\text{on}} 또한 개선되는 효과가 있다.

7. FinFET(Fin Field Effect Transistor)

(1) 등장 배경

기존의 2차원 평면 MOSFET은 게이트가 채널의 한 면에만 접촉하여 제어하는 구조로, 소자가 미세화됨에 따라 단채널 효과에 의한 누설 전류로 인해 대기 시 전력 소모가 증가하고 문턱 전압(V_{\text{Th}})을 낮추기 어려워 전원 전압 감소에 어려움이 있었다. [그림 2-25]와 같이 High-k 게이트 절연막 등의 단채널 효과 개선 기술을 적용하였으나, 더 이상의 미세화가 어려워 22nm급 소자부터 3차원 FinFET 구조가 등장하게 되었고, 14nm 기술 노드부터 본격 적용되어 왔다.

(2) FinFET의 구조, 원리 및 장점

FinFET은 Si 기판에 물고기의 등지느러미(Fin)와 유사한 모양으로 돌출된 얇은 수직 돌기가 채널이 되고, 이 채널의 3면을 게이트가 감싸게 됨으로써 채널에 대한 게이트의 제어 능력(Controllability)을 향상시킬 수 있는 3차원 구조이다. 쉽게 비유하면, [그림 2-26]과 같이 물이 흐르는 고무관을 위에서 누르는 것 보다 손으로 움켜쥐었을 때 물의 흐름을 더 잘 제어할 수 있다는 원리이다. 좀 더 정량적으로는 V_G에 의해 얇은 Fin 채널이 완전 공핍(Fully depletion)되면서 채널의 공핍 정전 용량(C_d)이 무시할 수 있을 만큼 감소하여 채널 하부의 누설 전류 경로를 원천 차단함으로써 문턱 전압 이하 스윙(Sub-Threshold Swing, SS = (kT/q)\ln(10)[1 + (C_d/C_i) (\text{mV/dec})]), 누설 전류(I_{\text{off}}) 및 DIBL 등의 SCE가 대폭 감소된다. 이로 인해 채널 도핑을 낮출 수 있어 캐리어의 이동도 개선 및 도펀트 수의 변동(Random Dopant Fluctuation, RDF) 감소에 따른 문턱 전압의 산포(\sigma V_{\text{Th}} \propto \sqrt{N_{\text{sub}}})도 개선할 수 있다. 한편, FinFET의 채널의 폭은 핀당 '2 \times 핀 높이(H_F) + 핀 폭(W_F)'으로 정의되어 단위 면적당 동작 전류(I_{\text{on}}) 또한 평면 소자 대비 증가하는 장점도 있다.

(3) FinFET의 단점과 대책

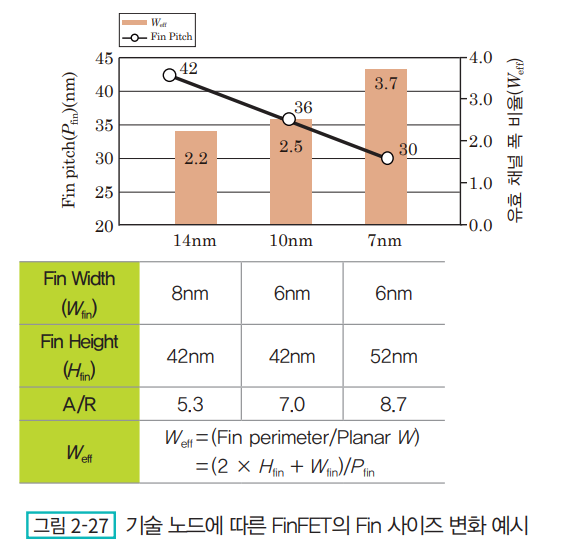

FinFET의 많은 장점에도 불구하고 미세화에 따른 핀의 폭과 높이 산포에 의한 문턱 전압 변동폭(\Delta V_{\text{Th}}) 감소를 위해 핀 패턴 형성 시 매우 정밀한 공정 제어가 필요하다. FinFET 소자의 충분한 성능 확보를 위해, [그림 2-27]의 예시와 같이 미세화에 따라 Fin의 피치는 감소하고 있으나 유효 채널 폭 비율(W_{\text{eff}}, 평면 소자에 대한 FinFET의 채널 폭의 비율)은 지속적으로 증가하는 추세에 있다. 이는 최소 피치당 핀 수의 증가 또는 핀의 높이 증가에 의한 고종횡비 구조를 초래하는 결과를 가져온다. 최소 피치 내에서 핀 수를 증가시키기 위해서는, 포토와 식각 공정을 복수 회 진행하는 LELE(Litho-Etch-Litho-Etch) 등의 다중 패터닝을 통한 패턴의 미세화가 필요하지만 두 패턴 사이에 정렬 오류 발생의 위험성이 있어 SAD(Q)P(Self Aligned Double(Quadruple) Patterning)와 같은 공법을 사용하거나 고가의 EUVL 공정을 사용해야 한다. 고종횡비 구조에 대한 대응은 게이트 스페이서(Spacer)와 같은 식각에 있어, 고에너지 이온에 의한 손상을 최소화하면서 핀 코너의 잔류물을 말끔히 제거하기 위한 우수한 선택비를 갖는 식각 공정도 필요하게 된다. 3차원 구조의 핀에 불순물을 주입하기 위해서는 등방성 도핑 및 저 손상 주입을 위한 플라즈마 도핑, 증기 상태 도핑(Vapor doping) 및 고온 이온주입(Hot ion implantation, 300~500°C) 등의 요소 공정 기술이 필요하다.

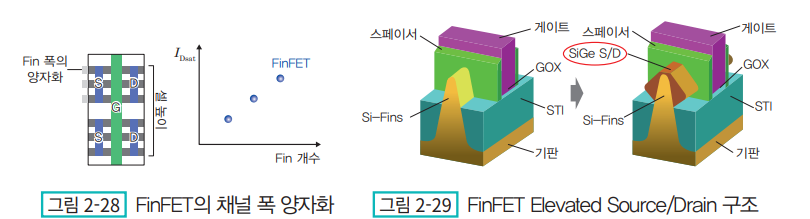

FinFET은 [그림 2-28]과 같이 채널 폭이 항상 핀 수의 배수가 되어 소자의 유효 폭이 양자화(정수 배로만 채널 폭을 늘릴 수 있음)되고 설계의 자유도가 떨어지는 문제가 있는데, 이는 핀 피치의 감소로 대응하고 있다. 이 외에 핀의 두께가 얇아 소스/드레인의 기생 저항이 증가되는 문제도 있다. 이는 부상(Elevated) 소스/드레인 구조를 채택하여 극복하고 있으며, 이때 [그림 2-29]와 같이 SiGe 소스/드레인 실리콘 격자 변형 기술을 적용하여 pMOS의 구동 능력도 함께 개선하고 있다.

FinFET은 [그림 2-28]과 같이 채널 폭이 항상 핀 수의 배수가 되어 소자의 유효 폭이 양자화(정수 배로만 채널 폭을 늘릴 수 있음)되고 설계의 자유도가 떨어지는 문제가 있는데, 이는 핀 피치의 감소로 대응하고 있다. 이 외에 핀의 두께가 얇아 소스/드레인의 기생 저항이 증가되는 문제도 있다. 이는 부상(Elevated) 소스/드레인 구조를 채택하여 극복하고 있으며, 이때 [그림 2-29]와 같이 SiGe 소스/드레인 실리콘 격자 변형 기술을 적용하여 pMOS의 구동 능력도 함께 개선하고 있다.

문턱 전압을 측정하는 또 다른 방법은 일정 전류(Constant current) 문턱 전압 측정법입니다. 최대 전달 컨덕턴스(

문턱 전압을 측정하는 또 다른 방법은 일정 전류(Constant current) 문턱 전압 측정법입니다. 최대 전달 컨덕턴스(

공핍 또는 약 반전 상태, 즉 문턱 전압 이하에서도 미량의 전류가 흐르는데 이 전류를 문턱 전압 이하 누설 전류(Sub-Threshold leakage current)라고 합니다. 문턱 전압 이상에서는 드레인 전압(

공핍 또는 약 반전 상태, 즉 문턱 전압 이하에서도 미량의 전류가 흐르는데 이 전류를 문턱 전압 이하 누설 전류(Sub-Threshold leakage current)라고 합니다. 문턱 전압 이상에서는 드레인 전압(