DRAM

기출문제 풀이

기출문제 ❶

DRAM의 기본 원리와 특성에 대해 설명하시오.

STEP1 접근 전략

설명형 문제로 난이도는 중 수준이며 출제 빈도가 높다.

DRAM 단위 셀의 구조, 동작 원리, 특성, 용도 순으로 설명한다.

DRAM이라 명명하게 된 이유가 설명 중에 드러나도록 한다

STEP2 답안 구조화 TIP

구조: 1T1C(단위 셀)

동작: WL, BL 선택 $\rightarrow$ Random access

대기: WL 0V, BL

1/2 V_H WT: WL↑

\rightarrow BLV_H orV_L input\rightarrow Cap 전하 저장\rightarrow WL↓RD: WL↑

\rightarrow Cap 전하 out\rightarrow BL 전하 공유\rightarrow \Delta V_{BL} \rightarrow S/A\rightarrow WL↓

특성

휘발성

\Delta V_{BL} \uparrow \propto C_s, 1/C_B \rightarrow C_s \uparrow, C_B \downarrow 누설 전류

\rightarrow Refresh\rightarrow Dynamic속도/용량/가격

\rightarrow SRAM과 낸드 사이

용도: 주 메모리

STEP3 모범답안

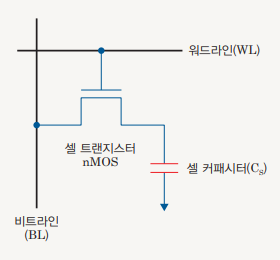

DRAM은 Dynamic Random Access Memory의 약자로, DRAM의 단위 셀은 하나의 nMOS 셀 트랜지스터(Cell Tr)와 하나의 셀 커패시터(Cell Cap)로 구성(1T1C)되며 Cell Cap에 데이터를 저장하는 휘발성 메모리 소자입니다. Cell Tr의 게이트를 워드라인(Word Line, WL)이라 하고 Cell Tr의 한쪽 소스/드레인과 연결되어 데이터가 드나드는 선의 역할을 하는 것을 비트라인(Bit Line, BL)이라 합니다. Cell Cap은 Cell Tr의 다른 한쪽 소스/드레인과 연결되어 있는 구조입니다. DRAM 셀의 동작은 크게 대기 상태, 쓰기, 읽기, 그리고 리프레시 동작으로 나눌 수 있습니다. 대기 상태에서는 WL에 0V가 인가되어 Cell Tr은 Off 상태에 있고, BL은 통상 High 데이터에 해당하는

DRAM의 쓰기 동작은 먼저 WL에 고전압을 인가하여 해당 Cell Tr을 ON 상태로 만들어준 후, BL에 쓰려고 하는 데이터 전압 값인

고득점 답안 DRAM의 파괴적 읽기 특성에 대해서도 설명한다. |

|

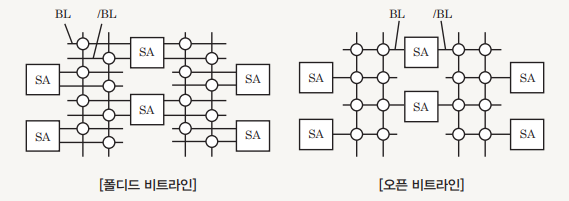

꼬리 질문 1 S/A는 무엇을 기준으로 변화된BL의 전압을 감지 및 증폭하는지 설명하시오. |

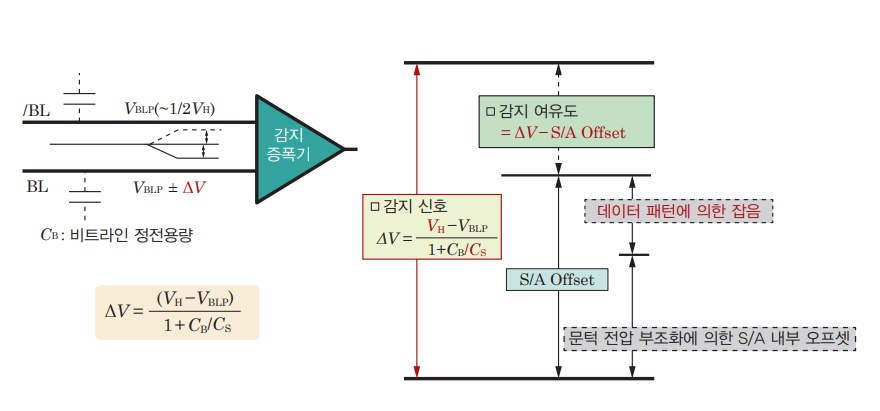

S/A는 변화된 BL 전압( |

꼬리 질문 2 전하 공유(Chargesharing)과정을 통해ΔV BL을 유도해 보시오. | ||

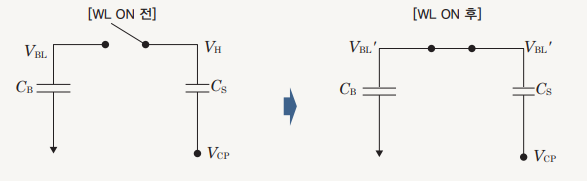

WL이 On되기 전과 후의 전체 전하량은 보존되어야 한다는 사실에 입각하여 High 데이터가 저장되어 있는 경우의 수식을 간략히 전개해 나가겠습니다. 우선 (좌측 그림과 같이) WL이 Off된 상태에서 BL쪽의 전하량은 (우측 그림과 같이) WL이 On된 상태에서는 BL과 Cell Cap의 스토리지 노드(SN)부의 전압이 | ||

기출문제 풀이

기출문제 ❷

DRAM 누설 전류의 원인과 그 해결책을 제시하시오.

STEP1 접근 전략

솔루션형 문제로 난이도는 중 수준이며 출제 빈도가 높다.

(판서 가능 시) DRAM 셀의 구조를 그리고 누설 전류의 경로를 표시한다.

각 누설 전류의 항목별로 원인과 대책을 간략히 설명한다.

누설 전류와 리프레시 특성과의 관계를 설명한다.

STEP2 답안 구조화 TIP

Q DRAM 누설 전류 원인 & 대책?

현상: Cell Cap 전하

\rightarrow 시간 경과\rightarrow 누설 전류\rightarrow 전하 소실누설 전류 경로:

① SN 접합부 누설 전류

② Cell Tr. Off 전류

③ 게이트 산화막 누설 전류

④ Cell Cap 절연막 누설 전류

⑤ Cell to Cell 누설 전류(Isolation 등)

대책: '1', '0' 판별 불가 전 다시 쓰기

\rightarrow 리프레시

STEP3 모범답안

DRAM은 셀 커패시터(Cell Cap)에 전하를 저장하여 메모리 소자로 사용하기 때문에 다양한 경로를 통한 전하 유출로 인해 데이터 손실 문제가 있습니다. 첫 번째(①)는 데이터가 저장되어 있는 Cell Cap의 스토리지 노드(Storage Node, SN)와 연결되어 있는 셀 트랜지스터(Cell Tr)의 PN 접합 누설 전류입니다. PN 접합 누설 전류는 두 가지 원인으로 발생할 수 있는데, 먼저 순수한 접합부에서의 누설 전류로 접합부의 고농도 도핑에 의한 고전계 형성 또는 이온주입 공정에 의한 손상 및 금속 오염 등의 공정 상 문제에 기인한 PN 접합 공핍 영역 내 포획 준위(Trap level) 생성으로 인한 누설 전류입니다. 적절한 채널 도핑에 의한 전계 감소와 저손상 공정 및 손상 회복을 위한 열처리 공정 적용 등으로 해결이 가능합니다. 또 다른 PN 접합 누설 전류의 원인은 Off 상태의 Cell Tr의 게이트와 SN 접합부가 겹치는 부분에서 강한 전기장에 의한 밴드 간 터널링을 통해 발생하는 게이트에 의해 유도된 드레인 누설 전류(Gate Induced Drain Leakage, GIDL)입니다. SN 접합부의

두 번째(②)는 Cell Tr의 Off 상태 전류로서 단채널 효과 및 낮은 문턱 전압이 주 원인입니다. SN 접합부의 전계 증가를 최소화하면서 문턱 전압의 증가를 위한 국부적인 채널 농도 증가 및 3차원 Cell Tr 적용 등의 구조적인 대책이 필요합니다.

세 번째(③)는 대기 상태에서 SN 접합과 게이트 산화막 사이에 흐르는 누설 전류로 게이트 산화막이 국부적으로 얇아지거나 핀홀(Pin hole) 등의 결함이 있을 경우 SN의 전하가 게이트로 빠져나가는 경우입니다. 이 현상은 특히, 스트레스가 집중된 STI(Shallow Trench Isolation) Corner rounding 부분이나 실리콘 기판을 식각하여 채널 길이를 증가시키는 3차원 Cell Tr의 경우 결정 방향에 따라 산화막 두께가 균일하지 못할 때 얇아진 국소 부분으로 전계가 집중되면서 발생할 수 있는 문제입니다. 균일한 두께의 산화막을 성장시킬 수 있는 라디칼 산화 공정 등을 적용함으로써 개선할 수 있습니다.

네 번째(④)는 Cell Cap의 유전체를 통한 누설 전류로, 정전 용량을 증가시키기 위해 유전체의 두께를 감소시킬 경우 직접 터널링에 의한 누설 전류 문제가 발생하므로 고유전율(High-

이렇게 다양한 경로를 통한 누설 전류는 일정 시간이 흘러 Cell Cap에 저장되어 있던 전하가 소실되는 문제가 발생하는데, 이를 방지하기 위해 주기적으로 해당 데이터를 다시 써주는 동작이 필요합니다. 이를 리프레시(Refresh) 동작이라고 합니다. 이러한 누설 전류는 온도 증가에 따라 지수 함수적으로 증가하므로, 리프레시 특성 평가도 고온에서 이루어져야 합니다.

꼬리 질문 1 DRAM Cell Tr는 통상 기판에 0V가 아닌 음의 전압을 인가하는데 그 이유에 대해 설명해 보시오. |

p형 기판(p-well)에 음의 기판 바이어스(Back bias)를 인가하면, 첫째, BL부 PN 접합의 공핍 영역 두께가 증가하여 접합 정전 용량(Junction capacitance)이 줄어 BL 기생용량이 감소하면서 |

꼬리 질문 2 DRAM의 셀 보존시간(Retention time, |

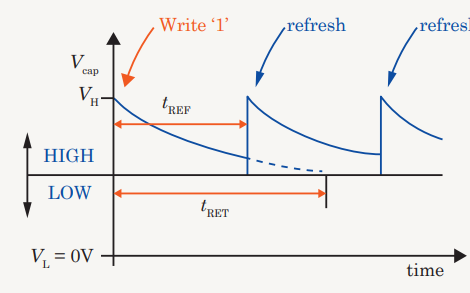

DRAM 메모리 셀에 '1'을 쓴 후 시간이 지나면, 셀은 다양한 경로를 따라 누설 전류가 발생하기 때문에 메모리 셀 커패시터(Cell Cap)의 스토리지 노드(Storage Node, SN) 전압이 감소하게 됩니다. 이렇게 데이터를 쓴 시점부터 감지 증폭기(Sense Amplifier, S/A)가 '0'과 '1'을 감지할 수 있는 최소 전압 수준으로 전압이 떨어질 때까지의 시간을 데이터 보존시간(Retention time, |

기출문제 풀이

기출문제 ❸

DRAM의 미세화에 따른 문제점과 그 해결책을 제시하시오.

STEP1 접근 전략

솔루션형 문제로 난이도는 중상 수준이며 출제 빈도가 높다.

미세화에 따른 대표적인 공정 및 소자 문제를 나열하고 그 해결책을 간략히 제시한다.

공정 측면에서는 가장 심각한 미세 패턴 형성에 대한 문제점 및 대책을 제시한다.

소자 측면에서는 DRAM 셀이 1T1C로 구성됨으로써 미세화에 따른 셀 트랜지스터와 셀 커 패시터의 열화와 그 대책에 대해 설명한다.

STEP2 답안 구조화

TIP Q DRAM 미세화 문제점 & 대책?

DRAM 미세화 → 공정, 소자적 문제 심각

미세 패턴 형성 → 다중 패터닝, EUVL

Cell Tr SCE↑,

I_{DSAT}↓ → 3D Cell TrCell Cap(

C_S )↓ → 3D Cell Cap, High-k 유전체

STEP3 모범답안

DRAM의 미세화에 따라 다양한 공정 및 소자 문제가 발생하게 되었습니다. 공정 측면에서는, 미세 패턴의 형성에 어려움을 겪게 되는데, 최소 패턴 크기가 30nm 이하로 되면서 ArF 액침 노광 단일 패터닝(Single-patterning)만으로는 원하는 해상도를 얻을 수 없어 다중 패터닝(Multi-Patterning) 기술을 사용 중에 있고, 최근에는 공정 원가 상승의 문제로 EUVL 공정이 도입되고 있습니다.

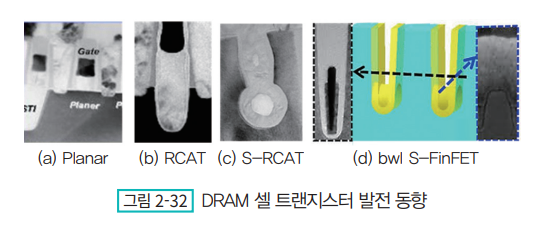

소자적으로는 먼저 DRAM 셀 트랜지스터(Cell Tr)의 열화 문제가 있습니다. 소자가 미세화됨에 따라 Cell Tr의 단채널 효과(Short Channel Effect, SCE) 등에 의해 이 문제가 더욱 심각해졌습니다. 기존 평면 트랜지스터(Planar Cell Array Transistor, PCAT)는 SCE에 의한 Off전류 문제가 발생하는데, 이를 구조적으로 개선하기 위해 채널이 형성될 부분의 실리콘을 일정 깊이로 식각하여 채널 길이를 증가시키는 함몰형 채널 어레이 트랜지스터(Recess CAT, RCAT)라는 구조가 도입되었습니다. 이후 채널의 하단부를 구 형태(Spherical)로 만들어 유효 채널 길이를 증가시켜 SCE를 추가 개선한 SRCAT(Spherical RCAT)이 등장하였습니다. 이후, SRCAT의 한계를 극복하기 위한 새들 핀(Saddle fin, S-Fin) 구조가 매몰 워드라인(Buried Word-Line(bWL)) 기술과 함께 등장하였는데, S-Fin은 RCAT의 채널 하단에 Fin 구조를 형성하고, 게이트가 Fin 형태의 채널을 감싸 채널 3면을 게이트로 제어하기 때문에 게이트 제어 능력이 향상되어 SCE가 개선되고, Fin의 높이만큼 채널 폭(Width)이 증가하여 전류 구동 능력도 향상되는 구조입니다.

다음을 DRAM 셀의 정전용량(

고득점 답안 DRAM의 미세화에 따른 감지 증폭기(Sense Amplifier, S/A)의 감지 여유도(Sensing margin)의 열화에 대해 설명한다. |

미세화에 따라 |

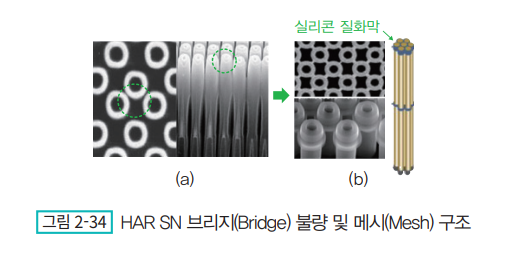

꼬리 질문 1 CellCap의3차원 수직 구조의 문제점과 해결책에 대해 설명하시오. |

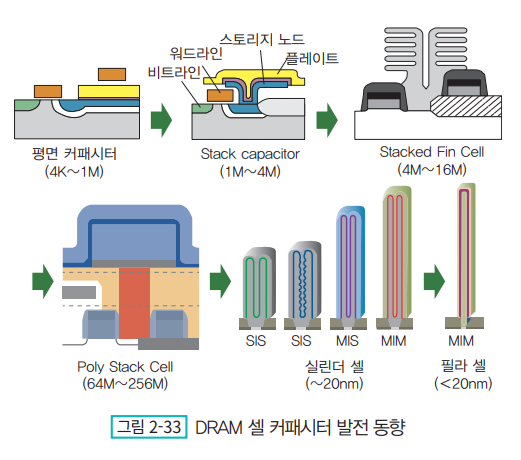

3차원 커패시터 전극의 구조에는 실린더(Cylinder)와 필라(Pillar) 형태가 있습니다. 실린더 구조는 높이에 비해 전극의 면적을 크게 확보할 수 있지만, 공정이 복잡해 미세화가 어렵다는 단점이 있습니다. 이에 비해 필라 구조는 모양은 단순하나 최소 정전 용량을 확보하기 위해서 실린더 대비 기둥의 높이를 증가시켜야 하고, 이로 인해 고종횡비(High Aspect Ratio, HAR) 구조가 되어 증착 및 식각 공정의 난이도 증가 문제를 초래하게 됩니다. 이에 대한 대책으로 기둥의 형성을 2단계로 분리해 종횡비를 완화하는 방법이 등장하였으나 이는 공정 수의 증가 및 고도의 공정 정밀도 제어를 요하는 반대급부가 있고, 이러한 높이의 증가는 SN(Storage Node)끼리 서로 들러붙는 리닝(Leaning) 불량 등의 기계적 한계에 직면하게 되는 문제가 있습니다. 이러한 문제는 SN을 실리콘 질화물(SiN) 그물(Net)로 서로 엮은 '메시(Mesh)' 구조와 같은 기술로 대응하고 있습니다. |

꼬리 질문 2 CellTr에 매몰WL(BuriedWL,bWL)을 적용한 이유에 대해 설명해 보시오. |

bWL은 기판 표면 아래로 WL(Word Line)을 매몰시켜 BL(Bit Line)과 WL 사이의 기생 BL 정전 용량( |

기출문제 풀이

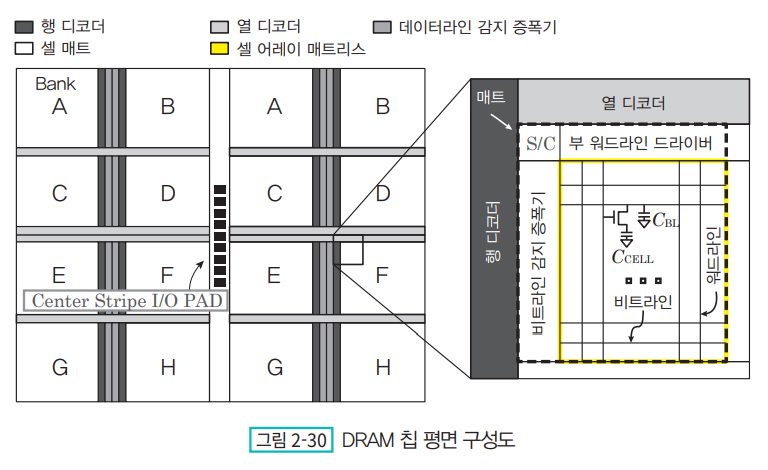

1. DRAM 셀(Cell)의 구조, 동작 원리 및 특성

(1) DRAM 셀의 구조

셀 트랜지스터의 다른 한쪽의 소스/드레인과 접해 있는 셀 커패시터의 한쪽 전극을 스토리지 노드(Storage Node, SN)라 하고, 다른 한쪽 전극을 셀 플레이트(Cell Plate, CP)라고 하며, 전하가 이 커패시터에 저장되어 있는지 여부를 가지고 High 또는 Low 데이터인지를 구분하는 것이다.

(2) DRAM 셀(Cell)의 동작 원리

DRAM 셀의 동작은 크게 대기 상태, 쓰기, 읽기, 그리고 리프레시 동작으로 나눌 수 있다.

① 대기(Stand-By) 상태

DRAM 셀은 쓰기나 읽기 동작을 하지 않는, 즉, 데이터를 저장만 하고 있는 대기 상태에서는 WL에 0V가 인가되어 셀 트랜지스터가 Off 상태에 있고, BL에는 통상, High 데이터에 해당하는

② 쓰기(Write) 동작

쓰기 동작은 먼저 WL에 고전압이 인가되고 BL이 선택되면 BL에 인가되던

③ 읽기(Read) 동작

읽기 동작 역시, WL에 고전압이 인가되고 BL에는

④ 리프레시(Refresh) 동작

이처럼 DRAM은 아주 작은 용량의 커패시터에 전하가 저장되고 저장된 전하는 전원이 공급되는 상태에서도 여러 경로를 통해 누설 전류 형태로 매우 짧은 시간에 방전되어 버리기 때문에, 이를 방지하기 위해서는 S/A가 High와 Low 여부를 판단할 수 없을 정도의 전하 손실이 있기 전에 주기적으로 해당 셀에 동일 데이터를 다시 써 주는 동작이 필요하다. 이를 리프레시(Refresh) 동작이라고 하고 이 때문에 대기 시간 동안 아무런 동작을 하지 않는 SRAM의 Static과 대조되는 Dynamic이란 말이 붙게 된 것이다. 리프레시 동작은 읽기(Read) 동작과 동일한데, 단지 읽은 데이터가 외부로 나가지 않고 앞서 설명한 다시 쓰기(Restore) 동작만으로 가능하다는 것이 차이점이다.

(3) DRAM의 특성

DRAM은 전원을 공급하지 않으면 저장된 데이터가 사라지는 휘발성(Volatile) 메모리 소자로, PC 등 전자기기의 주 메모리(Main memory)의 역할을 하며, SRAM 대비 속도가 느린 단점이 있으나, SRAM 셀 대비 단위 셀당 좁은 면적으로 큰 용량을 가지며 비트(Bit)당 가격도 저렴하다. 또한 DRAM은 낸드 대비 동작 속도는 빠르지만, 용량이 작고 가격도 비싸다는 특성을 가지며 주기적인 리프레시(Refresh) 동작을 해야 하므로, 전력소모 및 동작 속도의 저하가 불가피하다는 단점을 갖는다.

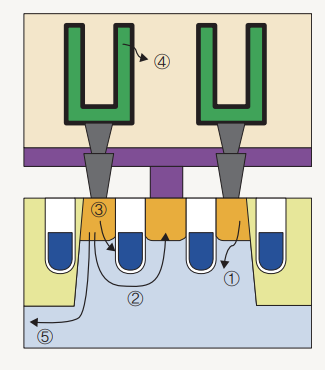

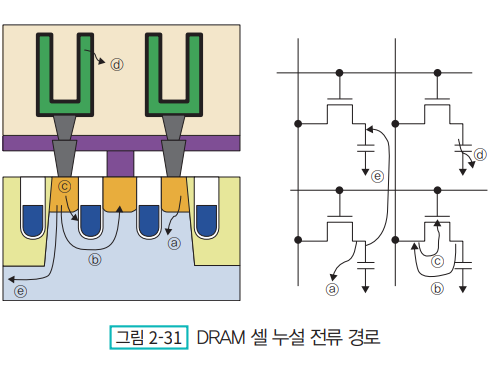

2. 셀 누설 전류(Cell leakage current)

DRAM은 셀 커패시터에 전하를 저장하는 방식의 메모리 소자이므로, 다양한 경로를 통한 전하 유출은 데이터 손실 문제를 일으킨다. 먼저 [그림 2-31]의 경로 ⓐ는 셀 커패시터의 SN과 연결된 셀 트랜지스터의 PN 접합에서 발생하는 누설 전류이다. 이 전류의 원인은 두 가지로 나눌 수 있다. 먼저 순수한 접합부에서의 누설 전류이다. 이는 접합부의 고농도 도핑에 의한 고전계 형성, 또는 이온주입 및 플라즈마 공정 등에 의한 손상 및 금속 오염 등 공정 상 문제에 기인한 PN 접합 공핍 영역 내 포획 준위(Trap level) 생성으로 인해 발생한다. 적절한 채널 도핑에 의한 전계 감소와 저손상 공정 및 손상 회복을 위한 열처리 공정 적용 등으로 해결이 가능하다.

다음 경로 ⓑ는 셀 트랜지스터의 오프(Off) 상태 전류로서, 단채널 효과 및 낮은 문턱 전압이 주원인이다. SN 접합부의 전계 증가를 최소화하면서 Off 상태의 누설 전류를 감소시킬 수 있는 구조적 대책 또는 국부적 채널 도핑 농도 증가와 같은 대책이 필요하다. 이것은 후술할 소자 격리를 통한 누설 전류(경로 ⓒ)와 함께, 정적 리프레시(Pause refresh) 특성은 물론 주변 셀의 동작 환경에 의해 영향을 받는 동적 리프레시(Dynamic(Disturbance) refresh) 특성이 악화되는 원인이 된다.

경로 ⓒ는 대기 상태에서 SN 접합부와 게이트 산화막 사이에 흐르는 누설 전류이다. 게이트 산화막이 국부적으로 얇아지거나 공정 과정에서 생길 수 있는 핀홀(Pin hole) 등의 결함으로 인해 SN의 전하가 게이트로 빠져나가는 것이다. 스트레스가 집중된 STI corner rounding 부분이나 실리콘 기판을 식각하여 채널 길이를 증가시키는 3차원 Cell Tr의 경우 결정 방향에 따라 산화막 두께가 균일하지 못할 때 얇아진 국소 부분으로 전계가 집중되면서 발생할 수 있는 문제로, 균일한 두께의 산화막을 성장시킬 수 있는 라디칼 산화 공정 등을 적용함으로써 개선할 수 있다.

경로 ⓓ는 셀 커패시터의 유전체를 통한 누설 전류이다. DRAM은 셀 커패시터에 전하를 저장하는 방식의 메모리 소자이므로, 셀의 정전 용량을 가능한 한 증가시켜야 한다. 따라서 정전 용량을 증가시키기 위해 커패시터의 유전체의 두께를 감소시키는 방법을 사용하는데, 이 경우 직접 터널링에 의한 누설 전류 문제가 발생할 수 있다. 고유전율(High-

마지막으로 경로 ⓔ는 셀 도면 상 가까운 활성(Active) 영역 간의 소자 격리를 통한 누설 전류이다. 원인으로는 주로 포토 및 식각 공정 등에 의한 물리적 불량(패턴 및 임계 선폭(Critical Dimension, CD) 불량 등)이 있으나, 필드(Field) 위를 지나가는 게이트에 의한 기생 필드 트랜지스터 문턱 전압 저하로 인한 누설 전류도 가능한 원인이다. 이에 대해서는 적정 필드 차단 이온주입(Field stop ion implant) 조건을 적용하는 것으로 대응할 수 있다.

3. DRAM의 미세화(Scaling) 동향과 문제점 및 대책

DRAM의 지속적인 미세화에 따라 다양한 공정 및 소자 문제가 발생하게 되었다. 공정적으로는 미세 패턴의 형성에 어려움을 겪게 되는데, 최소 패턴 크기가 30nm 이하로 되면서 LELE, SADP 등의 다중 패터닝(Multi-Patterning) 기술을 사용 중에 있고, 최근에는 EUVL 공정이 도입되고 있다. DRAM 셀의 주요 구성 요소인 셀 트랜지스터(Cell Tr)와 셀 커패시터(Cell Cap)의 동향(Trend) 및 미세화(Scaling)의 문제점과 대책들에 대해 알아보도록 하자.

(1) 셀 트랜지스터

셀 트랜지스터(Cell Tr)는 DRAM의 셀 커패시터(Cell Cap)와 비트라인(BL) 사이에서 스위치 역할을 하는 nMOS이다. DRAM 제품의 최소 선폭이 100nm 이하로 축소됨에 따라 [그림 2-32(a)]와 같은 기존의 평면 트랜지스터(Planar Cell Array Transistor, PCAT)는 단채널 효과(SCE)에 의한 오프 (Off) 상태 누설 전류가 발생하게 된다. 이러한 누설 전류의 억제를 위해 채널 도핑을 증가시키게 되면, 반대급부로 Cell Cap의 SN과 접하는 PN 접합부의 전계가 증가하고 접합 누설 전류가 증가하여 전하 보존(Retention) 특성이 악화된다. 이러한 Cell Tr의 SCE를 개선하기 위해, [그림 2-32(b)]의 함몰형 채널 어레이 트랜지스터(Recess Channel Array Transistor, RCAT)라는 소자가 도입되었다. RCAT은 채널이 형성될 부분의 실리콘을 적정 깊이로 식각한 함몰 게이트(Recess gate) 구조를 가진다. 이 구조 덕분에 채널 길이를 증가시켜 채널 도핑을 감소시킬 수 있으므로, PCAT에서 문제되었던 SCE 및 전하 보존 특성 문제를 해결할 수 있었다. 그러나 80nm 이하로 미세화됨에 따라 RCAT의 하단 바닥 곡률이 뾰족해지면서, 문턱 전압과 기판 효과(Body effect)의 증가, 문턱 전압 이하 스윙(Sub-Threshold Swing, SS) 및 DIBL 특성 악화 등의 한계에 달하게 되어, 이를 개선하기 위해 [그림 2-32(c)]의 S-RCAT(Spherical-Recess Channel Array Transistor) 구조가 등장하였다. 이 구조는 함몰 채널의 하단부를 구(Spherical) 형태로 만들어 곡률 반경을 증가시킴으로써 RCAT의 문제점을 상당 부분 해결할 수 있었고 이 구조는 ~40nm 기술 노드까지 적용되었다. 그러나 이후 S-RCAT의 직선 부분과 구형 함몰 부분이 만나는 목(Neck) 부분에 전계가 집중되는 문제로 전하 보존 특성의 악화를 비롯한 다양한 신뢰성 열화를 초래하였고, 구동 전류 부족 문제도 대두되었다. 이러한 S-RCAT의 문제를 해결하고자 등장한 구조가 [그림 2-32(d)]의 새들 핀(Saddle Fin, S-Fin)이다. S-Fin은 RCAT의 채널 하단에 핀(Fin) 구조를 형성하고, 게이트가 이 Fin 형태의 채널을 감싸는 3차원 트랜지스터 구조로 말의 안장 모습을 하고 있다고 하여 Saddle이라 불리게 되었다. 이 구조는 채널의 세 면을 게이트로 제어하기 때문에 게이트 제어 능력이 향상되어 SCE가 개선되고, 핀의 높이만큼 채널 폭(Width)이 증가되어 전류 구동능력도 개선되었다. 현재는 30nm 이하 DRAM Cell Tr에 적용 중이다. S-Fin 구조는 문턱 전압(

(2) 셀 커패시터

DRAM Cell Cap은 2개의 전극과 그 사이에 삽입된 유전체로 구성되어 있으며, Cell Tr의 접합부와 연결되는 하부 전극을 스토리지 노드(SN), 다른 한쪽의 상부 전극을 셀 플레이트(CP)라고 한다. DRAM은 Cell Cap을 충전 및 방전시킴으로써 데이터를 저장(Write)하고 읽어(Read)낸다. 따라서 데이터를 안정적으로 저장하고 감지하려면 최소 정전 용량 값이 필요하다. Cell Cap의 최소 정전 용량 값은 과거 ~25fF/cell 정도였으나, 감지 증폭기 및 관련 구동 회로의 최적화로 점차 감소하여 최근 ~10fF/cell 수준까지 내려가게 되었다. Cell Cap의 정전 용량은

DRAM의 미세화에 따라 Cell Cap의 크기 감소가 요구됐지만, 이는 곧 정전 용량의 감소를 동반하므로 다른 방안이 필요하게 되었다. 그래서 [그림 2-33]과 같이 2차원 평면 구조에서 평면적은 줄이되, 수직 치수(Vertical dimension)를 증가시켜 3차원적으로 면적을 늘려 왔다. 최근 3차원 커패시터 전극의 구조에는 실린더(Cylinder)와 필라(Pillar, 기둥) 형태가 있다. 실린더 방식은 전극의 면적을 크게 확보할 수 있지만, 공정이 복잡하고 공간이 좁아 구현이 어렵다. 이에 비해 필라 형태는 모양이 단순하지만, 정전 용량 확보를 위해 실린더 대비 기둥의 높이를 증가시켜야 한다. 이로 인해 고종횡비(High Aspect Ratio, HAR) 구조가 되어, 박막 증착 및 식각 공정의 난이도가 상승하는 문제를 초래하게 된다. 이러한 문제에 대해 기둥을 두 단계로 분리해 형성함으로써 종횡비를 완화시키는 방법이 있으나, 이 또한 공정 수의 증가 및 고도의 공정 정밀도 제어를 요구한다. 그리고 이러한 높이의 증가인 기계적 한계에도 직면하게 되는데, 이로 인해 [그림 2-34(a)]처럼 고종횡비(HAR)의 SN끼리 서로 들러붙는 브리지(Bridge) 및 리닝(Leaning) 불량이 일어날 수 있다. 이러한 불량을 방지하기 위해 SN을 [그림 2-34(b)]와 같이 실리콘 질화물(SiN) 그물(Net)로 서로 엮는 메시(Mesh) 구조가 사용되고 있다.

마지막으로 고유전율 물질의 적용에 대해 설명한다. 기존에 사용하던 실리콘 산화막(

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기