금속배선 공정

기출문제 풀이

기출문제 ❶

구리 금속배선을 사용하는 이유와 문제점, 그리고 해결책은 무엇인지 설명하시오.

STEP1 접근 전략

설명형, 솔루션형이 조합된 중상 수준의 문제로, 전반적인 금속배선 공정의 이해도를 측정 하고자 하는 문제이다.

Al에서 Cu 배선으로 전환된 이유를 설명한다.

저유전율(Low-k) 박막은 간략히만 언급하고 추가 질문에 대응한다.

Cu 적용 시 문제점을 언급하고, 그 해결책으로 다마신 공정이 도입되었음을 설명한다.

다마신 공정의 상세 흐름은 추가 질문에서 답하도록 한다.

STEP2 답안 구조화 TIP

Q 구리 배선 사용 이유, 문제점, 해결책?

Al → Cu 전환

- 소자 미세화 → 배선 저항 & 전류 밀도↑

→ RC Delay & 신뢰성(EM) 문제

- 신 물질 필요 → Al 배선 금속 비저항 감소(Al ≫ Cu) & EM 수명 개선(Al ≪ Cu)

Cu 문제점

- 식각 어려움 → 새로운 패턴 형성 방법 필요

- Cu의 Si, SiO2 내 확산↑ → 확산 방지막 필요

해결책: 다마신 구조 적용

STEP3 모범답안

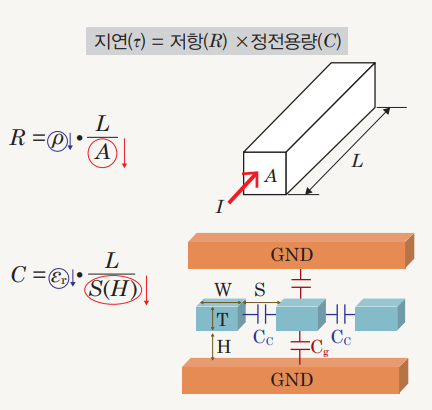

소자의 미세화에 따라 반도체 회로의 지연 문제가 부각되고 있습니다. 트랜지스터의 미세화로 전류 구동 능력이 개선되어 게이트 지연(Gate delay)은 감소하는 추세이나, 배선에 의한 지연은 급격한 증가를 보이고 있습니다. 회로 지연의 주 원인은 미세화에 따른 금속배선의 단면적(

그러나 이러한 많은 장점에도 불구하고 Cu를 반도체 배선 공정의 소재로 사용하는 데는 치명적인 몇 가지 문제가 존재하는데, 먼저 패턴 형성을 위한 식각 시 휘발성 있는 반응 부산물을 만들지 못하여 식각이 어렵다는 점이 있고, Cu는 침입형(Interstitial) 확산의 특성을 갖는 물질로 확산계수(Diffusion coefficient)가 높아 실리콘(Si) 또는 실리콘 산화막(

고득점 답안 Cu 배선을 위한 트렌치 형성 후 금속 매립 공정에 대해 좀 더 상세하게 설명한다. |

Cu 배선을 위한 트렌치 형성 후 금속 박막을 매립하는 공정 과정을 설명하면, 먼저 Cu의 확산을 막는 확산 방지층인 탄탈륨 질화막(TaN)을 증착합니다. 그후 탄탈륨(Ta)막을 증착하는데, 이는 TaN과 이후 증착될 Cu와의 접착력(Adhesion)이 좋지 않아 중간에 접착층(Glue layer)이 필요하기 때문입니다. 이어 Cu 종자(씨앗, Seed) 박막층을 증착하게 되는데, 이는 이후에 진행될 Cu 전해 도금 시 Ta막의 산화를 방지하고, 웨이퍼 표면의 전기 저항을 낮춰 균일한 Cu 도금 특성을 얻기 위함입니다. 이후 전해 도금을 이용해 트렌치를 Cu로 매립합니다. 이때 도금 방식을 사용하는 이유는 도금의 빠른 증착 속도에 따른 생산성 향상과 초등각 증착(Super conformal deposition)에 의한 우수한 비아 홀 매립 특성 때문입니다. 그리고나서 잉여증착된 Cu 및 하부 금속층들에 대한 CMP 평탄화를 한 후 마지막으로 SiN을 증착하여 Cu 상부 노출을 방지함으로써 다마신 공정이 마무리됩니다. |

꼬리 질문 1 전자이동(EM)에 대해 설명하시오. |

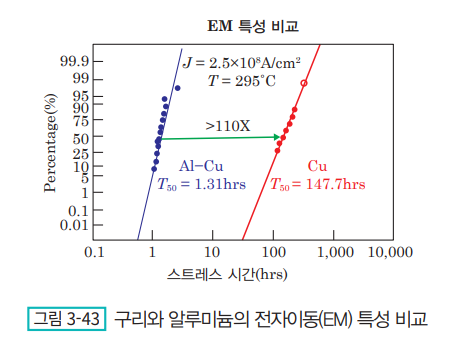

반도체 내에 흐르는 전류는 그 절대값 자체가 그리 크지 않지만 반도체 배선의 단면적이 매우 좁아 단위 면적당 흐르는 전류 밀도는 매우 높습니다. 이렇게 고밀도의 전류가 도체를 통해 흐르게 되면, 많은 수의 전자가 전기장에 의해 빠른 속도로 이동하면서 이온과 충돌하고, 주위 이온들과의 결합력이 낮은 이온이 전자가 이동하는 방향으로 따라 움직이는 현상이 나타나는데, 이러한 현상을 전자이동 또는 일렉트로-마이그레이션(Electro Migration, EM)이라 합니다. EM에 의해 이온은 금속 내의 결정 입계(Grain Boundary, GB)를 따라 이동하게 되고 이렇게 금속 이온이 빠져나간 자리에는 빈 공간인 보이드(Void)가 발생합니다. 이로 인해 배선이 끊기는(Open) 불량이 발생할 수 있습니다. 한편 이동 중인 금속 이온이 큰 결정립(Grain)을 만나 결정 입계가 막히게 되면, 결정 입계를 통한 이동이 어려워지는 지점에서 금속이 수직 또는 수평 방향으로 빠져나오는 현상이 발생합니다. 이를 힐록(Hillock)이라 하는데, 이로 인해 회로 간의 단락(Short) 불량이 발생할 수 있습니다. |

꼬리 질문 2 기생 커패시턴스 감소를 위한 Low- |

유전율( 먼저 분극성의 감소는 |

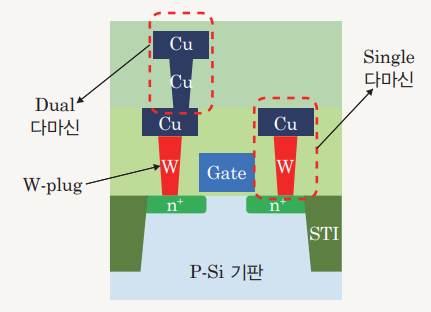

꼬리 질문 3 다마신 공정에서 단일(Single)과 이중(Dual) 다마신 공정의 차이에 대해 설명하시오. |

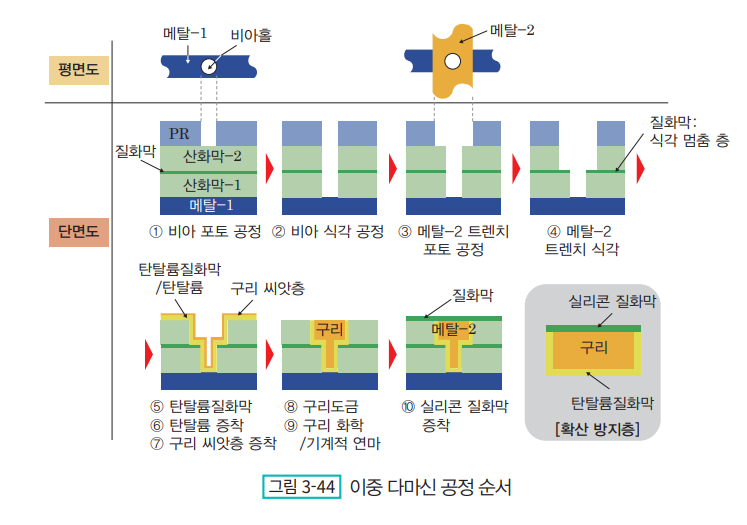

이중(Dual) 다마신은 상부와 하부의 금속배선을 이어주는 콘택, 즉 비아(Via) 홀이 상부 금속 라인(트렌치, Trench)과 동시에 형성되는 공정이며, 단일(Single) 다마신 공정은 비아와 트렌치를 따로 진행하는 것으로, 비아는 W 플러그를 통해 생성되고, 금속배선은 Cu 다마신 공정을 이용하여 생성됩니다. 따라서 공정 단계 수가 많아 이중 다마신 공정 대비 복잡합니다. 단일 다마신 공정은 금속배선층 간의 비아 홀 대신에, 확산층이 있더라도 실리콘과 직접 접촉하여 Cu를 사용하기 위험한 콘택 홀에 금속(W 등)을 매립하는 용도로 사용됩니다. |

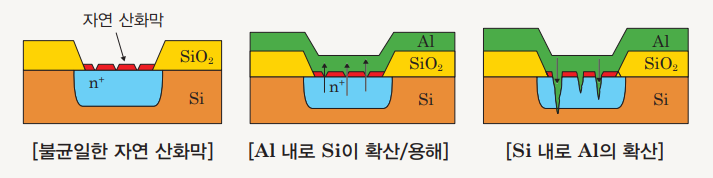

꼬리 질문 4 비저항 및 EM 등의 신뢰성 문제 외에 Al이 가진 문제점에 대해 설명하시오. |

먼저 Al은 비등점(660°C)이 낮아 후속 공정의 온도를 설정하는 데 제한이 큽니다. 두 번째로는 접합 스파이킹(Junction spiking) 문제가 있습니다. 실리콘(Si)과 순수 알루미늄(Al)이 직접 접촉할 시에는 접합 스파이킹 문제가 발생하게 되는데, Si과 순수 Al이 직접 접촉된 상태에서 저항성 콘택의 형성을 위한 열처리(~450°C)를 하면 Si이 Al 내로 확산되어 녹아 들어가게 됩니다. 이 과정에서 Al 내 Si의 고체 용해도인 ~0.5%(450°C) 수준으로 용해되어 들어가고, Si의 빈 자리에는 대신 Al이 확산되어 채워지게 됩니다. 이때 Si은 불균일한 자연 산화막 등의 영향으로 무작위로 용해되므로 운동화 바닥의 뾰족한 돌기와 같은 스파이킹 현상이 생기고, 이것이 p 또는 n의 접합 깊이(Junction depth)보다 깊을 경우에는 접합으로서의 기능을 상실하게 되어 소자가 정상적으로 동작할 수 없게 됩니다. 이를 개선하기 위해 미리 Al에 1% 정도의 Si을 첨가하여 Si이 Al 내로 녹아 들어가는 것 자체를 방지하거나, 확산 방지막(TiN)을 증착하여 Si의 확산을 방지하는 방법 등을 사용하기도 하였습니다. |

기출문제 풀이

기출문제 ❷

회로 지연(RC Delay)을 감소시키는 방법에 대해 설명하시오.

STEP1 접근 전략

솔루션형의 중상 수준의 문제로 금속배선 공정 및 집적 공정의 지식을 필요로 하는 문제이다.

RC Delay란 무엇이고 어떻게 정의되는지 설명한다.

각 요소별로 구조적 측면과 공정 및 소재적 측면의 개선 방향을 설명한다.

STEP2 답안 구조화 TIP

Q 회로 지연(RC Delay) 감소 방안?

RC Delay → 소자 미세화 → 저항(R)↑, 기생 커패시턴스(C)↑

충방전에 소모되는 시간 증가 → 신호 지연

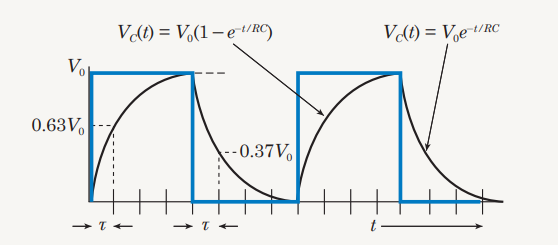

시정수(τ) = R × C → τ(충전): 63% V0, τ (방전): 37% V0

저항: 기생 & 배선 저항 감소 → 공정, 신 물질, 배치 설계

기생 정전용량: Low-k 물질

STEP3 모범답안

RC Delay란 기생저항을 포함한 도체의 저항(R) 및 기생 커패시턴스(C)에 의해 발생되는 신호 지연을 말합니다. 이는 전기적 신호가 지나가는 통로인 도체 및 기생적인 접촉 저항 등의 저항 값이 높거나 기생적으로 생성된 커패시터의 정전용량이 크면 이를 충방전하는 데 시간이 걸리고 이 시간이 회로 동작 지연으로 나타난다는 의미입니다. RC Delay는 R과 C의 곱으로 정의되는 시정수(

고득점 답안 이후의 금속배선은 어떻게 발전할지에 대해서도 설명한다. |

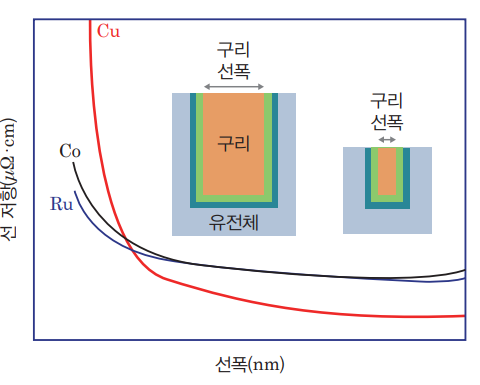

현재 많은 반도체 업체에서 Cu 배선이 적용되고 있으나, 7nm 이하 공정에서는 다마신 공정에서 금속배선이 채워질 트렌치(Trench) 폭이 감소하는 데 반해 확산 방지막, 접착층, Cu 종자층 등의 두께 감소는 크지 않습니다. 따라서 Cu 배선 선폭이 감소함에 따라 비저항이 급격하게 증가(Cu 배선 선폭이 10nm까지 줄어들게 되면 선(Wire) 비저항은 벌크 비저항의 약 10배까지 상승)하는 비저항 크기 효과(Resistivity size effect)로 인해 더 이상 Cu 배선으로는 RC Delay를 감소 또는 유지하기가 어려워졌습니다. 이는 Cu가 상온에서 39nm, 즉 상대적으로 큰 포논 산란(Phonon scattering)에 의해 결정되는 물질 고유의 값인 벌크 전자 평균 이동 거리(Electron Mean Free Path, EMFP)를 가지는 것이 주 원인입니다. 따라서 일부에서는 차세대 배선 물질로서, 벌크 비저항이 Cu보다 크지만 짧은 EMFP를 가져 저감된 비저항 크기 효과와 향상된 물질 신뢰성을 가지는 Ru과 Co를 이미 사용하고 있는 것으로 알려져 있습니다. |

꼬리 질문 1 소스-드레인 면저항 감소를 위해 고농도, 얕은 접합의 이온주입이 필요한 이유를 설명하시오. |

먼저항만 생각한다면 고농도의 불순물을 도핑하면 되겠지만, 접합 깊이를 제어하지 않으면 고농도의 도펀트가 동일 온도 이력에서 실리콘 깊이 방향은 물론, 수평 방향으로도 확산되어 MOSFET의 유효 채널 길이가 짧아져 단 채널 효과가 심화될 수 있습니다. 때문에 매우 낮은 에너지의 이온주입으로 가능한 얕은 이온주입이 되도록 해야 합니다. 물론 펀치 쓰루 스톱(Punch-Through stop), 후광(Halo) 이온주입 등을 병행하지만, 소스-드레인이 고농도화가 되면 이들의 농도도 증가시켜야 하므로 접합 누설전류 및 접합 기생 정전용량 등의 증가로 인해 소자의 특성이 열화될 수 있습니다. |

꼬리 질문 2 실리사이드, 폴리사이드, 살리사이드의 차이점에 대해 설명하시오. |

실리콘은 주로 고융점 금속(Refractory metal)과 반응하여 안정적인 금속 또는 반도체 특성의 화합물을 형성하는데 이를 실리사이드(Silicide)라고 합니다. 소자의 미세화에 따라 MOSFET의 소스-드레인의 접합 깊이가 얕아지고, 이는 소스-드레인의 기생 저항(면저항 및 접촉 저항)의 증가를 초래하여 결국 소자의 동작 속도가 저하되는 문제가 발생합니다. 실리사이드(Silicide)는 이러한 소스-드레인만이 아니라 다결정 실리콘 게이트의 면저항을 감소시키는 데도 사용되는 공정 방법이며 널리 사용되는 물질로는 티타늄( 살리사이드(Self-Aligned Silicide, SALICIDE)는 별도의 패터닝 공정 없이 자기 정렬 방식으로 소스 및 드레인의 단결정 실리콘 및 다결정 실리콘 게이트 전극과 금속 간의 반응에 의해 실리사이드 및 폴리사이드를 동시에 형성할 수 있는 공정을 말하며 금속이 실리콘과는 반응을 하지만 실리콘 산화막과는 반응을 하지 않아 산화막 위의 미반응 금속을 화학 약품으로 제거하는 원리를 이용한 공정입니다. |

핵심 이론 정리

1. 구리 배선과 저 유전율(Low-k) 배선층간 절연체의 필요성

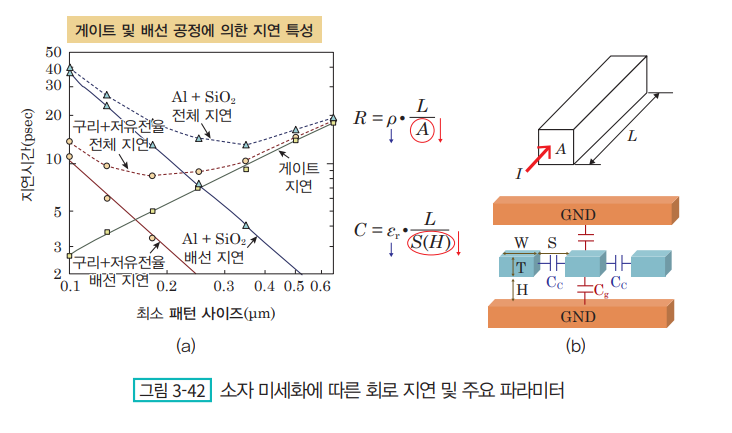

[그림 3-42(a)]는 소자 미세화에 따른 회로의 신호 지연 특성을 나타낸 것이다. 게이트 지연(Gate delay)은 주로 트랜지스터에 의한 지연으로, 소자의 미세화에 따라 전류 구동 능력의 개선으로 감소하는 추세이지만, 배선에 의한 지연은 급격한 증가를 보여 기존 알루미늄(Al)과

시정수(Time constant)라고도 불리는 회로 지연 시간(

2. Cu 배선의 문제점 및 해결책

배선층 재료로서 Cu는 몇 가지 치명적인 문제가 존재하는데 ① 패턴 형성을 위한 식각 시 휘발성 있는 반응 부산물을 만들지 못해 식각이 어렵고, ② Cu의 확산 계수가 높아

3. Cu 이중 다마신(Dual damascene) 공정

다마신은 Cu 식각과 확산 문제를 동시에 해결 가능한 방법으로 여기서 이중(Dual)이란 말이 붙는 이유는 상부와 하부의 금속배선을 이어주는 콘택 홀, 즉 비아(Via) 홀이 상부 금속 라인(트렌치, Trench)과 동시에 형성되기 때문에 붙여진 이름이다. [그림 3-44]에는 이중 다마신 공정의 순서도를 도시하였고, 위쪽은 평면도(위), 아래쪽은 단면도(옆)를 나타낸 것이다. 먼저 하부 금속층(메탈-1) 위로 배선 간 절연막인 산화막-1과 얇은 실리콘 질화막, 산화막-2 순으로 증착되어 있는 상태에서, ① 포토 공정으로 메탈-1과 상부 금속 메탈-2를 연결하는 비아 홀을 패터닝한다. ② PR을 블로킹층으로 하여, 세 층의 절연막을 식각하여 메탈-1이 드러나게 한다. ③ 메탈-2가 형성될 영역을 패터닝한다. ④ 패터닝된 PR을 마스크로 하여 산화막-2를 식각한다. 이때 식각 선택비 차이를 이용해 실리콘 질화막이 드러났을 때 식각이 멈출 수 있도록 한다. 이로써 비아 홀(구멍)과 메탈-2 라인이 동시에 형성된다. ⑤ Cu의 확산을 막는 확산 방지층인 탄탈륨 질화막(TaN)을 증착하고 ⑥ 접착력을 위해 접착층(Glue layer)으로 탄탈륨(Ta)막을 증착시킨다. ⑦ Cu 전해 도금 시 웨이퍼 표면의 전기 저항을 낮춰 균일한 Cu 도금 특성을 얻기 위해 얇은 Cu 씨앗(종자, Seed) 박막층을 증착한다. ⑧ 전해 도금 공정을 이용해 비아 홀 및 상부 금속 라인(Trench)을 Cu로 매립한다. 이때 도금 방식을 사용하는 이유는 도금의 빠른 증착 속도에 따른 생산성 향상과 우수한 비아 홀 매립 특성 때문이다. ⑨ 상부 금속 라인(Trench) 상부를 CMP 공정으로 제거하고, 표면을 평탄화한다. 마지막으로 ⑩ 실리콘 질화막(SiN) 등 Cu 확산 및 산화를 막을 수 있는 박막을 증착함으로써, Cu 배선의 2가지 문제를 모두 해결한 Cu 이중 다마신 공정이 완료된다.

4. 저 유전율(Low-k) 절연막(Dielectric)

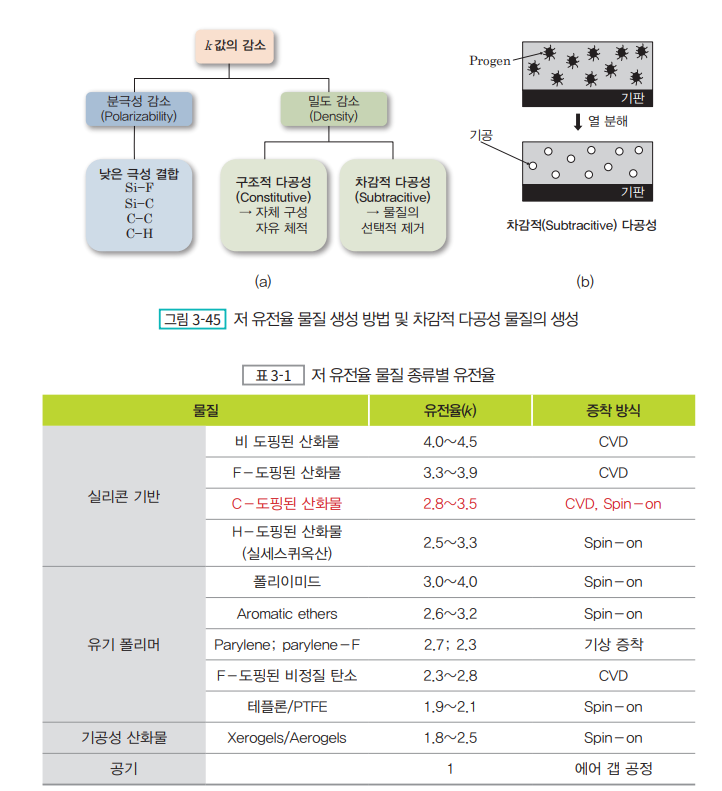

배선 층간 절연체의 저 유전율(Low-

저 유전율 물질의 형성 방법에는 [표 3-1]과 같이 통상 회전 도포(스핀 코팅, Spin coating)와 화학적 기상 증착(Chemical Vapor Deposition, CVD)의 두 가지 방법이 있다. Low-

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기