기출문제 풀이

기출문제 ❶

\text{SiO}_2 두께가 시간에 따라 어떻게 변화하는지에 대해 설명하시오.

STEP1 접근 전략

설명형 문제이며 난이도는 중상 수준으로, 산화 공정 영역에서 출제 빈도가 높다.

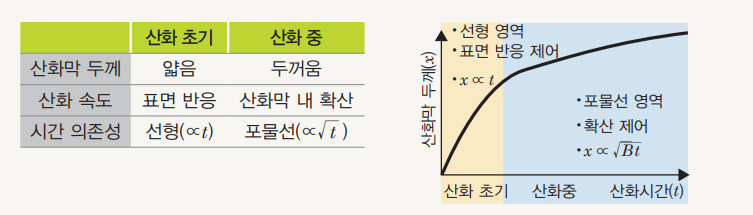

Deal-Grove 산화 모델을 기반으로 시간에 따른 \text{SiO}_2 두께 변화 그래프를 이용하여 설명한다.

산화 초기와 산화가 어느 정도 진행된 상태에서의 그래프 기울기가 바뀌는 이유를 설명한다.

STEP2 답안 구조화 TIP

Q \text{SiO}_2 두께의 시간 의존성?

- 산화제가 \text{SiO}_2 표면으로 이동 → \text{SiO}_2 내 확산 → \text{Si}/\text{SiO}_2 경계에서 반응 → 산화막 형성

STEP3 모범답안

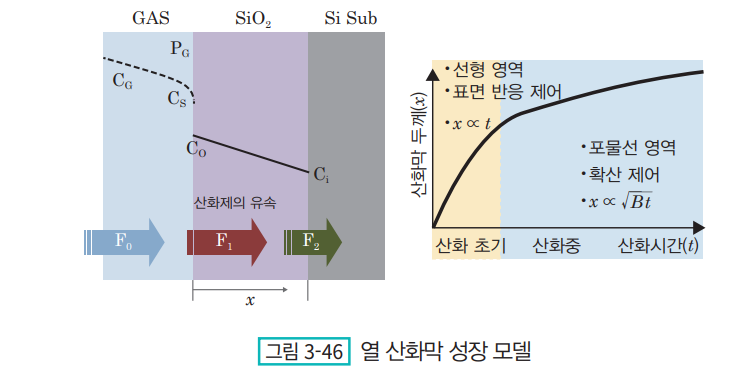

실리콘의 산화 과정은 ① 산화제(Oxidant)가 벌크(Bulk) 가스에서 \text{SiO}_2 표면으로 이동하고, ② \text{SiO}_2를 통해 확산되다 ③ \text{Si}/\text{SiO}_2 경계에서 실리콘과 만나 반응하여 실리콘이 소모되며 산화막이 성장하는 모델로 설명할 수 있으며 이를 Deal-Grove 모델이라고 합니다. 산화막이 없거나 매우 얇은 산화 초기에는 산화제가 산화막을 뚫고 확산해 나가기가 쉬우므로, 실리콘과 만나 반응하여 \text{SiO}_2를 형성하는 과정이 전체 산화 속도를 결정짓는 인자가 되며, 반응 속도가 산화 시간에 선형적으로 비례(∝t)하는 선형 구간으로 이를 표면 반응 제어 영역이라고 합니다. 시간이 흐른 후에는 산화막이 어느 정도 성장하여 산화제가 산화막을 뚫고 \text{Si}/\text{SiO}_2 경계까지 도달하는 과정이 전체 산화 속도를 결정 짓는 인자가 되고, 이때의 산화막은 산화 시간의 제곱근에 비례하여 포물선 형태로 성장하므로 이 구간을 확산 제어 영역이라고 합니다.

꼬리 질문 1 건식 산화와 습식 산화의 차이점에 대해 설명하시오. |

열 산화막 성장 반응은 실리콘 원자와 산소 원자가 고온에서 반응하여 \text{SiO}_2 박막이 성장되는 건식 산화(Dry oxidation)와 수증기(\text{H}_2\text{O})를 실리콘과 반응시켜 산화막을 성장시키고 \text{H}_2를 반응 부산물로 배출하는 습식 산화(Wet oxidation)의 두 가지로 나눌 수 있습니다. 산화막 성장 속도에 있어서는 습식 산화가 건식 대비 5~10배 빠른데, 이는 \text{O}_2보다 \text{H}_2\text{O}의 \text{SiO}_2 내로의 용해도(\text{OH}^-)가 크기 때문입니다. 전기적 특성은 습식 산화막 쪽이 열악한데, 이는 산화막 내 수소(\text{H}_2) 잔류와 낮은 밀도에 의한 문제로 해석됩니다. 따라서 건식 산화막은 고품질의 박막 특성이 요구되는 게이트 산화막 등에 사용되고 습식 산화막은 두꺼운 산화막을 빠른 시간 내에 성장시키는 용도로 사용되어 왔습니다. |

꼬리 질문 2 열 산화막 성장 시 소모되는 실리콘의 두께와 전체 산화막 두께의 비율은 어느 정도인지 설명하시오. |

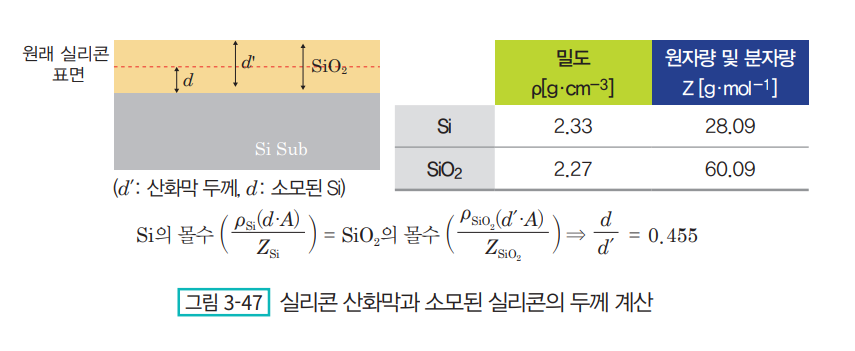

실리콘 산화막(\text{SiO}_2)은 실리콘(\text{Si})을 소모해 가면서 성장하는데, 예를 들어 100\text{nm}의 산화막을 성장시킬 때 소모된 \text{Si}은 45.5\text{nm}, 즉 전체 산화막 두께의 약 46% 정도의 \text{Si}이 소모되면서 성장하게 됩니다. 이때 \text{Si}(2.33\text{g/cm}^3, 28.09\text{g/mol})과 \text{SiO}_2(2.27\text{g/cm}^3, 60.09\text{g/mol})의 원자(분자) 밀도 및 원자량(분자량), 그리고 소모되는 \text{Si}의 몰수와 \text{SiO}_2의 몰수가 같다는 관계로부터 전체 산화막 두께와 소모된 \text{Si} 두께의 비를 도출할 수 있습니다. |

기출문제 풀이

기출문제 ❷

반도체 업체들이 (100)면의 실리콘을 선호하는 이유를 설명하시오.

STEP1 접근 전략

설명형 문제이며 난이도는 중 수준이다.

실리콘 산화막 성장 시 생성되는 네 가지 전하에 대해 설명하고, 이 중 실리콘 결정면에 영향을 받는 전하들이 원자 밀도와 관련 있음을 설명한다.

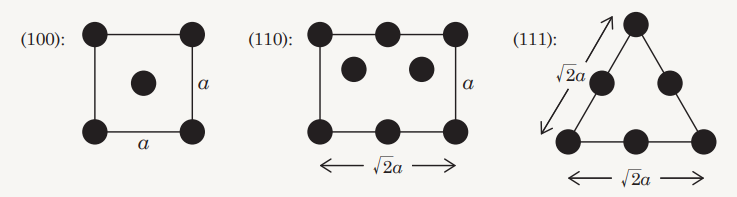

결정면에 따른 원자 배치를 이용, 원자 밀도가 가장 낮은 결정면을 선택했음을 설명한다.

STEP2 답안 구조화 TIP

Q (100) 웨이퍼의 선호 이유?

- 산화물 고정 전하(Q_f), 계면 포획 전하(Q_{it}), 유동성 이온 전하(Q_m), 산화막 포획 전하(Q_{ot})

- Q_f: 산화 미참여 잉여 \text{Si} \rightarrow \text{Si-Rich}

- Q_{it}: \text{O}_2와 미결합 \rightarrow \text{Si Dangling bond}

STEP3 모범답안

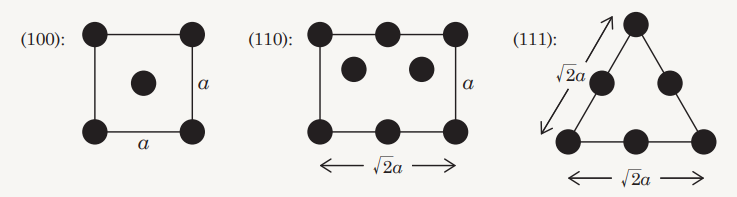

실리콘 산화막(\text{SiO}_2) 성장 시 산화막 내, 그리고 \text{Si}/\text{SiO}_2 계면에서 소자 동작에 악영향을 미치는 다양한 전하가 생성되는데, 산화물 고정 전하(Fixed oxide charge, Q_f), 계면 포획 전하(Interface trapped charge, Q_{it}), 유동성 이온 전하(Mobile ionic charge, Q_m), 산화막 포획 전하(Oxide trapped charge, Q_{ot}) 등 크게 4가지 종류가 있습니다. 이 중 실리콘의 결정 방향에 영향을 받는 전하는 산화물 고정 전하(Q_f)와 계면 포획 전하(Q_{it})이며 산화물 고정 전하(Q_f)는 산화 시 완전히 산화에 참여하지 못한 잉여 \text{Si}으로 \text{Si-Rich} 상태가 되는 것이 발생 원인이며, 계면 포획 전하(Q_{it})는 \text{Si}/\text{SiO}_2 계면에 \text{O}_2와 결합하지 못한 불포화 결합(Dangling bond)에 의해 발생합니다. 이들은 모두 산화되는 표면의 \text{Si} 원자 밀도에 영향을 받게 되는데, 실리콘 결정면에 따른 단위 면적 내 실리콘 원자의 개수는 (100)면이 가장 적고, (111), (110) 순으로 많아집니다. 따라서 \text{Si} 원자 밀도가 가장 낮아 MOSFET의 게이트 산화막과 실리콘 채널 사이 계면에 원치 않는 전하가 생성되어 MOSFET의 문턱 전압 등의 특성에 악영향을 가장 적게 주는 (100)면의 웨이퍼를 선호하게 된 것입니다.

꼬리 질문 1 설명한 계면 전하 외에(100)면의 웨이퍼를 선호하는 또 다른 이유에 대해서도 설명하시오. |

\text{Si} 웨이퍼를 (100) 방향으로 제작 시 표면의 \text{Si} 원자 밀도가 가장 낮고 이에 따라 불포화 결합이 가장 적어 자연 산화막(Native oxide)의 성장을 억제할 수 있습니다. 또한 (100)면의 웨이퍼 사용 시 MOSFET의 채널은 (110)면이 되는데 이 면은 전자와 정공의 이동도를 최적화할 수 있는 면이 되며 이러한 현상은 최근 MOSFET 기술인 FinFET에서 그 효과가 잘 나타나고 있습니다. 이러한 이유들로 인해 (100)면의 웨이퍼를 주로 사용하는 것입니다. |

핵심 이론 정리

1. 산화 공정의 개요

산화 공정은 소자 형성 시에 꼭 필요한 다양한 용도의 절연막(산화막)을 형성하는 공정으로, 크게 CVD와 열 산화 공정으로 나눌 수 있다. 여기서는 고온의 열 산화 공정에 대해 알아보자.

(1) 열 산화 공정(Thermal oxidation)

열 산화 공정은 건식(Dry)과 습식(Wet) 산화로 나뉜다. 먼저 건식 산화는 \text{O}_2와 \text{Si}을 반응시켜 \text{SiO}_2를 성장시키는 방식이고 습식 산화는 수증기 상태의 물(\text{H}_2\text{O})과의 반응을 통해 \text{SiO}_2를 얻는 방식이다. \text{SiO}_2 내 \text{H}_2\text{O}의 용해도가 \text{O}_2보다 크므로 습식 산화가 건식 산화 대비 5~10배 빠른 산화막 성장 속도를 보인다. 전기적 특성은 습식 산화막 쪽이 더 열악한데 이는 성장 속도가 빠른 만큼 구조적으로 치밀성이 떨어지고 산화막 내 잔류하는 수소로 인한 문제로 해석된다. 따라서 건식 산화로 생성된 산화막(건식 산화막)은 고품질의 박막 특성이 요구되는 게이트 산화막 등에 적용되고, 습식 산화로 생긴 산화막은 두꺼운 산화막을 빠른 시간 내에 성장시키는 용도로 사용되어 왔다.

(2) 열 산화막의 특성

① \text{Ge}이나 화합물 반도체 등에 비해 산화가 용이하고, 9\text{eV} 정도의 높은 에너지 밴드 갭을 갖는 우수한 절연체이며, \text{Si}/\text{SiO}_2 경계의 결합 밀도가 낮아 안정적이고 접착력도 우수하다. ② \text{SiO}_2는 \text{Si}에 비해 도펀트에 대한 확산도(Diffusivity)가 낮아 선택적 도핑(Doping) 시 차폐막(Masking layer)으로 사용할 수 있다. ③ \text{Si}이나 \text{SiO}_2에 대한 식각 선택비가 커, 식각 하드마스크(Hard mask)로의 적용이 가능하고, 불산(\text{HF}) 등을 제외한 거의 모든 화학 약품에 저항성이 높다.

(3) 열 산화막의 응용

열 산화막은 30\text{nm} 이상의 두께를 가지며, 선택적 도핑을 위한 차폐막으로 사용되거나 또는 소자 격리 기술의 하나인 LOCOS(LOCal Oxidation of Silicon) 공정의 필드 산화막(Field oxide) 용도로 사용되었다. 현재는 이온주입 공정 및 얕은 트렌치 소자 격리 기술(Shallow Trench Isolation, STI)의 도입으로 인해 더 이상 쓰이지 않게 되었고, PR 또는 CVD 절연막 등으로 대체되어 사용되고 있다. 그 대신 열 산화막은 주로 20\text{nm} 이하의 얇은 표면 보호막(Surface passivation) 및 게이트 산화막의 용도로 사용 중이다.

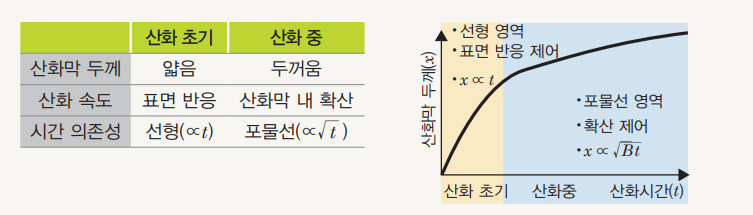

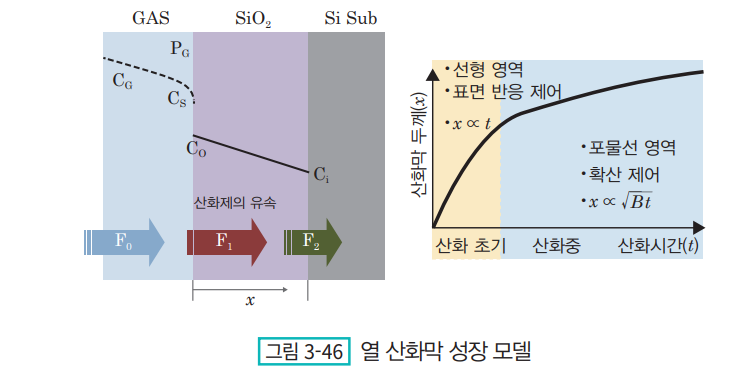

(4) 열 산화막의 성장 메커니즘

실리콘의 산화 과정은 [그림 3-46]의 좌측 그림과 같이 ① \text{O}_2 또는 \text{H}_2\text{O}의 산화제가 벌크(Bulk) 가스에서 \text{SiO}_2 표면으로 이동하고, ② 기 성장된 \text{SiO}_2를 통해 확산되다가 ③ \text{Si/SiO}_2 경계에서 \text{Si}과 만나 반응하여 \text{Si}이 소모되면서 \text{SiO}_2가 성장하는 모델로 설명할 수 있습니다. 이를 딜-그로브(Deal-Grove) 모델이라 합니다. 산화막이 없거나 매우 얇은 산화 초기에는 산화제가 산화막을 뚫고 확산해 나가기 쉬우므로 \text{Si}과 만나 반응하여 \text{SiO}_2를 형성하는 과정이 전체 산화 속도를 결정짓는 인자가 됩니다. 반응은 산화 시간에 선형적으로 비례(x \propto t)하는 선형 구간에 해당하며 이를 표면 반응 제어 영역(Surface reaction limited regime)이라 합니다. 시간이 흐른 후에는 산화막이 어느 정도 성장하여 산화제가 산화막 내를 확산하여 \text{Si/SiO}_2 경계까지 도달하는 과정이 전체 산화 속도를 결정짓는 인자가 됩니다. 이때의 산화막은 시간의 제곱근에 비례(x \propto \sqrt{t})하여 포물선 형태로 성장하는 확산 제어 영역에 해당하므로 [그림 3-46]의 우측 그림과 같은 형상을 보이게 됩니다.

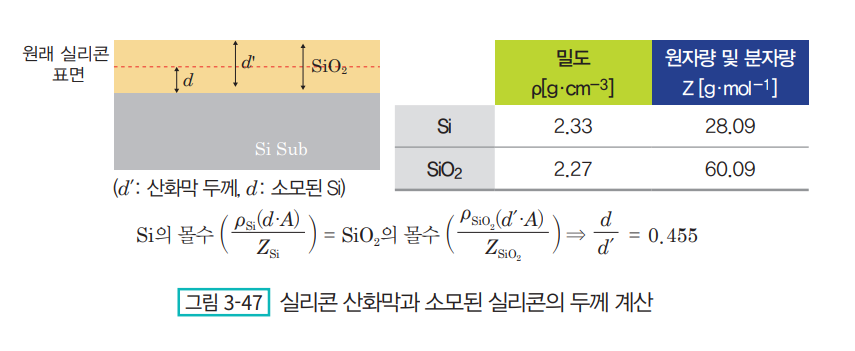

(5) 열 산화막 성장 시 실리콘 소모량

\text{SiO}_2는 \text{Si}을 소모하면서 성장합니다. 그렇다면 예를 들어 100\text{nm}의 \text{SiO}_2를 성장시킬 때에는 \text{Si}이 어느 정도나 소모되는지 알아봅시다. [그림 3-47]과 같이 전체 \text{SiO}_2의 두께를 d'라 하고, 소모된 \text{Si}의 두께를 d라 하자. 여기서 \text{Si}과 \text{SiO}_2의 물리량인 원자(분자) 밀도와 원자량(분자량)을 알아야 하며, [그림 3-47]에 이를 도시하였습니다. d와 d'의 관계는 소모되는 \text{Si}의 몰수(mol)와 \text{SiO}_2의 몰수의 관계로부터 간단하게 도출할 수 있습니다. 먼저 몰수는 밀도(\text{g/cm}^3)와 부피(\text{cm}^3)를 곱하여 질량(g)을 구하고, 이 값을 \text{Si}의 원자량(g/mol) 또는 \text{SiO}_2의 분자량으로 나누어 구합니다. 1\text{mol}의 \text{Si}이 산화되어 1\text{mol}의 \text{SiO}_2가 생성되므로 두 몰수를 같게 두어 d와 d'를 구하면 되는데, 계산 결과 총 100\text{nm}의 산화막을 성장시켰을 경우 \text{Si} 45.5\text{nm}가 소모된다는 것을 알 수 있습니다.