테스트 장비

기출문제 풀이

기출문제 ❶

우리 회사에서 XRD를 어떤 용도로 사용하는지 설명하시오.

STEP1 접근 전략

난이도는 중 수준이며 자주 출제되는 문제이다.

측정 장비에 대한 질문은 원리까지 이해하여 설명하기에는 상당히 어려운 내용이다. 따라서 이 장비를 사용하여 반도체의 어느 부분을 검사하는 것인지에 초점을 맞추어 설명하는 것이 좋다

STEP2 답안 구조화 TIP

XRD 필요성: 소재 부품의 구조 해석

주요 이론

- X-선 발생 및 X-선 회절 장치

- X-선 회절 이론 및 측정

- X-선 회절 분석 Data 해석(다결정)

STEP3 모범답안

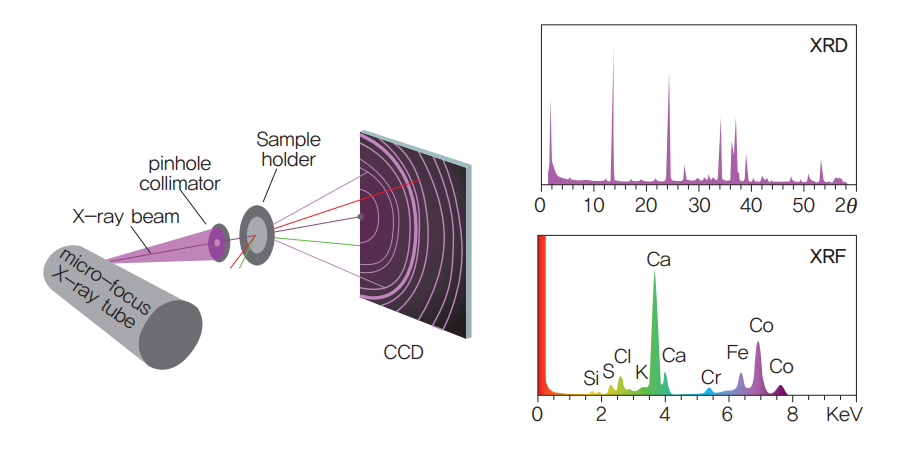

X선 회절법(X-Ray Diffraction, XRD)은 X선을 사용하여 제조된 반도체의 결정 구조를 측정하는 기술입니다. X선을 결정에 부딪히게 하면 그중 일부는 회절을 일으키는데, 그 회절각과 강도는 물질 구조 상 고유한 값이므로 이 회절 X선을 이용하여 시료에 함유된 결정성 물질의 종류와 양에 관련된 정보를 알 수 있습니다. 이처럼 결정성 물질의 구조에 관한 정보를 얻기 위한 분석 방법이 XRD입니다

XRD 분석은 공정 단계를 통제하고 반도체 웨이퍼의 물리적 구조를 분석하기 위해 X선의 주사 각도를 달리하며 얻은 회절 패턴을 해석하여 결정의 구조를 분석하는 방법이며, 다양한 결정형이 존재할 경우 대략적인 정량 분석이 가능합니다. 또한 XRD 분석을 통해 결정화도 값을 얻을 수 있으며, Profiling 기법으로 분석하고자 할 경우 결정과 관련된 피크 정보가 필요합니다. 그리고 XRD의 특수 기법을 활용하여 박막의 단결정, 다결정 등 결정질(Quality) 분석, 다층(Layered structure) 박막의 구조, 박막의 두께, 각 층의 밀도 등의 정보를 얻을 수 있습니다. 향후에는 EUV에 사용되는 Bragg Mirror의 특성을 분석하는 데 중요한 장비가 될 것입니다.

기출문제 풀이

기출문제 ❷

SEM 분석 시 박막이 균일하게 합성되었다는 것을 어떻게 알 수 있는지 설명하시오.

STEP1 접근 전략

난이도는 상 수준이며 자주 출제되는 문제이다.

측정 장비에 대한 질문은 원리까지 이해하여 설명하기에는 상당히 어려운 내용이다. 따라서 이 장비를 사용하여 반도체의 어느 부분을 검사하는 것인지에 초점을 맞추어 설명하는 것이 좋다.

STEP2 답안 구조화 TIP

Q 반도체 분석 장비?

주사 전자 현미경: SEM(Scanning Electron Microscope)

- 표면 분석

- 불량 분석

- 길이 측정

- Image

- 성분 분석

에너지 분산 X선 분광 분석기: EDS(Energy Dispersive X-Ray Spectroscope)

- 이물질

- 오염 부위에 대한 정성 분석

Photon 방출 분석 시스템: PEM(Photon Emission Microscope)

- Standby current 불량

- Pin leakage 불량

열적 방출 분석 시스템: Thermal emission microscope

- Metal 배선의 Short

- Contact의 저항 이상

- 산화막의 Microplasma leakage

- 산화막 파괴

STEP3 모범답안

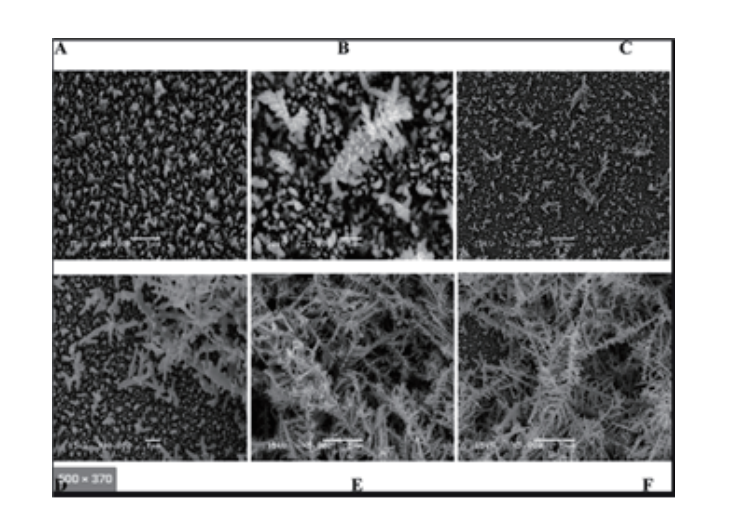

주사 전자 현미경(Scanning Electron Microscope, SEM)은 관찰하고자 하는 시료의 미세한 부분을 확대하여 관찰하고 분석하는 데 사용됩니다. 1,500배 정도까지의 배율로 관찰할 수 있는 광학 현미경에 비하여 SEM은 80만 배의 높은 배율로 시료의 관찰이 가능하며, 관측용 시료 제작이 용이하여 시료 표면 관찰에 가장 널리 사용됩니다. SEM은 가속된 전자 빔을 시료 표면에 주사시켜 시료 표면에서 발생되는 2차 전자(Secondary electron), 투과 전자, X선 등을 집속 렌즈를 통해 모아 검출기로 검출하고, 이를 증폭하여 모니터 상에 동기로 주사하며 표면의 높낮이를 나타내는 3차원 영상으로 형상화하는 분석 장치입니다. 시료의 표면 상에 있는 미세 구조의 관찰, 구성 원소의 분포, 정성, 정량 등을 분석할 수 있습니다.

SEM 영상은 2차원 데이터임에도 불구하고 마치 3차원 이미지와 유사하여 물체를 훨씬 정확하게 관찰할 수 있다는 장점이 있습니다. 따라서 요철이 심한 파단면이나 표면조도가 큰 시료 관찰에도 유리합니다. 광학 현미경과 달리 전자 현미경의 영상은 눈으로 직접 볼 수 없으므로 모니터에 그림으로 나타내게 됩니다. 전자빔이 입사된 각 점의 명암을 화면의 좌표계에 옮겨 각 점(Pixel)의 명암으로 영상을 나타내며 SEM에서는 각 Spot에서 튕겨 나온 전자의 양에 따라 명암이 구분됩니다. 박막표면이 논바닥처럼 갈라진 것과 같은 구조가 있다면 박막이 균일하지 않다는 것을 의미합니다. 그리고 투명한 박막을 입히게 되면 두께에 따라 반사되는 색이 변화하기 때문에 확인이 가능한데, 불투명한 경우에는 박막의 위치를 달리하면서 면저항을 측정하기도 합니다. 필요 시 이온빔으로 두께 방향으로 깎아 내면 경계가 분명해지므로 접촉면의 균일도를 확인할 수도 있습니다.

핵심 이론 정리

1. 반도체 측정/검사장비 기술 개요

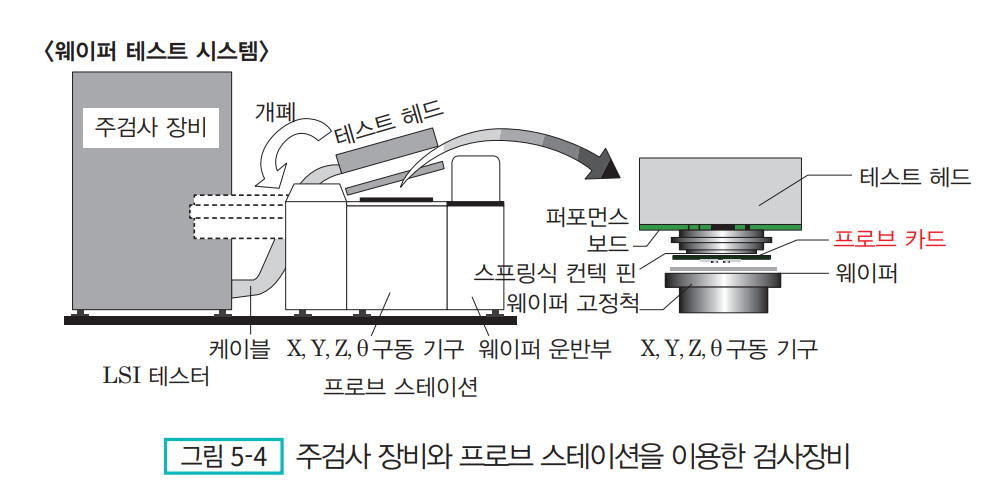

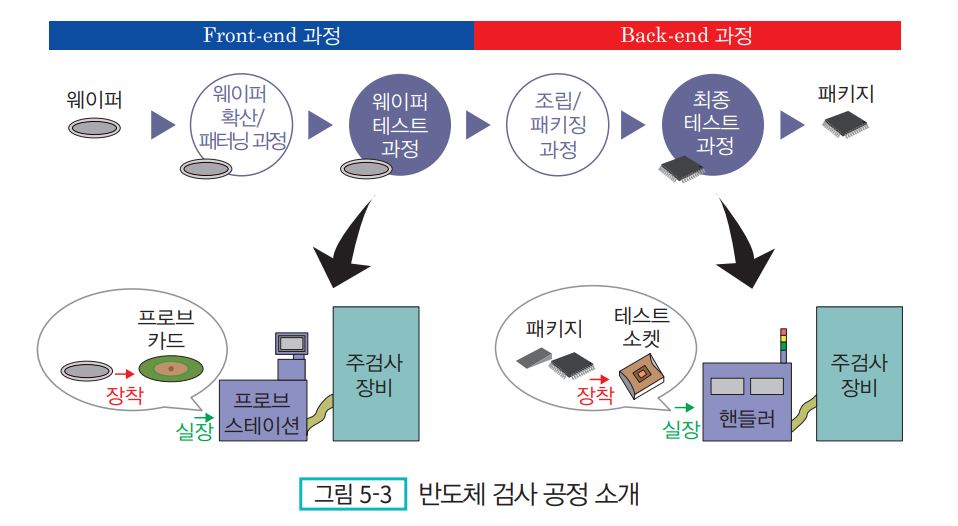

반도체 검사장비는 크게 주검사 장비(Automated Test Equipment, ATE), 프로브 스테이션(Probe Station), 핸들러(Handler), 번인(Burn-in) 장비로 구성되어 있다. 이는 웨이퍼 상태에서 칩의 정상여부를 검사하는 프로브 스테이션 등의 ‘웨이퍼 검사장비’, 반도체 전후 공정을 마친 후 최종 단계에서 패키지의 정상적인 작동 유무를 평가하는 핸들러 등의 ‘콤포넌트 검사장비’, 그리고 PCB(Printed Circuit Board)에 반도체 소자가 여러 개 장착되어 있는 모듈 상태에서 제대로 작동하는지를 검사하는 ‘모듈 검사장비’로 분류할 수 있다.

(1) 주검사 장비

반도체 주검사 장비(IC 테스터) 또는 자동화된 테스트 장비(Automated Test Equipment, ATE)는 장치가 설계 사양에 지정된 대로 작동하는 경우, 테스트 목적으로 출력 신호를 예상 값과 비교하기 위해 전기 신호를 반도체 장치에 제공한 후, 테스트 대상 장치(Device Under Test, DUT)를 이용해일련의 테스트를 수행함으로써 결함을 찾는 데 사용된다.

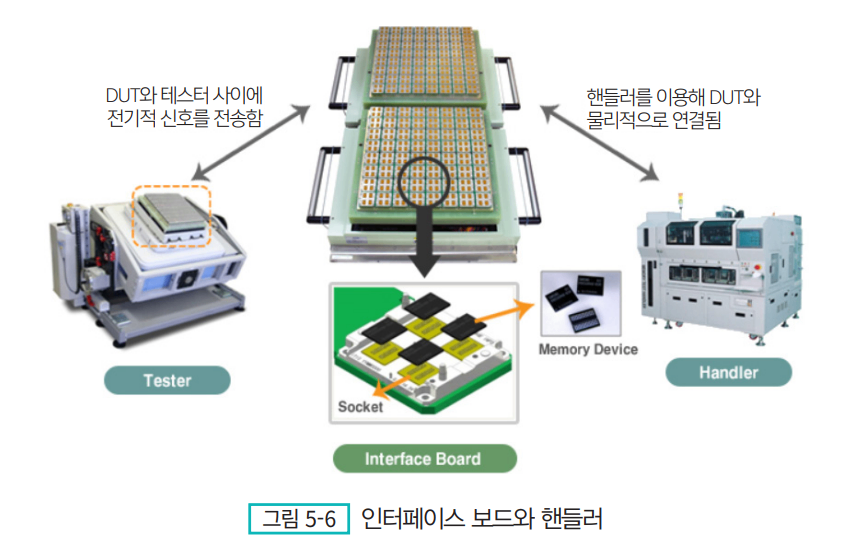

테스터는 대략 로직 테스터, 메모리 테스터, 아날로그 테스터로 분류되며 일반적으로 IC 테스트는 웨이퍼를 테스트하는 웨이퍼 테스트(Die sorting 또는 Probe test)와 패키징 후 최종 테스트 단계인 패키지 테스트의 두 가지 수준에서 수행된다. 이러한 웨이퍼 테스트에는 프로브와 프로브 카드를 사용하고 있으며, 패키지 테스트에서는 핸들러와 테스트 소켓을 테스터와 함께 사용하고 있다.

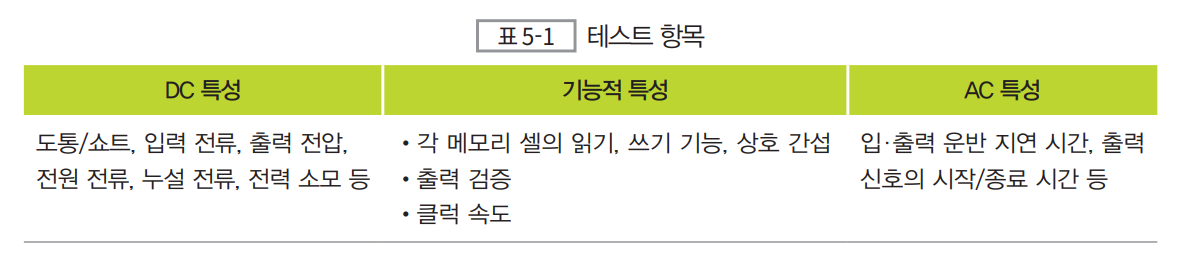

다음 AC 테스트는 웨이퍼 검사에서 시스템 클럭과 고주파 입력 신호를 사용하기 때문에 출력 점검이라 부르기도 한다. 이는 IC 소자의 타이밍을 측정하는 것으로, 입력 단자에 펄스 신호를 인가하여 입출력 운반 지연 시간(Access time), 출력 신호의 시작 시간과 종료 시간 등의 동작 특성을 측정한다. 이때 각 블록의 2차 하모닉 전류 누설, 목적으로 하는 주파수 이외의 주파수 성분인 불요파(Spurious wave), 증폭 이득 등 여러 가지 AC 특성을 테스트함으로써, 잡음(Noise)이나 누설량의 많고 적음, 그리고 그에 따른 허용치를 판별해 내어야 한다.

마지막으로 기능 테스트는 일반적으로 디지털 블록을 모두 포함하여 테스트해야 하지만 모든 블록이 각각의 테스트 포인트를 가지고 있는 것은 아니므로, 블록 단위로 모아서 특성 시험을 진행하게 된다. 주로 소자의 정확한 출력 검증과 클럭 속도 등을 측정한다. 메모리 IC 소자의 경우, 메모리의 실제 동작 속도에서 각 메모리 셀의 읽기/쓰기 기능이나 상호 간섭 등을 시험하며, 패턴 발생기에서 만들어진 검사 패턴을 규정의 레벨로 변환한 펄스를 피검사 IC 소자 즉, DUT(Device Under Test)에 인가하여 DUT의 출력 신호를 규정 레벨과 비교한다. 이 비교 결과를 패턴 발생기에서 발생한 출력 기대 패턴과 비교함으로써 동작의 양부를 검사하는 것이다. 일반적으로 AC 테스트와 기능 테스트를 겸한 다이내믹 기능 테스트로 실시한다.

이러한 반도체 칩의 검사 공정은 반도체 소자 생산에 있어서 많은 비용과 시간을 요구하며, 점점 기능이 많아지고 패키지 형태로 다양해지고 있어 IC 소자 검사에 복잡하고 가격이 비싼 검사 시스템이 필요하게 되었다. 즉, 고효율의 핸들러를 사용해야만 한다. 따라서 반도체 IC 소자의 기능이 향상됨에 따라 검사 공정에 드는 비용도 점점 더 높아지고 검사 시간도 더 길어지고 있는 상황이다. 따라서 이렇게 검사 시스템에 손실 요인이 발생하면, 이것은 제품의 수율에 큰 영향을 미치고 생산성을 좌우하는 주요 변수가 된다. IC 소자의 검사 공정은 보통 로트(Lot) 단위로 이루어지고, 하나의 로트에는 약 1,000개 이상의 IC 소자가 포함되므로, 하나의 로트를 검사하는 과정에서 검사 시스템의 실가동, 로딩, 인덱스, 언로딩, 순간 정지, 고장 수리, 로트 교체, 재검사 시간 등 많은 손실 시간이 발생한다. 종래의 검사 공정에서는 이러한 손실 요인을 작업자가 수작업으로 계산하거나 경험에만 의존하였기에, 손실 요인 데이터가 작업자마다 서로 다르고 신뢰도가 떨어질 뿐만 아니라 추적할 수 없는 손실 요인 데이터도 발생하였다. 이러한 이유 때문에, 손실 요인을 분석하고 관리하기란 사실상 불가능하였다. 하지만 반도체 집적회로 소자가 고성능의 소량 생산 방식으로 제조 판매되고 시장 적시성(Time-to-Market)의 요구가 점점 더 높아짐에 따라 검사 공정의 생산성과 수율 향상은 필연적인 과제가 되었기 때문에, 검사 공정의 손실을 최대한 줄이고 검사 시스템의 설비 가동률을 최적화하는 것이 절실하게 요청된다.

(2) 프로브 스테이션(Probe station)

반도체, PCB, 전자 회로, 부품의 조립 공정 등을 진행하기 전에 웨이퍼 상 수백, 수천 개의 칩이 제대로 완성되었는지 특성을 측정하는 과정이 필요하다. 그리고 이 과정에서 주요 측정 장비와 피 측정체를 연결하기 위해 사용되는 테스트 장비가 바로 프로브 스테이션(Probe station)이다. 프로브 스테이션은 프로브 카드(Probe card)나 프로브 헤드(Probe head) 등을 이용해 프로브 팁(Probe tip)을 웨이퍼 패드의 신호 연결 라인에 연결하며, 이는 초미세 회로 선폭에 적용하기 위해서 반드시 필요한 장비이다. 추가로 포지셔너(Positioner), 현미경 등을 장착함으로써 측정 채널의 수, 빠른 테스트 타임, 육안으로 구분하기 어려운 테스트 포인트들을 쉽고 빠르게 측정할 수 있는 기능을 갖추고 있고, 전체 웨이퍼 검사가 끝나면 웨이퍼를 다시 카세트로 옮겨 다음 웨이퍼 테스트를 위해 이송한다.

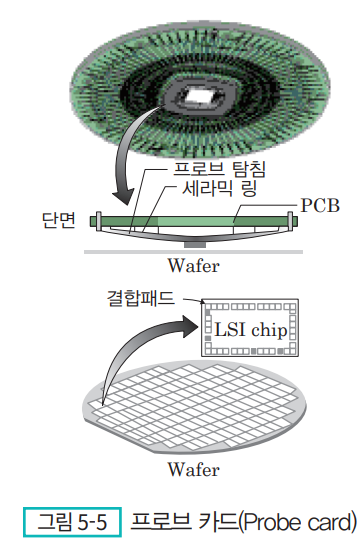

(3) 프로브 카드(Probe card)

일반적으로 프로브 카드(Probe card)는 반도체 칩의 공정 중 또는 공정이 완료된 후에, 그 결함 유무를 테스트하기 위하여 웨이퍼와 반도체 검사 장비를 전기적으로 연결시킨다. 그 후 주검사 장비의 전기적 신호를 웨이퍼에 형성된 반도체 다이(Die)에 전달하고, 반도체 다이로부터 돌아오는 신호를 반도체 주검사 장비에 전달하는 역할을 하는 장치이다.

프로브 카드는 웨이퍼 프로버에 도킹되어 다이 전극과 다이 테스터 사이의 측정기 역할을 하므로, 프로브 카드의 바늘이 다이의 전극에 접촉한 상태로 테스트가 수행된다. 이러한 프로브 카드 제작의 핵심이 되는 부품은 탐침(Needle)이며, 그 크기가 [μm] 단위로 상당히 미세하다. 만약 길이, 꺾임 각도 등 탐침 자체에 문제가 있다면 정밀한 반도체 웨이퍼 검사를 할 수 없을 것이다. 왜냐하면 탐침 길이가 일정하지 않은 경우 반도체 웨이퍼와의 접촉에 문제가 생겨 웨이퍼의 전기적 특성을 평가할 수 없게 되기 때문이다. 따라서 반도체 웨이퍼 검사에서 중요한 역할을 하는 탐침은 프로브 카드에 장착되기 전에, 반드시 이상 여부(탐침의 꺾임 정도, 길이 등)를 검사해야 한다. 탐침에는 현재 텅스텐 또는 다른 소재로 만들어진 바늘이 웨이퍼 검사용으로 사용되고 있다.

프로브 탐침의 종류에는 접촉 단자의 기계적인 동작 원리에 따라 캔틸레버(Cantilever), 버티컬 프로브(Vertical probe), 그리고 블레이드 탐침(Blade needle) 등이 있다. 최근에는 기술이 진보하여, 멤스(MEMS) 프로브 카드라는 것이 나왔는데, 이는 MEMS(Micro Electro Mechanical System), 즉 반도체 제조 공정을 활용한 초미세 탐침을 배열한 조립체를 말한다.

(4) 핸들러(Handler)

DRAM, 플래시 등의 메모리 소자부터 로직(Logic) 등의 시스템 반도체에 이르기까지, 다양한 반도체 제품들은 각각 쓰임에 따라 여러 단계의 품질 검증 과정을 거치게 된다. 이러한 과정 가운데 최종 단계에서의 검사 공정은 주검사 장비와 함께 테스트 핸들러라는 반도체 장비들에 의해 이루어지는데, 이때 테스터 핸들러는 반도체 후 공정 상에서 반도체 칩을 검사 장비로 이송하는 기능을 하는 장비이다. 즉 핸들러는 반도체 공정 중 최종 과정인 전기적 시험(Electrical test) 공정에서 반도체 칩들을 주검사 장비로 공급해주고, 검사 결과를 토대로 양품과 불량품을 등급에 따라 분류하는 자동화 장비인 것이다. 이렇듯 핸들러에 의해 검사 장소까지 이동한 반도체 칩이나 모듈은 검사가 이뤄지는 공간(Test site)에서 검사를 마친 후, 그 결과를 토대로 각각의 칩들이 등급별로 분류되는 과정을 거친다.

한편, 소자의 테스트 처리 속도 단위인 파라(Parallel)는 한 번에 전송할 수 있는 반도체 칩의 양을 의미한다. 예컨대 256 파라급 제품은 반도체 칩을 한 번에 최대 256개 옮길 수 있는 장비를 일컬으며, 한 번에 768개를 옮길 수 있는 디바이스라면 768 PARA라고 한다. 이렇게 동시에 768개 소자를 테스터에 정확히 접속하기 위해서는 컨택 프레스의 힘이 강해야 하고 온도 변화에 따른 위치 보정 및 재질 변경 등의 기술력이 요구된다.

최근에는 4차 산업혁명에 따라 사물 인터넷, 인공 지능 등의 반도체 기술이 급성장하고 있고 여러 개의 칩이 적층되는 MCP(Multi Chip Package)는 물론 DRAM에서 설명한 HBM(High Bandwidth Module)과 같은 다양한 형태의 첨단 패키지 수요가 급증하고 있다. 이에 반도체용 테스트 핸들러가 급성장하고 있는 상황이며, 생산성 향상과 검사 비용 절감을 위해 한 번에 많은 양의 칩을 검사하는 것이 중요해졌다.

(5) 번인(Burn-in) 장비

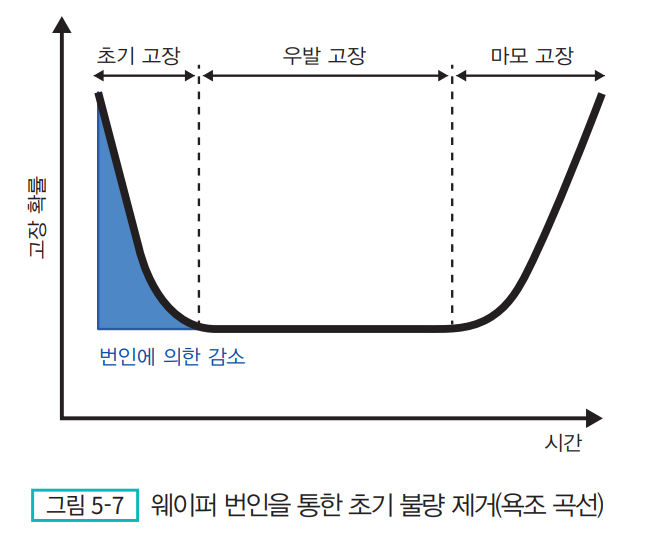

번인(Burn-in)은 시스템의 구성 요소들을 사용하기 전에 수행하는 테스트 과정을 말한다. 이 테스트는 반도체 소자의 신뢰성을 검사하기 위해 125도 정도의 고온 및 임계치에 가까운 전원 전압 조건에서 진행되며, 약 48시간 동안 특정 장애가 발생하도록 하여 제품의 부하에 대한 불량을 초기에 검출할 수 있다. 일종의 극한 상황 테스트라고 할 수 있으며, 이는 상온 동작 시에는 이러한 성능 차이가 잘 나타나지 않는 데 비해, 실리콘 소자의 온도가 높아짐에 따라 밴드 갭이 줄어들어 소자 특성 악화가 발생하는 현상을 이용한다.

그림에서 볼 수 있듯이 불량의 발생 빈도는 욕조 모양의 곡선을 보이는데, 이 욕조 곡선의 초기 고장 부분에 해당하는 특정 구성 요소의 불량을 감지하는 것이 목적이다. 번인 기간이 충분히 긴 번인 프로세스를 완료한 제품은 초기 불량이 거의 없는 것으로 신뢰할 수 있다.

다음 BIST는 테스터 기능의 일부로서, 테스트 패턴을 생성하기 위한 회로와 LSI 칩의 테스트 결과 및 예상 값을 비교하는 회로를 구축함으로써 칩 회로 내에서 테스트를 수행할 수 있다. BIST 회로에는 메모리 테스트용 메모리 BIST와 논리 회로 테스트용 논리 BIST가 포함된다. 따라서 LSI 테스터로부터 대부분의 테스트 패턴을 공급할 필요가 없으므로 칩당 더 적은 수의 테스트 핀으로 테스트를 수행할 수 있어 한 번에 테스트할 수 있는 칩 수를 늘릴 수 있다. 따라서 BIST 도입의 가장 큰 장점은 테스트 비용 절감이 되겠다.

한편, 번인은 다음 2가지로 크게 나누어진다.

① 패키지 레벨 번인(Package Level Burn-in)

패키지 레벨 번인은 고온의 챔버에 제품을 삽입하고 Standby 상태에서 소자 전원에 고객이 실제 사용하는 것보다 가혹한 조건의 고전압을 장시간 인가하여 신뢰성을 확보하는 단계로, 반도체 제품이 Active 상태가 되도록 각 핀에 신호를 인가하는 방식으로 진행된다.

② 웨이퍼 레벨 테스트 및 번인(Wafer-Level Test and Burn-in, WLTBI)

WLTBI는 반도체 칩을 웨이퍼 형태로서 전기적 테스트 및 번인을 받는 프로세스를 의미한다. 일반적으로 웨이퍼 프로버를 사용하여 본드 패드, 볼 또는 다이의 범프에 닿는 수백 또는 수천 개의 초박형 프로버 니들을 통해 웨이퍼의 모든 다이에 필요한 전기 여기를 공급함으로써, 웨이퍼 형태의 비용 효율적인 KGD를 용이하게 한다. 이는 SoC(System-on-Chip) 접근 방식의 대체 솔루션으로 SiP 및 MCM 기술을 가능하게 한다.

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기