패키지 공정

기출문제 풀이

기출문제 ❶

패키지 공정에 대해 아는 대로 설명해 보시오.

STEP1 접근 전략

난이도는 하 수준이며 자주 출제되는 문제이다.

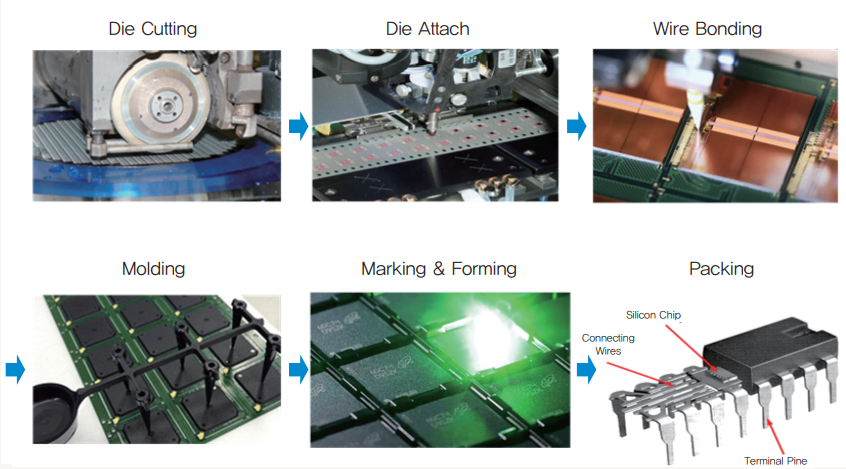

패키지 공정은 FAB 공정에서 만들어진 웨이퍼를 패키징하는 공정이므로 패키지의 공정 순서 및 역할에 대해 설명한다.

STEP2 답안 구조화 TIP

반도체 패키지 역할

- 보호 및 신뢰성 확보

- 전기적 연결

- 기계적 연결

- 열 방출

반도체 패키지 개발 동향

- 열 방출

- 고속 대응

- 소형화

- 다기능

- 고신뢰성

- 저비용

패키지 분류

- 기존 패키지: 플라스틱, 세라믹

- 웨이퍼 레벨 패키지: 재배선 RDL(Redistribution Layer), 플립 칩, TSV, WLCSP(웨이퍼 레벨 칩 스케일 패키지)

STEP3 모범답안

반도체 패키지 공정의 기본적인 목적은 크게 네 가지로 요약할 수 있습니다. 첫째, 충격 등 외부 환경으로부터 보호 및 신뢰성 확보, 둘째, 반도체 칩에 필요한 전원 공급, 셋째, 반도체 칩과 사용할 제품 간의 전기적 신호 연결, 넷째, 반도체 동작 중에 발생하는 열을 내보내기 위한 방열판 역할입니다.

고득점 답안 |

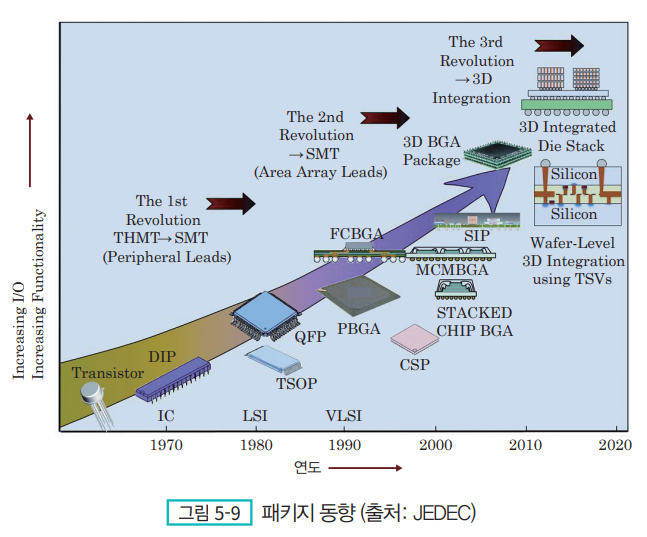

반도체 패키지는 위의 기본적인 세 가지 기능 이외에 응용 분야별로 요구하는 제품의 형태나 기술적인 요건에 맞추어 매우 다양한 종류의 패키지가 사용 및 개발되고 있습니다. 특히 기기의 소형화에 따라 패키지의 크기는 더욱 경박단소가 요구되고 있으며, 소모 전력의 최소화와 안정적이고 빠른 신호 전달을 위한 배선 설계, 그리고 최근에는 SiP(System in Package) 또는 PoP(Package on Package) 등의 새로운 패키지 기술이 요구되면서 가격 경쟁력까지 있는 저가의 패키지 기술이 중요시되는 추세입니다. |

꼬리 질문 1 후공정 순서에 대해 설명하시오. |

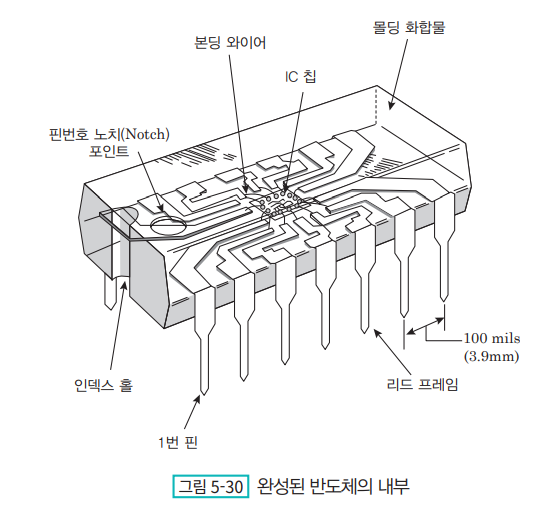

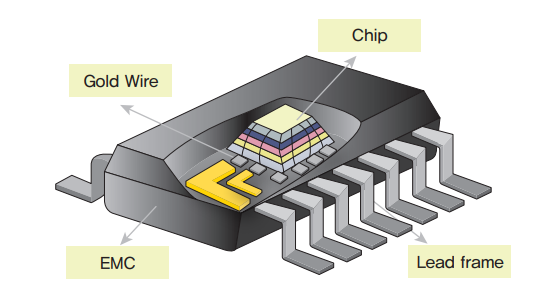

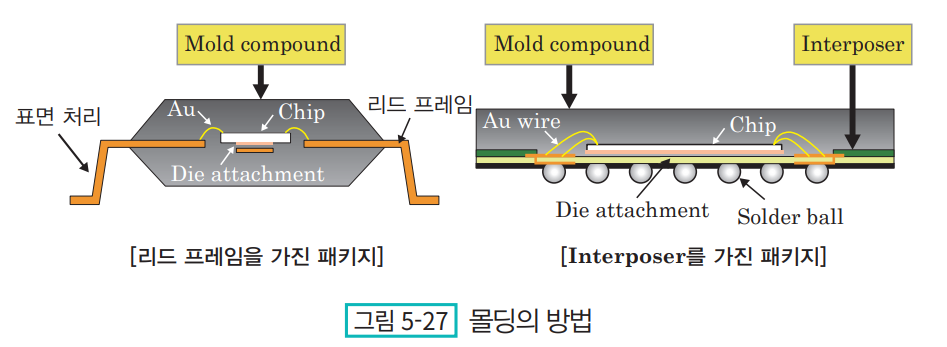

일반적인 반도체 후 공정(또는 패키지 공정)은 우선 FAB을 통해 만들어진 웨이퍼를 준비하여 스크라이브 라인을 따라 Diamond saw 장비를 이용해 Die(칩)를 하나씩 커팅해 줍니다. 커팅된 개별 Die는 회로 간에 전기 신호를 전달하는 리드 프레임에 고정되는데, 이 리드 프레임에 고정된 다이의 금속층인 패드와 전기 신호를 연결하기 위해 와이어 본딩(Wire bonding)을 하게 됩니다. 최근에는 칩의 사이즈를 줄일 수 있는 플립칩(Flip-Chip) 패키지가 많이 사용되고 있습니다. 와이어 본딩이 끝난 리드 프레임은 외부 환경으로부터 보호하기 위해 에폭시 몰딩 컴파운드로 몰딩을 하게 됩니다. 몰딩을 마친 후에는 제조사 및 제품명을 마킹하고 리드 프레임의 다리를 원하는 구조에 맞춰 포밍(Forming)합니다. 이렇게 공정이 완료되면 테스트를 통하여 양품을 선별하고 포장을 하여 고객사에 전달하게 됩니다.

|

기출문제 풀이

기출문제 ❷

와이어 본딩에서 일어날 수 있는 불량에 대해 설명하시오.

STEP1 접근 전략

난이도는 중 수준이며 자주 출제되는 문제이다.

이 문제는 실제 경험을 통해 알게 되는 내용이므로 현상에 대한 내용만 설명한다.

STEP2 답안 구조화 TIP

Q 와이어 본딩?

정의

불량의 원인

- 작업자의 부주의

- 장비의 문제

- 파라미터의 입력 실수

불량의 종류

- Broken wire

- Lifted bonding

- Missing wire

- Double bonding

- No wire

STEP3 모범답안

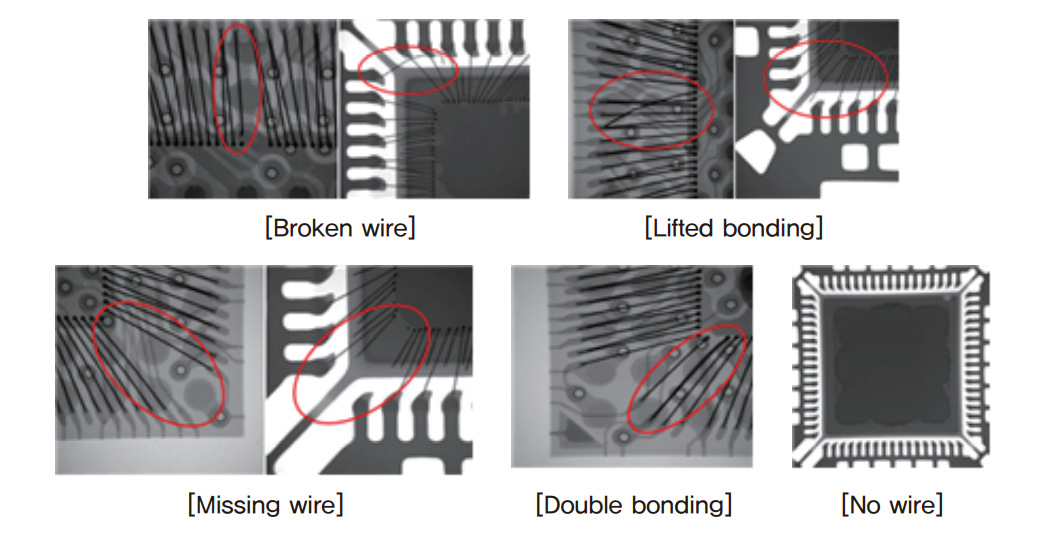

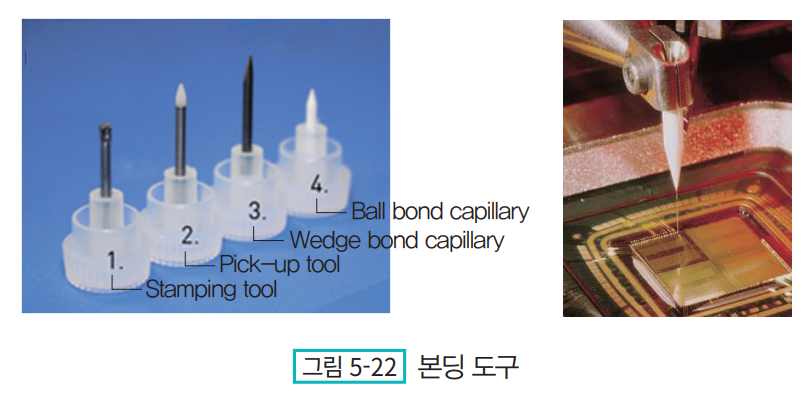

와이어 본딩 불량은 작업자의 부주의와 장비의 문제, 파라미터의 입력 실수에 의해 발생할 수 있습니다. 최적의 본딩 상태를 위해 칩의 패드와 리드 프레임 간에 주어진 수치대로 정확히 본딩이 형성되어야 하지만, 실제 현장에서는 많은 불량이 따르게 되고 경우에 따라 작업 중 와이어가 끊어져 작업자가 캐필러리로부터 와이어를 꺼내어 다시 작업하기도 합니다.

와이어 본딩 불량의 종류에는 Broken wire, Lifted bonding, Missing wire, Double bonding, No wire 등이 있으며, 이 중 Broken wire는 작업 중에 와이어가 끊어지는 현상으로, 와이어 재질이 불안정하거나 장비에서 와이어를 끌어올 때 과도한 힘으로 당기게 되면 발생합니다. 둘째, Lifted bonding은 실리콘 칩의 패드에 접착된 Ball 부분이 떨어지는 현상이며, 본딩 패드가 오염되었거나 와이어 본딩 장비에 잘못된 와이어 파라미터를 셋팅했을 때 발생하게 됩니다. 셋째, Missing wire는 대개 공급되는 와이어가 부족하거나 캐필러리가 막혀 공정 진행이 일시적으로 안 된 경우를 말하며, 드물게는 장비의 파라미터에서 빠져 있는 경우도 있는데 이때에는 만들어진 전체 제품이 불량이 되기도 하므로 주의해야 합니다. 넷째, Double bonding은 장비의 파라미터가 잘못된 경우와 기계의 오동작으로 인한 경우에 생기게 되는데, 작업을 마친 후 검사 과정에서 핀셋으로 두 개 중 하나를 떼어 내면 문제가 해결됩니다. 다섯째, No wire는 현장에서 가끔 발생하는 현상으로서, 와이어가 다 떨어지면 와이어 본딩 머신의 센서에서 해당 칩을 건너뛰고 다음 칩에 작업을 하게 되어 발생합니다. 이렇게 와이어가 떨어진 경우에는 본드 패드에 캐필러리가 찍고 간 흔적이 남게 됩니다.

핵심 이론 정리

1. 패키지 공정의 개요

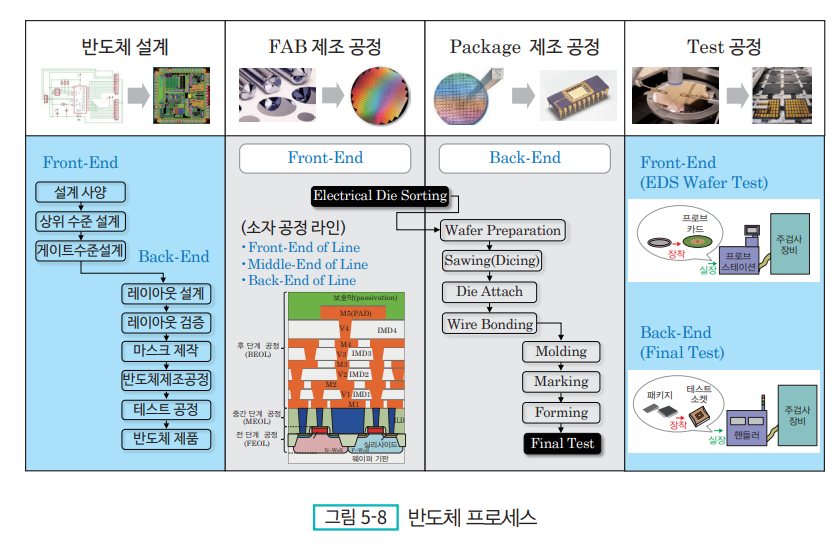

전 공정인 FAB 공정을 학습한 후, 후 공정으로 넘어가면서 각 공정에서의 용어에 대한 혼동이 올 수 있다. 이에 따라 간략히 용어 정리를 하고 넘어 가도록 한다. 먼저 반도체 제품 설계 또는 Foundry에서는 [그림 5-8]과 같이 설계 사양을 정하고 기능 검증을 하는 부분까지를 Front-End라고 하고, 로직 합성 또는 디지털 합성 부분부터 FAB을 포함해 하나의 제품이 나오게 되는 과정을 Back-End라고 분류하고 있다. 그리고 반도체 제조 공정에서는 웨이퍼 위에 회로를 형성시키는 전 공정(Fabrication)을 Front-End 공정, 후 공정을 Back-End 공정이라고 한다. 또한 소자 형성 시 금속배선 공정에서 언급한 것처럼, FAB 공정에서 트랜지스터가 만들어지는 과정을 FEOL(Front-End Of Line), 금속배선 공정 과정을 BEOL(Back-End Of Line)로 나누어 분류한다. 최근에 FinFET 등의 트랜지스터가 3차원으로 복잡하게 만들어지면서, 콘택 홀과 플러그 형성 단계를 별도로 MEOL(Middle-End Of Line)로 나누고 있다.

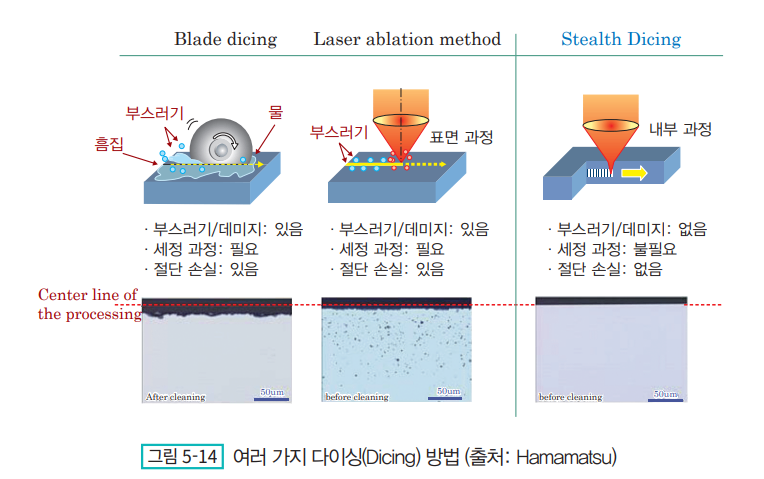

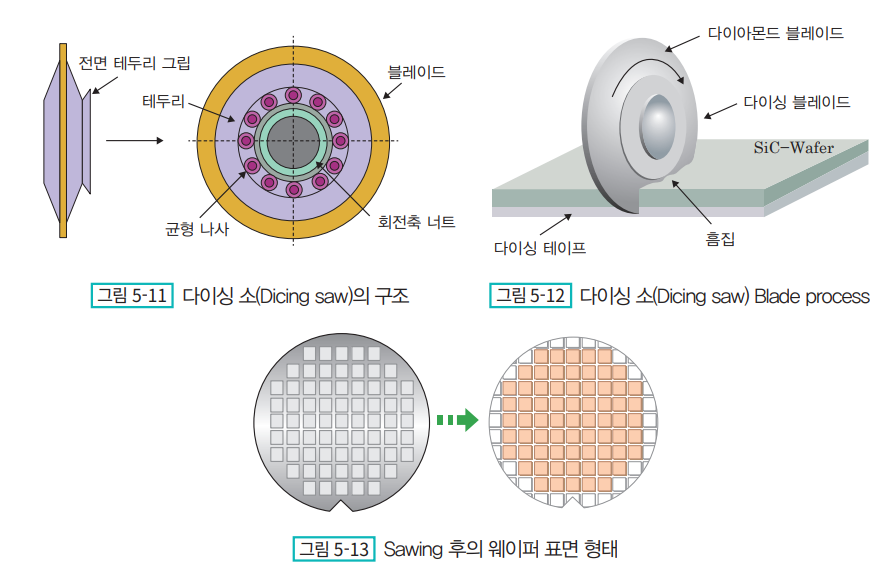

2. Die preparation

전 공정에서 웨이퍼 상의 회로 패턴 형성과 웨이퍼 검사가 종료되면, 어셈블리라고 하는 후 공정이 이루어진다. 그리고 그 후 공정의 첫 번째가 바로 Die preparation이라고 하는 다이싱(Dicing)이다. 즉, 웨이퍼를 절단하여 낱개의 칩으로 자르는 공정이다. 또한 다이싱은 스크라이빙(Scribing)이라고도 부른다. 그럼 지금부터 실제의 과정을 간략히 살펴보도록 하자. 먼저 웨이퍼 그대로는 두께가 두꺼워 자르기도 어렵고, 이 두꺼운 웨이퍼를 잘라 칩으로 사용할 경우에도 뒷면의 전기 저항이 높아 문제가 발생한다. 그러므로 먼저 뒷면을 얇게 연삭한 후, 그것을 UV 테이프로 부착하여 전체의 프레임을 고정한다. 그 다음은 다이싱 소(Dicing saw)라고 불리는 다이아몬드 미립자를 붙인 얇은 원형 날을 이용하여 웨이퍼를 종, 횡으로 자른다. 이때 다이싱 공정 중, 칩 내부에 기계적 결함이 발생하지 않도록 날의 압력이나 절단 속도를 제어할 필요가 있다. 이렇게 Die preparation은 상기의 과정처럼 칩을 조립하기 위해 웨이퍼를 조각내는 공정을 말한다.

(1) Wafer mounting

웨이퍼 프레임 로드(Load) → 웨이퍼 로드(Load) → 다이싱 테이프를 이용한 웨이퍼와 웨이퍼 프레임의 부착 → 테이프 절단 → 웨이퍼 언로드(Unload)

이러한 Wafer mounting 작업이 진행될 시에는 물리적인 힘에 의한 웨이퍼 자체 손상, 칩이 있는 부분의 스크래치, 테이핑 시 공기 방울의 생성, 테이프 자체가 균일한 장력이 없어 테이프가 비틀리는 현상 등을 미연에 방지해야 한다.

(2) Wafer sawing(Wafer dicing)

Wafer mounting 공정이 끝나면 바로 Wafer sawing 공정이 실시된다. 이는 앞에서 설명하였듯이 IC 패키지를 조립하기 위해 웨이퍼를 조각으로 잘라내는 공정이다. 절단하는 방법은 물리적인 톱(다이싱 소)을 이용하거나 레이저(Laser)를 이용하는 방법이 쓰이고 있다. 다이싱(Dicing) 공정 중에 실리콘 웨이퍼는 다이싱 테이프에 붙여지고, 테이프의 한 면에 접착 성분이 있어 웨이퍼 프레임에 고정되도록 한다. 이후 웨이퍼가 조각 모양으로 절단되면, 테이프에 남아 있는 부분을 다이(Die)라고 부르고, 이 다이가 리드 프레임(Lead frame)이나 PCB(Printed Circuit Board) 기판에 붙여지게 된다. 또 웨이퍼 절단 시 잘려나가는 부분은 다이 스트리트(Die street)라고 불리며 일반적으로 폭이 75μm 정도 된다. 웨이퍼 절단 공정 후 테이프에 남아 있는 다이는 다시 Die bonder, Die sorter에 의해 다음 공정이 진행된다. 이때 다이의 크기는 일반적으로 0.5~35mm 정도가 되며 직선으로 가공되기 때문에 직사각형이나 정사각형 모양을 갖는다.

① 다이싱 소(Dicing saw)

다이싱 소(Dicing saw)는 웨이퍼를 절단하는 데 사용되며, [그림 5-11]의 구조와 [그림 5-12]와 같은 공정 형태로 진행된다. 공정 순서는 웨이퍼 프레임(Wafer frame)에 웨이퍼를 고정시키고 다이싱 장비(Dicing machine)에 로드하여 알려질 부분을 맞춘다. 그 다음 웨이퍼는 고속으로 회전하는 다이아몬드 Wheel blade에 의해, 두께별 미리 프로그램된 크기로 절단된다. 이때 잔류물은 고압의 초순수(DIW)를 뿌려 제거한다.

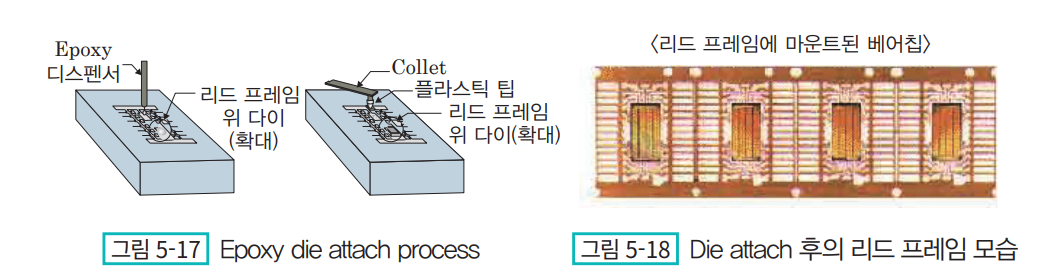

3. Die attach

상기의 내용들은 웨이퍼 상에 반복적으로 만들어진 칩을 자르는 다이싱 작업에 관한 내용이었다. 이제는, 이렇게 잘라진 칩 또는 다이를 완성된 제품의 기판에 삽입하고 납땜하여 전기적인 회로가 구성될 수 있게 하는 작업이 진행되어야 한다. 이러한 과정의 공정을 Die attach(Die mount 혹은 Die bond)라고 한다. 이것은 완성된 IC 칩을 다이 패드(Die pad)나 반도체 패키지의 리드 프레임에 탑재시키는 공정으로, 크게 Adhesive 방식과 Eutectic 방식으로 나뉜다. 공정 과정은 UV 테이프 위에 배열된 칩을 마운트 장비(Mounter)의 진공 척(Vaccum chuck)으로 픽업하여 리드 프레임 위에 붙이는 순서이다. 이를 위해 은 도금된 리드 프레임 부분 위에 은 페이스트를 둥근 점 형태로 찍고, 여기에 칩을 접착시키게 된다. 이러한 Die attach 공정이 중요한 이유는 후 공정에서도 견딜 수 있는 충분한 강도의 접착력으로 칩을 고정시킬 수 있기 때문이고, 또 적절한 열 전도도 및 전기 전도도를 부여함으로써 칩에서 발생하는 열을 방출시켜 칩 표면의 전하 축적을 방지할 수 있기 때문이다.

(1) 리드 프레임(Lead frame)

리드 프레임이란 반도체 패키지의 주요 부품으로서, 반도체 칩과 외부 회로를 연결시켜 주는 전선(Lead) 역할과 반도체 패키지를 전자 회로 기판에 고정시켜주는 버팀대(Frame) 역할을 동시에 수행하는 금속 기판을 말한다. 이 리드 프레임은 IC칩을 탑재 및 고정하는 다이 패드부와 IC칩 상의 단자와 선을 연결하는 Inner 리드부, 그리고 외부 단자가 되는 Outer 리드부로 구성되어 있다. 리드 프레임의 가운데에 IC칩을 올려놓고 세라믹스 등의 패키지를 씌우면 반도체 기기가 되는 것이다. 따라서 리드 프레임이 가져야 할 조건으로는 다음과 같은 것들이 있다.

기계적인 강도가 강할 것

소자가 발생하는 열을 방열하기 위해 열전도성이 클 것

열팽창 계수가 작을 것

기계적 가공성이 좋을 것(펀칭, 절곡, 절단)

리드의 인성이 좋을 것(구부림 동작을 반복할 때 손실이 없을 것)

도금과 납땜이 용이할 것

내산화성 및 내열성이 클 것

내압력성, 내부식성, 내환경성이 좋을 것

한편, 리드 프레임을 사용하는 패키지는 원가가 저렴한 구리 리드 프레임을 사용하기 때문에 생산 원가가 저렴하다는 장점을 가진다. 대체로 전형적인 패키지 구조를 가지며, 구조가 상대적으로 간단해 출력 단자수가 적은 소자에 적합하다. 특히 저렴한 가격과 작은 크기, 그리고 우수한 전기 및 열적 특성 때문에 무선 이동 통신 제품에 많이 사용된다.

(2) Die attach

다이싱(Dicing)을 통해 잘라진 하나의 다이를 Polyimide, Epoxy 등의 접착 물질을 사용한 Adhesive die attach 공정을 통해 리드 프레임 위에 부착시키는 방법이다. [그림 5-17]과 같이 다이 패드에 정확히 맞추어진 양 만큼 Epoxy를 바르고, 하나씩 잘라진 웨이퍼에서 다이를 가져와 접착시키는 과정으로 진행된다. 이 과정에서 웨이퍼 테이프로부터 다이를 떼어낼 때 ‘Collet’으로 알려진 로봇 암(Arm)이 대부분 사용되는데, 칩의 표면에 손상이 가지 않도록 하면서 Die bond에 정확하게 위치시켜 접착해야 한다.

4. Wire bonding

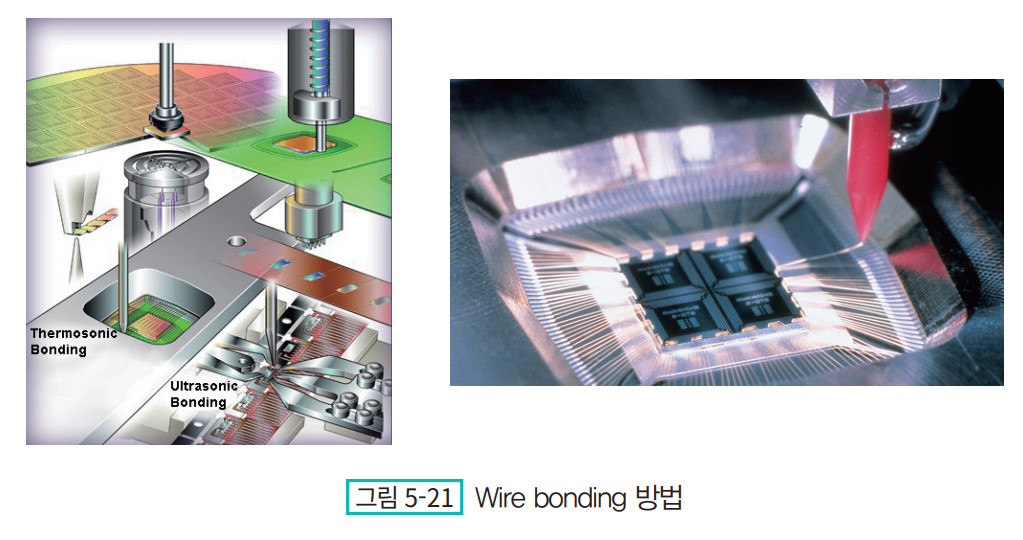

(1) 와이어 본딩(Wire bonding)

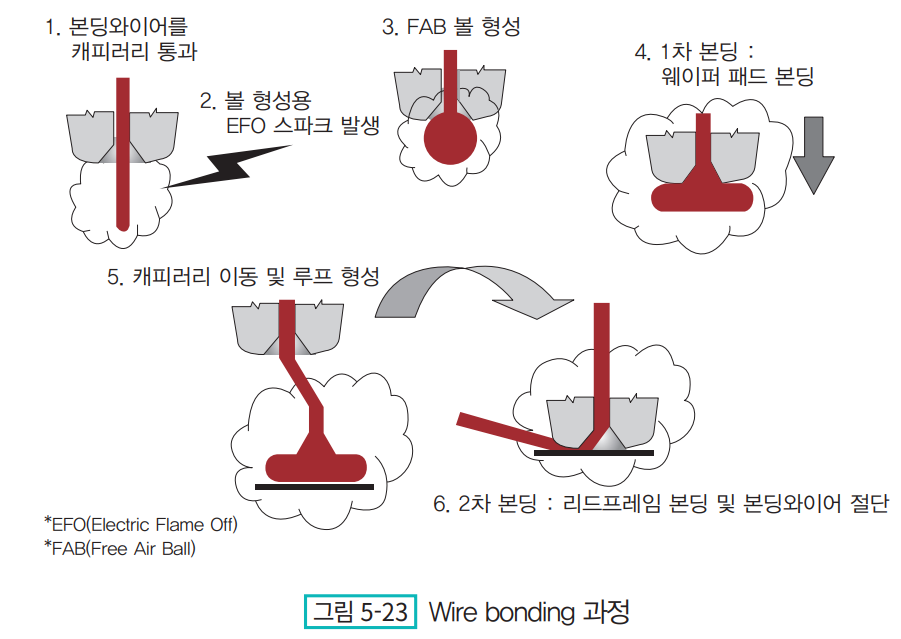

회로가 구성된 다이를 리드 프레임을 이용해 패키지의 리드에 매우 가는 고순도선으로 연결하는 공정을 Wire bonding이라 한다. 반도체 칩이 제대로 동작하기 위해서는 외부와 전기적으로 연결되어야 하므로, 와이어 본딩 공정의 미세한 금속선으로 반도체 칩의 끝부분과 다른 전기적 연결단자를 연결해야 한다. 이때 구리(Cu)는 금(Au)보다 장점이 많아, 전기적 도통을 위한 물질로서 사용량이 증가되고 있는 상황이다. 저렴한 가격과 뛰어난 열/전기 전도성이 주된 장점이며, 이 때문에 Cu 와이어는 고전류 또는 고출력 제품의 적용에 적합하다. 현재 Cu 와이어 본딩을 적용하는 표면 처리에는 전해 Ni/Au가 일반적이고 Au의 두께는 0.5μm 정도이다. 만약 이 Au을 다른 저렴한 금속으로 대체할 수 있다면, 가격 절감 효과는 매우 클 것이다. 현재 전해 Ni/Au를 대체 가능한 표면 처리로는 ENEP(Electroless Nickel Electroless Palladium)이 적합하며, 이미 Cu 와이어 본딩 특성에 대한 신뢰성 부분은 반도체 분야에서 증명되고 있다. 사실 반도체 칩의 표면에 선을 붙이는 것은 어려운 작업이다. 왜냐하면 칩 연결에 쓰이는 와이어가 시간이 지나도 제 성능을 낼 수 있도록 전기적 연결이 좋아야 하기 때문이다. 한편, 초창기 상업적인 Wire bonding 방법은 칩에 직접 납땜을 하는 방법이었다. 이러한 납땜법은 생산성이 좋지 않았고, 반도체 물질과 접합하는 다이오드 부분이 약해져서 성능을 떨어뜨리는 결과를 가져오기도 했다. [그림 5-20]은 Bonding용 금 와이어를 보여주고 있다.

5. 플립 칩(Flip-Chip) bonding

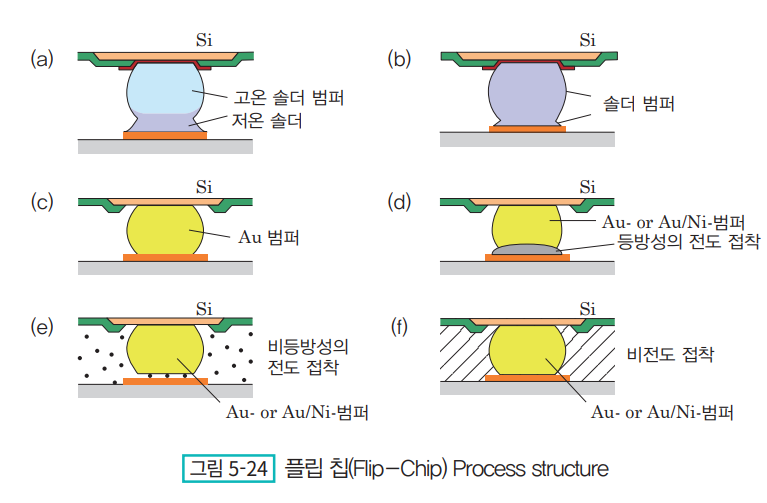

반도체 칩을 제조하는 과정에서 웨이퍼 단위의 식각(Etching), 증착(Evaporation)과 같은 공정을 마치면 테스트를 거쳐 종적으로 패키징(Packaging)을 하게 된다. 패키징은 외부 단자(Outer lead)가 형성된 기판에 칩이 실장되고 몰딩(Molding)을 하는 것을 말한다. 외부 단자는 기판과 칩을 전기적으로 연결하는 단자를 말하며, 이 외부 단자와 칩의 연결 형태에 따라 Wire bonding, Flip-Chipbonding이라는 말을 하게 되는 것이다. Wire bonding은 리드가 형성된 기판(컴퓨터의 메인보드 같은 기관이 아니다)에 칩을 올려 두고 미세 와이어를 이용해 외부 단자와 전기적으로 연결된 내부 단자에 반도체 칩의 전극 패턴을 연결하는 방식이다. 그리고 Flip-Chip bonding은 전극패턴 혹은 내부 단자에 Solder ball 등의 돌출부를 만들어 주고 기판에 칩을 올릴 때 전기적으로 연결되도록 만든 것이다. 그래서 Flip-Chip bonding을 이용하면 Wire bonding만큼의 공간을 절약할 수 있어 작은 패키지의 제조가 가능해진다. 또한 플립 칩의 뛰어난 열 성능은 내열성이 낮은 방열판 부분이 있기 때문에 가능한 것인데, 이 경우 열은 Thermal ball과 내, 외부의 방열판을 통해 방산된다. 낮은 접합면과 Case 간의 열저항은 방열판 커버와 다이 간 접촉에 의해 이루어진다. 밀착성과 열전도성을 좋게 하기 위하여 다이와 방열판 커버 사이에 Thermal grease(Thermal compound)를 얇게 바른다. 열성능을 향상시키기 위한 외부 방열판은 외부 커버에 쉽게 부착할 수 있기 때문에 낮은 열저항을 이용할 수 있다. 플립 칩 패키징의 또 한 가지 중요한 이점은 전기적 성능이 뛰어나다는 점이다. 플립 칩은 패키지에서 병목 작용을 하는 와이어 본드가 필요없기 때문에 전기 성능이 좋다. 한편 오늘날 대부분의 전자 소자는 고주파에서 작동하기 때문에 신호의 무결성(Integrity)이 중요한 고려 사항으로 대두되는 상황이다. 과거에는 2~3GHz가 대부분의 패키지에서 최고 한계치였으나 플립 칩은 기판 기술에 따라 10~40GHz의 주파수 지원도 용이하다.

i) 칩 표면에 범프(Bump)를 입힌다.

ii) 범프(Bump)된 칩을 기판에 Face-Down으로 장착한다.

iii) 칩과 기판 사이의 빈 공간을 비전도성 물질로 채우는 Under filling 공정을 한다.

(1) 플립 칩 범핑(Flip-Chip bumping)

범핑(Bumping)이란 웨이퍼 Al 패드 위에 금 또는 납땜(Solder) 등의 소재로 5~10μm 크기의 외부 접속단자(Bump)를 형성해 주는 차세대 공정을 말한다. 다이 표면의 Bump들은 여러 기능을 수행할 수 있는데, 기관과의 전기적 연결, 칩에서 기관으로 열을 전달함으로써 열 방출, 칩과 칩 사이 또는 칩과 기판 사이에 공간을 제공하여 전기적 쇼트를 방지, 물리적으로 칩을 지탱하는 등의 역할을 한다.

땜납 범프(Solder bumping)는 스퍼터링(Sputtering), 플레이팅(Plating) 등에 의해 UBM(Under Bump Metallization)을 칩에 도포한다. UBM을 입히는 공정은 본드 패드에 있는 산화막층을 제거하고 땜납(Soldering)할 부분을 정하는 데 쓰인다. 그 다음 UBM층 위에 증착(Evaporation), 전기 도금(Electroplating), 스크린 인쇄(Screen-Printing), 미세 증착(Needle-Depositing) 등의 방식으로 땜납(Solder)을 도포하게 된다.

(2) 범핑 공정

① 증발 범퍼 공정(Evaporated bump process)

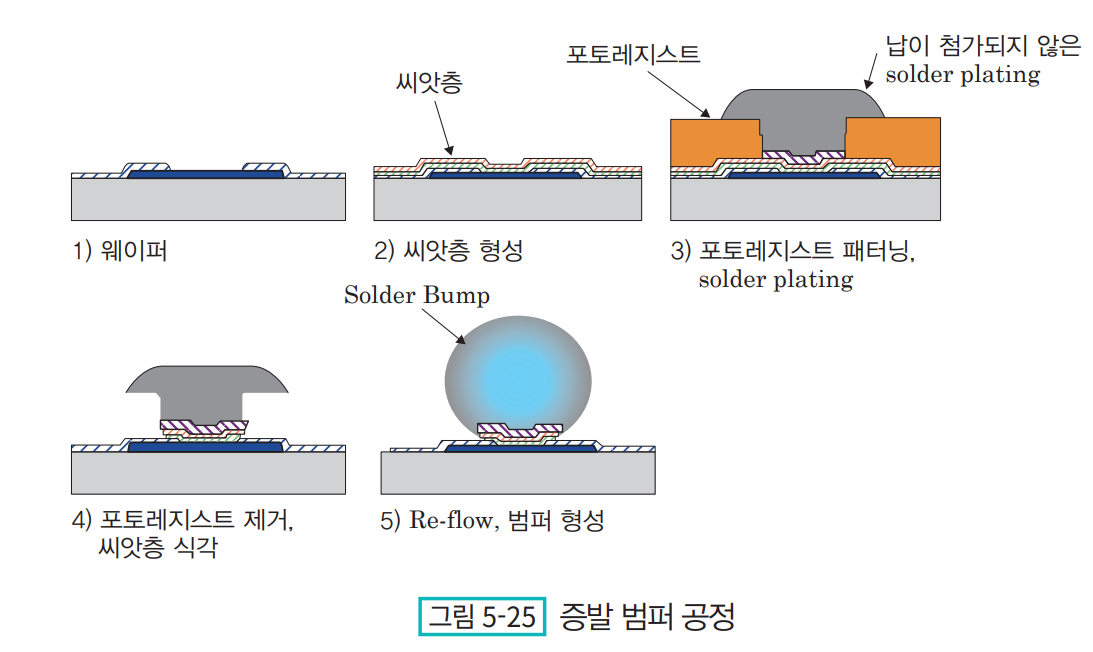

증발에 의한 UBM 및 솔더 범프(Solder bump)의 형성은 일반적으로 IBM 및 C4(Controlled Collapse Chip Connection) 프로세스에 의해 실행된다. 통상 웨이퍼는 금속 범퍼 증착 전에 산화물 또는 포토레지스트를 제거하기 위해 세정 공정이 수행되는데, 세정 공정 또한 웨이퍼 보호 및 본드 패드의 표면을 거칠게 하여 UBM의 보다 나은 접착을 촉진시키는 역할을 한다. 그리고 세정 공정 이후에는 범퍼의 UBM 기초 구조 중 첫 번째 금속층이 금속 마스크(일반적으로 몰리브덴)를 이용해 웨이퍼를 패턴화하는 스퍼터링 공정에 의해 도포된다. 이 첫 번째 금속층은 대개 티타늄과 내열성의 다른 금속이 혼합된 상태이며, 디바이스와 전기 접촉성을 최적화시킨다. 이렇게 함으로써 웨이퍼 표면에 강한 접착성을 가지게 되고 솔더 범프(Solder bump)와 다이 금속층 간의 확산 장벽(Diffusion barrier)으로서 작용하게 된다. 그 다음 구리와 같은 금속을 증착하여 UBM층을 형성시킨다.

② 전기 도금 범퍼 공정(Electroplated bump process)

플립 칩 어셈블리를 위한 솔더 범프는 칩의 입출력(I/O) 패드에 전기 도금되어 증착된다. 웨이퍼 범핑의 기본 공정 단계는 씨앗층(UBM)의 스퍼터링, 포토 공정(포토리소그래피), 범프 금속의 전기 도금, 씨앗층의 식각 및 리플로우(Reflow)이다. 이 중 전기 도금은 높은 증착률과 잘 알려진 화학 반응 및 우수한 증착 균일성으로 인해 플립 칩 범프의 증착에 널리 사용되어 왔다. UBM과 솔더 범프는 동일한 포토레지스트 마스크를 사용하여 순차적으로 증착되며, 전기 도금 공정은 전형적으로 하나의 마스크층 및 하나의 포토 공정 과정을 필요로 한다. UBM/솔더는 포토레지스트 개구에서 전기적으로 증착되고 포토레지스트의 제거 후에, 증착된 금속층은 웨이퍼로부터 전도성 씨앗층을 식각하기 위한 마스크로서 작용한다. 이는 전기 도금의 단순성에도 불구하고, 공정이 다른 재료의 화학적 호환성에 매우 민감하다.

6. 몰딩(Molding)

7. 마킹(Marking) 공정

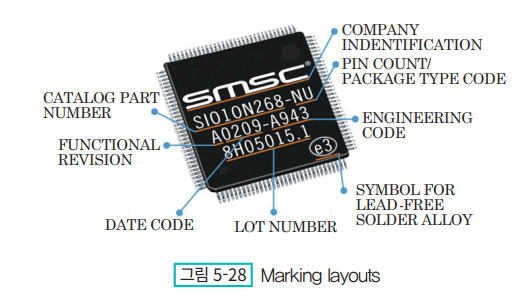

마킹(Marking) 공정은 조립 공정이 완료된 패키지 위에 제조사에서 필요로 하는 회사의 로고, 제품명, 부품 이름, 그리고 제조 일자를 구분할 수 있는 여러 가지 형태의 마킹을 하는 것이다. 이러한 표식들은 조립 공정 중에 새겨질 수도 있고 또는 테스트 공정 중에 새겨지기도 하지만, 대부분은 조립 공정에서 작업이 완료된다. [그림 5-28]은 흔히 사용하는 마킹 방법의 Layout을 보여주고 있다.

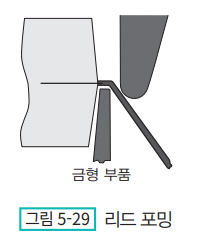

8. 리드 코팅(Lead coating)과 포밍(Forming)

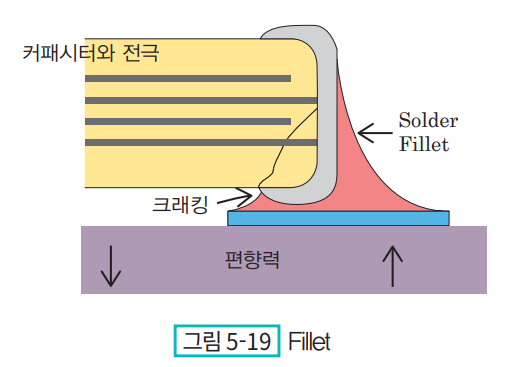

앞의 반도체 재료에서 설명하였듯이, Lead coating 공정은 만들어진 반도체의 리드를 부식으로부터 보호하고 전기 전도성을 좋게 하기 위해 금속 물질로 코팅하는 공정이다. 이 공정이 끝나면 리드 프레임을 사용 용도에 맞게 포밍(Forming)하여 IC를 완성시키게 된다. 이러한 공정의 목적은 리드들의 오염 방지, 마찰에 의한 손상 방지, 접착력 강화 등에 있으며, 반도체 산업에서의 리드 코팅 공정은 크게 두 가지로 나눌 수 있다. 주석(Tin)과 같은 순수 금속을 쓰는 것과 Tin 및 Lead와 같은 합금을 쓰는 방법인 Plating 공정, 그리고 Solder와 같은 물질로 표면을 도포하여 금속 접합을 하는 공정인 Coating 공정이 바로 그것이다. 이 중 Solder coating 공정에서 중요한 변수는 표면 장력 즉, Solder에 의해 코팅될 표면이 코팅 물질을 흘러내리지 않도록 붙잡고 있어야 한다는 것이고, 코팅 공정 중 표면에 Solder가 퍼지는 정도에 따라 Solder층이 생성된다. 다음 Tin plating은 전도 물질이나 전해질 용액에 Plating하고자 하는 물질을 넣고 전류를 가함으로써 코팅이 이루어진다. 이때 전기 도금(Electroplating) 시스템은 다음과 같이 구성된다.

음극(Cathode): 코팅될 표면

양극(Anode): 코팅하고자 하는 소스 물질

전해질(Electrolyte): 양극(Anode)에서 음극(Cathode)으로 금속 이온을 전달하는 역할을 하는 용액

전력원(Power source): 양극(Anode) 쪽의 소스 물질을 금속 이온화시키는 전류나 에너지

코팅이 이루어지는 음극(Cathode) 측에서는 이온들이 소모되는 환원 반응이 일어난다. 이와 반대로 소스 역할을 하는 양극(Anode) 측에서는 산화 반응이 일어나며 다음과 같은 식으로 표현된다.

환원 반응:

산화 반응:

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기