GAA MOSFET

예상문제 풀이

예상문제 ❶

GAA(Gate All Around) MOSFET에 대해 설명하시오.

STEP1 접근 전략

설명형 문제로 난이도는 중상 수준이며, 최신 로직 반도체 소자인 GAA MOSFET에 대한 문제로서, 최신 소자 트렌드에 대한 관심을 알아 보고자 하는 의도에서 출제 가능성이 있다.

GAA 구조의 출현 이유 및 FinFET 대비 장단점을 설명한다.

GAA의 종류 및 제작 핵심 공정은 시간적 여유를 고려하여 설명할 수 있도록 한다.

STEP2 답안 구조화 TIP

Q GAA MOSFET?

평판 → FinFET → GAA

장점: SCE↓,

I_{DS} ↑, Scaling↓, 채널 폭 양자화 개선단점: 공정 난이도↑

NW 기반: 면적↓, 전력↓, 공정 난이도↑

NS 기반: 성능↑, 공정 난이도↓

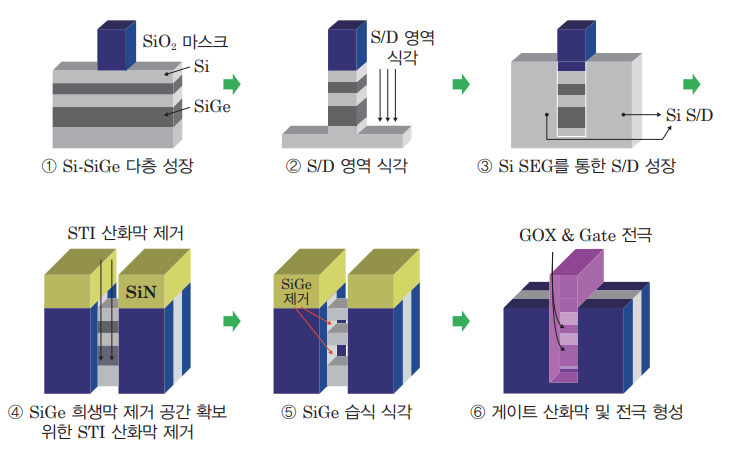

핵심 공정: 저결함 Si/SiGe 결정 성장, Si SEG, SiGe 선택적 습식 식각

STEP3 모범답안

14nm 이하 공정에서는 기존의 평판 MOSFET의 단채널 현상을 극복하기 위해 물고기 지느러미(Fin) 모양의 3차원 입체 구조의 FinFET이 적용되고 있습니다. 그러나 3nm 이후 공정에서는 FinFET 또한 한계에 이르게 되었고 이를 극복하기 위해 새롭게 탄생한 것이 바로 GAA(Gate All Around) 구조입니다. GAA 소자는 채널의 4면을 게이트가 감싸고 있어 게이트의 채널 제어 능력을 극대화한 구조로, 이로 인해 높은 전력 효율을 얻을 수 있는 소자입니다. 한편 게이트가 트랜지스터를 원활히 제어하기 위해서는 채널의 폭(Width)을 가능한 얇게 만들어야 하는데, 그에 반해 전류 구동 능력은 채널의 폭에 비례하므로 FinFET의 경우는 얇아진 Fin의 폭을 보상하기 위해 Fin의 높이(Height)를 높게 하거나 복수 개의 Fin을 2차원적으로 배열하여 전류 구동 능력을 올려야 하므로 공정의 난이도가 상승하고 소자의 면적이 증가하게 됩니다. 또한 FinFET의 채널 폭은 항상 Fin 수의 배수가 되므로 소자의 유효 폭이 양자화되는 문제가 있어 설계의 자유도가 떨어지는 문제가 있습니다. 이에 비해 GAA 구조는 전류 구동 능력 증가를 위해 수평적인 배열이 아닌 수직으로 Si 채널을 적층하므로 미세화가 용이하며 연속적인 채널 폭 설계로 소자의 유효 폭이 양자화되는 문제를 피할 수 있어 효율적인 칩 설계가 가능합니다.

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기