Short channel effect가 무엇이며 그 방지방법에 대해 설명해보세요.

[쇼트 채널 효과(short channel effect)]

단채널 효과라고도 한다. MOS FET 등에서 게이트의 길이(소스, 드레인 간의 거리)가 짧은 경우의 영향이다. 드레인 전압 VD를 일정하게 하고 채널 길이를 짧게 하면 드레인과 소스로부터의 공핍층이 게이트 밑의 기판 영역으로 삐어져 나온다. 그래서 채널 부분의 전위 장벽이 저하되면 드레인 전압의 약간의 증가에 의해 드레인 전류 ID가 급증하고, 이것이 진행되면 공핍층의 접촉에 의한 펀치스루(punch-through)가 생긴다.

일반적으로 트랜지스터의 게이트의 길이가 점차적으로 줄어듦으로서 발생하는 문제점 중에 하나가 단채널 효과이다. 단채널 효과는 여러 가지 현상을 통칭하는 것으로, 대표적인 특성이 트랜지스터의 누설전류가 증가되고, 항복전압(Punchthrough voltage)이 감소되며, 포화 전류 특성을 보이지 않고 드레인 전압에 따라서 전류가 계속 증가하는 현상이 발생된다.

[방지 방법]

① 드레인 구조: 이것을 방지하기 위해 드레인의 채널측에 n-층을 두고 공핍층의 전계를 저하시켜, 열전자의 발생을 억제하여 ID의 급증을 방지하도록 한다. 이와 같이 n-를 만들어 넣은 구조를 가볍게 도프한 드레인 구조(LDD)라 한다.

② 드레인 접합 깊이를 얕게: 소스 및 드레인의 접합 깊이를 얕게 하는 방법이다. 그러나 접합의 깊이가 줄어듦에 따라서 소스 및 드레인의 면저항이 급격하게 증가하는 문제점이 있다.

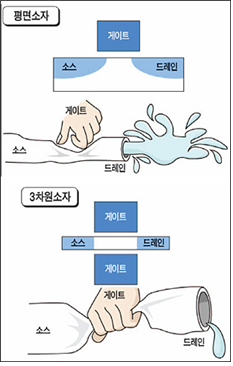

③ 실리콘 채널의 전면 감싸기(FinFET): 실리콘 채널의 사방에 게이트가 만들어진 구조로, 3차원 소자(핀펫)는 폭이 좁은 채널을 2개 이상의 게이트가 부분 또는 전면을 감싸고 있어 누설되는 전류를 훨씬 효과적으로 줄일 수 있다.

④ GAA(Gate-All-Around) FET: 게이트가 채널의 사방(상·하·좌·우)을 완전히 둘러싸는 3차원 트랜지스터 구조이다. 채널이 얇은 판(sheet) 형태일 경우 나노시트(Nanosheet) FET, 선(wire) 형태일 경우 나노와이어(Nanowire) FET라고도 부른다. FinFET이 게이트가 채널의 3면만 감싸는 데 비해, GAA는 채널 전면을 제어할 수 있다는 점에서 보다 강력한 게이트 제어력을 갖는다. 또한 나노시트의 폭과 두께를 독립적으로 조정할 수 있어 같은 면적에서 더 큰 On-Current를 확보하는 것이 가능하다. 나아가 nFET과 pFET을 수직으로 적층하는 CFET(Complementary FET) 구조로 발전시키면 면적을 대폭 절감할 수 있는 잠재력도 갖추고 있다.

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기