MOSFET의 구조에 대해 설명해보세요.

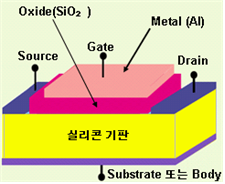

MOSFET(Metal-Oxide Semiconductor Field Effect Transistor) 또는 MOS 트랜지스터는 금속막, 산화막, 반도체 영역으로 구성된 트랜지스터의 일종이다. MOS 트랜지스터의 source와 drain은 실리콘 표면에 생성되며 gate의 양쪽에 배치 되게 된다. 반도체 영역은 대부분 트랜지스터 역할을 하기 위해 표면이 단결정 실리콘으로 도핑 되어 있다. 산화막은 실리콘 산화막 형태로 구성되는데 금속막과 절연을 하는 기능을 한다. 금속막은 MOS 트랜지스터에 전압을 인가하기 위한 지점으로 사용된다.

MOSFET의 구조는 아래 그림에 나타나 있다. 실리콘 기판 위에 source, drain 단자를 만들고 이 단자에 전류를 흘려준다. Gate 단자에는 전압을 걸 수 있도록 되어 있는데 맨 상층부는 금속으로 주로 Al 이 쓰이고 금속층 밑에 산화막 보통 SiO2가 쓰여서 MOS 구조를 하고 있다. 이 구조의 특징은 중간층에 절연막이 있다는 것이다. 그래서 gate에 어떤 (+), (-)가 걸리더라도 전류가 흐를 수 없다는 것이다. 따라서 입력 임피던스가 약 1,013Ω 정도로 매우 크다. 또한 실리콘 기판 하부 쪽으로 substrate 단자가 하나 더 있는데 동작의 단순화를 위해 보통 source 단자 쪽과 연결하여 사용한다.

Source와 drain이 P형 반도체이고 표면이 N형 반도체일 경우 MOS 트랜지스터는 P 채널 MOSFET 또는 PMOS라 불리며 source와 drain이 N형 반도체이고 표면이 P형 반도체일 경우 N 채널 MOSFET 또는 NMOS라 불린다.

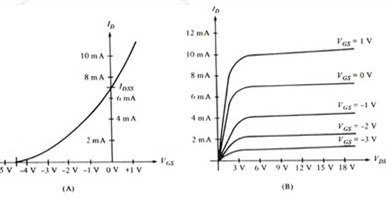

<소스와 드레인 사이의 전류>

[트랜지스터 구조의 진화]

반도체 공정의 미세화가 진행됨에 따라 기존의 평면(Planar) MOSFET 구조는 단채널 효과(SCE) 억제에 한계를 보이기 시작하였다. 이를 극복하기 위해 채널을 얇은 핀(Fin) 형태로 세우고 게이트가 3면을 감싸는 FinFET 구조가 도입되었으며, 인텔은 2011년 22nm 공정부터 이를 양산에 적용하기 시작하였다. 최근에는 FinFET의 후계 구조로서 게이트가 채널의 사방(상·하·좌·우)을 완전히 둘러싸는 GAA(Gate-All-Around) FET가 도입되고 있다. 삼성전자는 2022년 SF3(3nm) 공정에서 이를 MBCFET(Multi-Bridge Channel FET)라는 명칭으로 세계 최초로 양산에 적용하였으며, TSMC도 N2(2nm) 공정부터 나노시트(Nanosheet) 기반의 GAA 구조를 도입할 예정이다.

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기