MOSFET의 공핍형(Depletion)과 증가형(Enhancement) 타입에 대해서 설명해 보세요

MOSFET은 Depletion type(공핍형)과 Enhancement type(증가형)으로 구분할 수 있다. 공핍형은 평상시에 소스와 드레인 사이에 채널이 형성되어 있어, 전류가 흐르다가 게이트를 닫아주면 전류가 차단되는 형태로 동작하고 증가형은 반대로 평상시에 소스와 드레인 사이에 채널이 형성되지 않아 전류가 흐르지 못하다가 게이트를 열어주면 전류가 흐르게 되는 형태로 동작한다는 것이 다르다.

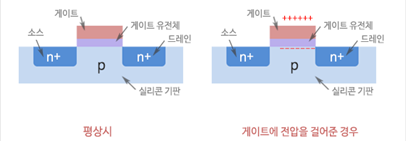

위의 그림에서 보듯, NMOS의 소스와 드레인은 N형 영역으로써 전자가 다수 캐리어이고, 두 영역의 사이에는 P형 영역으로써 정공이 다수 캐리어이다. 평상시에는 소스와 드레인 사이에 전자가 흘러갈 수 있는 채널이 형성되어 있지 않다. 게이트에 양의 전압을 걸어주는 경우에는 게이트와 실리콘 기판 사이에 유전체가 끼어있어서 전류는 흐를 수 없다. 하지만 전기장(전계)이 형성되어 게이트 밑부분에 있는 정공들이 척력을 받아 밀려나고 전자(P형 영역에서의 소수 캐리어)들이 인력을 받아 몰려들어 N형 채널이 형성되는 경우, 이 N형 채널은 전자가 달려갈 수 있는 도로와 같다. 이렇게 형성된 N형 채널을 반전층이라고 한다. P형 영역의 다수 캐리어는 정공이었는데, 게이트에 걸어준 양의 전압 때문에 다수 캐리어인 정공이 물러나고 소수 캐리어인 전자가 몰려들어 캐리어 영역이 P형으로부터 N형으로 반전되었기 때문에 반전층이라고 부르는 것이다.

반대로 게이트에 음의 전압을 거는 경우, 인력에 의해 정공들이 끌려와 처음보다 더 많은 정공이 게이트 밑에 모이게 된다. 이는 전자가 달릴 수 있는 통로가 더 굳세게 닫힌 것과 같아 전류가 흐르지 못하게 된다. 증가형 NMOS의 경우 소스에서 드레인으로 전자가 흐를 수 있도록 통로를 만들기 위해 게이트에 양의 전압을 걸어주었는데, 통로가 간신히 만들어져서 전류가 흐르기 시작하는 전압을 문턱전압(threshold voltage)이라고 부른다. 결과적으로 MOSFET은 문턱전압 이상의 전압을 게이트에 걸어줘야만 전류가 흐르는 것이다.

이상적으로 생각했을 때 Vgs < Vth(Vth : Threshold Voltage) 인 상황이라면 차단 영역이기 때문에 완벽한 채널이 형성되지 못하여 Drain과 Source사이에 전류가 흐르지 못할 것이다. 하지만 실제로는 그렇지 않다. 즉, Gate - Source의 전압인 Vgs가 문턱전압인 Vth보다 작더라도 Drain과 Source 사이에 전류가 미약하게 흐를 수 있다.

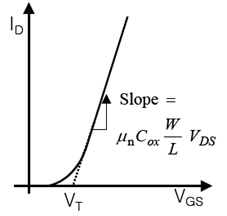

<MOSFET에서의 실제 Vgs와 Id 와의 그래프>

즉, 위와 같이 Vgs가 Vt가 되기 이전에 이미 Id(드레인 전류)는 증가하고 있다. 이렇게 문턱전압에 도달하기 전에 흐르는 전류를 문턱 이하 누설전류(Sub Threshold Current)이라고 한다. 이는 실제 전자들의 에너지 분포에서 몇 개는 볼츠만 분포에 의해 상대적으로 높은 에너지를 가지고 있고 이런 전자들이 완벽하지 않은 채널 사이에 흘러들어가서 Sub Threshold Current를 만들어 내는 것이죠. 따라서 아래와 같은 식이 문턱 이하 누설전류의 식이 됩니다.

위의 식을 봐도 볼츠만 상수와 절대온도가 관련된 것을 볼 수 있다. 또한 Vgs를 통해 문턱누설전류는 게이트의 문턱전압과 관련된 것을 알 수 있다.

이 문턱 이하 누설전류가 이슈가 되는 이유는 MOSFET은 높은 입력 임피던스를 가지고 있어 저전력 설계에 이용되는 것에 문제가 있기 때문이다. 저전력 설계를 위한 반도체를 구동하기 위해서는 일단 게이트 전압의 문턱전압이 작아져야 한다. 즉, 기존에는 5V의 문턱전압이 3.3V로 낮아지고 요즘에는 다시 1.8V정도로 낮아지면서 저전력 설계를 구현하게 된다는 것이다. 이렇게 문턱전압이 낮아지면서, 이전에 충분히 높은 게이트 전압에서는 누설전류가 큰 문제가 안 되었지만 현재는 누설되는 전류의 양도 전체 소모 전력의 중요한 부분이 되었다. 예를 들면 5V 구동일 때 3V만 되어도 누설전류가 생기고 이는 전체전력에서 큰 부분이 아니겠지만 1.8V 구동에 0.7V에 누설전류가 있다면 전체적으로 큰 전력소모가 된다는 것이다. 따라서 요즘 이 누설 전류를 줄이기 위해서 많은 연구가 되고 있다.

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기