누설 전류에 대해서 설명해 보세요.

마이크로프로세서를 보다 고속으로 동작하기 위해서는 트랜지스터를 보다 작게 만들면 된다. 트랜지스터가 작아지면 집적도가 높아져 다이 사이즈도 작아지고, 한 장의 웨이퍼로부터 많은 칩을 얻을 수 있게 되므로 비용도 낮아지게 된다. 그러나 트랜지스터의 크기를 줄이는 데는 몇 가지 문제가 있다. 우선 누설 전류(current flow)가 존재한다는 것이다. 누설 전류란 전류가 흘러야 할 곳이 아닌 다른 곳으로 흘러버리는 현상이다. 즉 전류가 새는 것인데 이는 트랜지스터 본래의 동작에 기여하지 못한 채 소비전류만을 늘리게 된다.

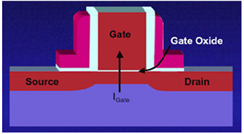

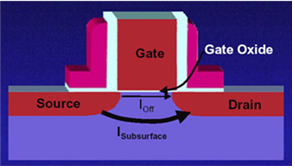

누설 전류가 흐르게 되는 경우는 크게 두 가지가 있을 수 있다. 크기가 작아지면서 산화막의 두께 또한 얇아지게 된다. 그로 인해 게이트(Gate)와 아래 기판(subsurface) 간에 전류가 누설되는 것이다. 그리고 소형화가 되면서 소스(source)와 드레인(drain) 사이에 있는 절연층도 얇아질 수밖에 없다. 그로 인해 소스와 드레인 간에 누설 전류도 흐르게 되는 것이다.

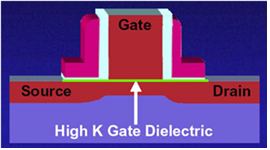

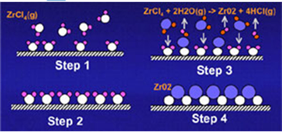

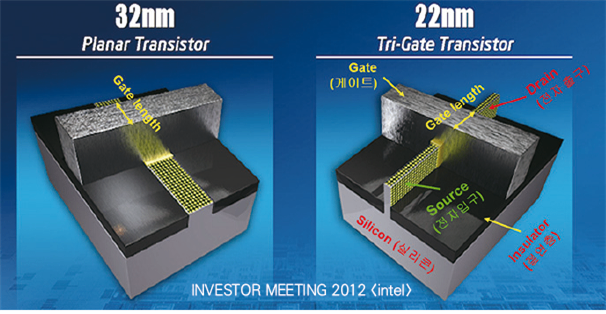

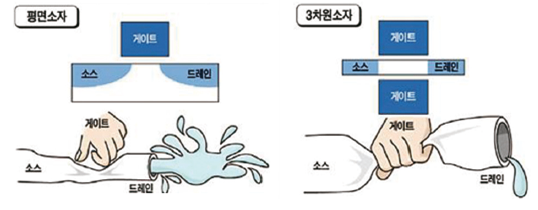

게이트의 누설전류를 줄이기 위해서 반도체 제조회사들은 크게 두 가지의 시도를 하고 있다. 첫 번째는 게이트의 절연재료에 보다 높은 유전율의 물질을 사용하는 것이다. 유전율은 k로 나타내기 때문에, 이 기술을 'High-k'라고 부르기도 한다. 또다른 시도는 평면이 아닌 입체를 활용하는 방법으로 Fin-FET이라고 불리는 기술이다.

[최신 누설 전류 해결 기술]

High-k 물질로는 HfO₂(이산화하프늄)이 현재 첨단 공정의 표준 게이트 절연막으로 자리잡았으며, 여기에 TiN·TaN 등 금속 게이트를 조합한 High-k/Metal Gate(HKMG) 구조가 인텔 45nm(2007년) 이후 모든 첨단 CMOS 공정에 적용되고 있다. 최근에는 FinFET에서 한 단계 더 나아간 GAA(Gate-All-Around) FET가 도입되어 채널 전면에 대한 게이트 제어력을 극대화함으로써 서브스레숄드 누설 전류를 더욱 효과적으로 억제하고 있다. DRAM에서는 채널을 기판 내부에 매립하는 BCAT(Buried Channel Array Transistor) 구조가 적용되어 GIDL(Gate Induced Drain Leakage) 전류를 줄이고 리프레시 특성을 개선하고 있다.

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기