10nm 이하 공정에서 발생할 수 있는 아날로그 회로설계의 어려움에 대해 설명해 보세요.

반도체 공정기술은 발전을 거듭하고 있어, 현재 CMOS 반도체의 경우 14nm공정이 양산 제품의 생산에 사용되고 있으며, 향후에는 10nm 이하의 공정기술도 양산 수준으로 확보될 것으로 예상된다. 이와 같은 반도체 공정 기술의 발전으로 인해 한 개의 반도체 칩 위에 하나의 시스템을 집약하는 System-on-chip이 가능하게 되었다.

SoC의 대부분은 디지털 로직으로 구성되어 있다. 하지만 인간이 인지하는 모든 정보는 디지털 정보가 아니라 아날로그 정보이기 때문에, 디지털 로직과 인간이 인지하는 정보를 이어주기 위해서는 아날로그 회로가 필수적으로 요구된다. 반도체 공정 기술이 발전할수록 동일한 디지털 로직을 구현하는데 필요한 비용 (실리콘 면적, 전력 소모)은 점점 감소한다. 하지만, 반도체 공정 기술이 발전하여 CMOS 트랜지스터의 크기가 줄어들수록 아날로그 회로는 동일한 성능을 얻기 위해 지불해야 하는 비용이 거의 동일하게 유지된다. 결국 SoC의 구현 비용 중에서 아날로그 회로를 구현하는데 드는 상대적 비용이 증가하게 되는 것이다. 다르게 말하면, 반도체 공정 기술이 발전함에 따라 역설적으로 아날로그 회로의 설계는 그 난이도가 증가하게 된다.

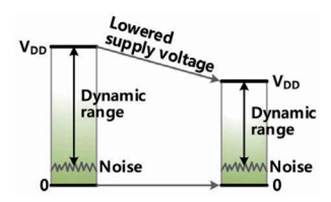

아날로그 회로에서 정보를 표현하는 수단은 통상적으로 전압이다. 이러한 상황에서 공급 전압이 낮아진다는 것은 아날로그 신호가 가질 수 있는 범위가 줄어든다는 것을 의미한다. 즉, 위의 그림에서 보인 바와 같이 신호의 동적 범위 (dynamic range)가 감소하게 된다. 만일 공급 전압이 줄어든 상황에서도 신호의 동적 범위를 동일하게 유지하기 위해서는 잡음의 크기를 줄이는 수밖에 없다. 하지만 잡음의 크기를 줄이기 위해 트랜지스터의 트랜스 콘덕턴스(gm)을 키우게 되면 전력 소모가 증가하게 되고, 트랜지스터의 게이트 면적을 늘리는 경우 게이트의 면적을 늘려야 하는데, 이는 각각 아래와 같은 문제를 야기한다.

먼저 CMOS 트랜지스터의 게이트 길이가 줄어들수록 아날로그 회로의 성능을 결정하는 가장 중요한 요소인 Intrinsic gain이 감소한다. 또한 공급 전압이 줄어듦에 따라 트랜지스터를 수직으로 쌓아 전압 이득을 높이는 캐스코드 등의 설계기법을 사용할 수 없게 된다. 즉, 아날로그 회로의 가장 기본적인 구성 요소인 전압 증폭기의 설계가 매우 어려워지는 것이다. 이와 같은 상황을 극복하기 위한 설계 기법으로서 구체적으로 아래와 같은 기법들이 시도되고 있다.

① 트랜지스터의 바디 단자 이용

통상적으로 CMOS 트랜지스터를 이용해서 회로를 설계할 때는 게이트, 소스, 드레인의 세 개의 단자를 활용하고 바디 단자는 일정한 전압으로 유지하거나 해당 트랜지스터의 소스 단자에 연결한다. 하지만 공급 전압이 낮은 경우 전압 헤드룸 문제를 해결하기 위해 바디 단자에 신호를 인가하여 회로를 구현하는 방법을 사용할 수 있다.

② 비교기를 이용한 연산 증폭기 회로 대체

적분회로는 아날로그 신호를 처리하는 아날로그 회로에서 가장 중요한 구성요소 중 하나이다. 통상적으로 적분기는 연산 증폭기를 활용하여 구현하는데, CMOS 반도체 공정이 발전함에 따라 증폭기의 설계가 점점 더 어려워지기 때문에 고성능의 연산 증폭기 구현 역시 매우 어려운 작업이 된다. 이를 해결하기 위해 비교기(Comparator)를 이용하여 적분회로를 구현하는 방법이 제안되고 있다. 비교기는 연산 증폭기에 비해 설계가 훨씬 간단하고 공급 전압이 낮은 경우에도 좋은 성능을 얻을 수 있다.

③ 시간 정보를 이용한 아날로그 신호 표현

소자의 크기가 작아지고 공급 전압이 감소하면서 발생하는 어려움은 정보를 표현하는 수단으로 전압을 사용하기 때문이다. 따라서 정보를 표현하는 수단으로 전답이 아니라, 전류를 사용하여 낮은 공급 전압에서도 신호의 동적 범위를 확보할 수 있을 것이다. 보다 구체적으로는 기존의 연산 증폭기를 이용한 적분회로를 전압 조절 발진기로 대체함으로써, 연산 증폭기를 사용하지 않고 회로를 구현하는 것이다.

④ 확률적 아날로그 신호 처리

아날로그 회로의 성능을 제한하는 확률적 변이는 그 값을 예상할 수 없기 때문에, 설계 단계에서 그 값을 최소화할 수 있게 하거나 실제 동작 단계에서 그러한 변이를 보상할 수 있도록 하는 것이 기존의 방식이었으나, 다수의 비교기를 활용하여 비교기의 입력 오프셋이 가우시안 분포를 갖게 하도록 하고, 모든 비교기의 출력을 더한 값을 아날로그-디지털 변환기의 디지털 출력으로 삼는 방법이다. 다만 이러한 확률적 신호처리를 이용하기 위해서는 통상적인 아날로그-디지털 변환기에 비해 훨씬 더 많은 수의 비교기가 필요한 문제가 있다.

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기