3D NAND 반도체 기술에 대해서 설명해 주세요.

최근 반도체 시장에서 3차원 설계가 중요하게 다루어지는 점은 2차원 설계에서 더 미세한 공정을 수행하는 데에 한계가 왔다는 점이 가장 크다. 공정이 미세화된다는 것은 셀이 작아지고 간격이 좁아진다는 것을 뜻하는데, 이렇다 보니 전자가 누설되는 간섭현상이 심화되면서 한계가 나타나는 것이다. 또 20nm부터는 쿼드러플패터닝을 해야 해서 NAND의 중요한 요소 중 하나인 가격 면에서 높이 쌓는 것이 유리하다는 것이 현재 메모리 업체들의 판단이다.

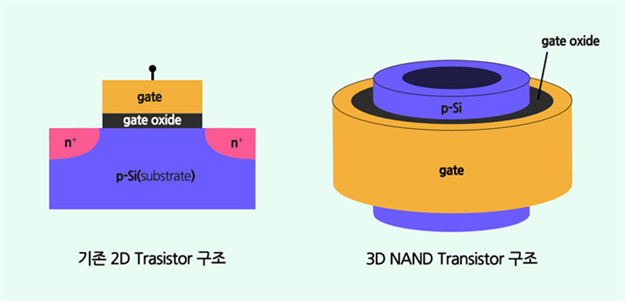

3D NAND와 2D NAND의 구조적 측면에서의 차이점을 보면, 기존 2D NAND는 평면으로 배열했지만 3D NAND는 원기둥 모양의 트랜지스터를 수직으로 쌓아올리고 쌓인 기둥들을 평면으로도 배열한다. 공정적인 측면에서는 기존 2D NAND는 실리콘 기판에 gate oxide를 증착한 후 그 위에 gate 물질을 얹고 패터닝을 해서 MOS Transistor로 동작하게 하는 방식이었으나, 3D NAND는 그 순서가 반대가 된다. Gate에 구멍을 뚫어서 그 안에 gate oxide를 만들고, 그다음에 기판 역할을 하는 p-Si(poly silicon)을 증착하는 방식을 사용한다.

이와 같은 복잡한 공정을 활용하는 이유는 고집적 제품을 만들 수 있기 때문이다. 2D NAND는 128Gb가 한계점이었으나 3D NAND를 이용하면 256Gb, 512Gb까지 만들 수 있다. 이는 고용량 제품을 싼 값에 만들 수 있다는 점에서 좋은 결과이다. 또한 품질적인 면에서도 2D NAND는 셀이 워낙 작다 보니 작은 만큼 품질 관리가 어려려운데, 3D 같은 경우 비교적 큰 셀들을 쌓아 올리기 때문에 품질이 좋다는 점에서 장점이 있다. 초기에는 24단~48단 수준으로 개발이 이루어졌으며, 이후 100단 이상을 넘어 현재는 200단 이상의 고적층 기술이 적용되고 있다.

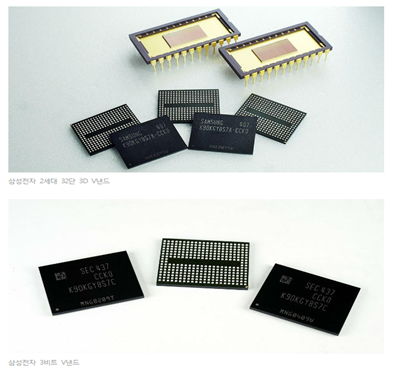

3D NAND 시장을 선점한 삼성전자는 2014년 5월 2세대 32단 3D VNAND를 양산하기 시작했다. 2세대는 1세대 VNAND보다 30% 이상 적층 수를 높였고, 기존 평면구조 MLC 대비 신뢰도 수명을 2배 늘리면서도 전력 소비량은 20% 절감시켰다. 삼성전자는 2세대를 공개한지 1년도 안된 2014년 10월, 3비트 3D VNAND 양산에 성공했다. 삼성의 3비트 VNAND는 2세대(32단) 공정은 그대로 유지하면서 셀 하나에 저장되는 데이터 수를 기존 2개에서 3개로 늘려 셀 저장 용량을 1.5배 확대함으로써 10나노급 128 Gb를 구현해 냈다. 3비트 VNAND는 기존 10나노급 평면구조 NAND 제품보다 생산성이 2배 이상 향상되면서 서버용 SSD에서 보급형 PC SSD까지 제품군을 대폭 확대해 나가고 있다.

3D NAND 기술 개발에 탄력을 받은 삼성전자는 2015년 8월 256 Gb 속도를 구현하는 3세대 48단 VNAND 양산을 시작했다. 3세대 VNAND는 셀이 형성될 단층을 48단으로 쌓고 나서 약 18억개의 원형 홀을 수직으로 뚫은 다음, 총 853억 개 이상의 셀을 고속 동작시킴으로써 각 셀마다 3개의 데이터(3비트)를 저장할 수 있도록 성능이 향상됐다. 따라서 총 2560억 개의 데이터를 읽고 쓸 수 있게 된 것이다. 특히 ‘3차원 원통형 CTF(3D Charge Trap Flash) 셀 구조’와 ‘48단 수직 적층 공정’, ‘3비트 저장기술’을 적용해 2세대 VNAND보다 데이터를 더욱 빠르게 저장하고, 소비 전력량을 30% 이상 줄였다. 또 기존 32단 양산 설비를 최대한 활용함으로써 제품 생산성을 약 40%나 높여 원가 경쟁력도 대폭 강화했다. 초기에는 삼성전자가 선도적으로 양산을 진행하였으나, 이후 SK hynix, Micron Technology, Kioxia 등 주요 업체들도 3D NAND 양산에 참여하고 있다.

[최신 기술 현황]

3D NAND의 적층 단수는 해마다 빠르게 증가하고 있다. 2024년 기준으로 삼성전자는 300단 이상의 V-NAND 양산을 추진 중이며, COP(Cell Over Peri) 구조를 채택하여 페리페럴 회로를 셀 하단에 배치함으로써 면적 효율을 극대화하고 있다. SK하이닉스는 321단 4D NAND를 발표하였고, Micron은 232단 NAND를 이미 양산하고 있다. 적층 단수가 높아질수록 동일 면적에 더 많은 용량을 집적할 수 있으나, HAR 식각 정밀도 확보와 층간 정렬(Overlay) 제어가 기술 경쟁력의 핵심 과제가 되고 있다.

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기