FinFET(Finfield effect transistor)기술과 Ultra-thin body SOI(Sillicon-on-indulator) 기술에 대해 설명해 주세요.

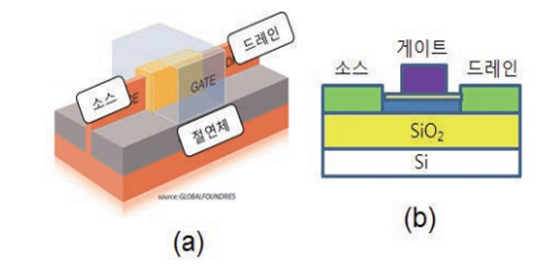

최근의 트랜지스터의 최소 선폭은 20nm로 마이크로프로세서, 시스템 반도체, 메모리소자까지 다양하게 적용된다. 이후 20nm 선폭을 넘어선 기술로써 제안되는 것은 FinFET(Finfield effect transistor)기술과 Ultra-thin body SOI(Silicon-On-Insulator) 기술로 대표된다. FinFET 기술은 아래 그림과 같이 평면형 2D 트랜지스터에서 변형된 형태로 소스와 드레인이 3면의 게이트에 의하여 감싸여 있는 3차원 구조를 가지고 있다. 이러한 경우에 Gate의 Si body에 대한 electric field 조절 능력이 획기적으로 증가하는 이점이 있다.

이러한 3차원 다중 게이트 FinFET은 선폭이 짧아짐에 따라 따라 발생하는 트랜지스터의 누설전류를 50%이상 감소시킬 수 있다. FinFET의 구조에서 트랜지스터 게이트는 상부와 좌우측에 설계되어 있는 서라운드(Surround) 게이트는 on과 off 상태에서 채널에 흐르는 전류를 완벽하게 제어할 수 있다. 특히 이것은 모바일 기기와 같이 휴대용 장치는 제한된 전지를 사용하는 경우 매우 중요한 동작특성이 된다. 즉 낮은 채널 전류 조절은 낮은 전력소비를 의미하는 것이며 이것은 전지를 좀 더 오래 사용할 수 있다는 말과 같다.

그러나 CMOS 소자의 채널거리를 최소화 시키는 방법은 실리콘 원자의 크기에 대한 제한 때문에 영원히 지속될 수 없다. 실리콘 기반 20nm 채널길이를 가지는 트랜지스터에 포함되는 실리콘 원자는 200개 정도에 지나지 않는다. 현재의 반도체 물리학에서 실리콘 재료는 연속적인 물질로 가정함으로 전자와 정공의 통계적인 거동이나 옴의 법칙이 모두 적용 가능하다. 그러나 20nm의 채널길이를 넘어 원자단위의 물리적 해석 방법으로 양자역학은 전혀 다른 형태를 가질 것이다. 결국 bulk 상태의 실리콘 상태에 대한 해석이 달라지므로 소자생산기술이나 안정적인 소자 동작의 방법은 완전히 변화해야 할 것이다.

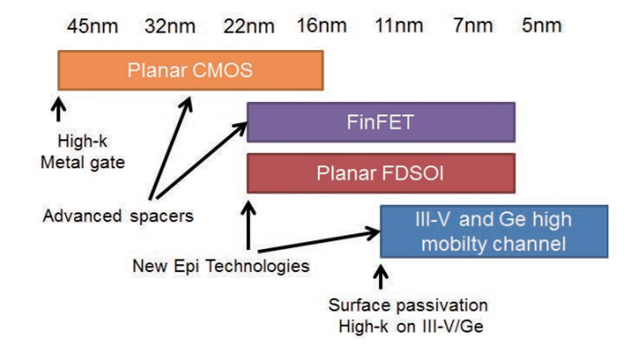

결국 높은 주파수와 낮은 동작전압에서 높은 전자이동도를 가지는 소자를 만들기 위해서 실리콘과는 구별된 SiGe, III-V 화합물 반도체 (GaAs, GaN, InP), IIVI 화합물 반도체, 탄소기반 나노물질(graphene, graphene oxide)과 같은 대안 반도체물질들이 적극적으로 연구 개발될 것으로 예상된다. 아래 그림은 45nm공정에서 5nm공정으로 게이트의 폭이 협소해짐에 따라서 적용가능한 반도체 CMOS의 구조의 변화를 보여 주고 있으며 단계적으로 극복하고 적용해야 할 기술을 제시하고 있다.

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기