ALD(Atomic Layer Deposition: 원자층 증착기술)에 대해서 설명해 보세요.

DRAM의 커패시터는 물을 담는 종이컵과 비슷하다고 이해하면 된다. 종이컵의 두께가 얇으면 물이 스며들거나 샌다. 지나치게 새면 컵으로서의 역할을 못한다. 커패시터는 전하를 담는 그릇으로 전하가 차 있는지, 비어 있는지를 통해 '1'과 '0'을 구분한다. 회로공정이 미세해지다보니 이 전하를 담는 그릇이 너무 작아지고 입구가 좁아져 제대로 작동하지 못하는 문제가 발생했다.

이는 커패시터의 유전막을 형성하는 증착과정에서 원자층이 과도하게 붙는 문제로 인한 것으로 이를 해결한 것이 ALD(Atomic Layer Deposition: 원자층 증착기술)이다. 커패시터를 만들 땐 안에 담기는 전하가 너무 빠르게 새지 않도록, 그리고 바로 옆 캐패시터 전하의 영향을 받지 않도록 얇고 단단한 유전막을 씌워야 한다. 초균일 유전막 형성 기술의 핵심은 바로 이 유전막을 균일하게 유지하는 데 있다. 최근 삼성전자는 독자적으로 개발한 물질을 캐패시터 안팎에 코팅, 유전막 두께를 옹스트롬 단위로 균일하게 만드는 데 성공했다.

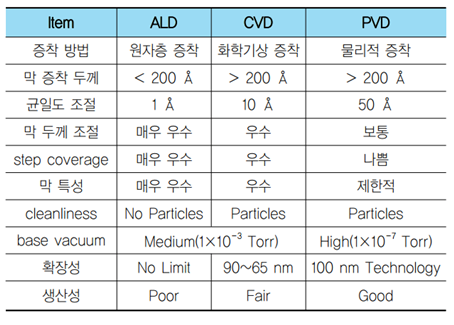

ALD법은 CVD법에 비해 생산성이 낮은 단점이 있지만, 낮은 온도에서 우수한 단차 피복성과 균일한 조성을 가지는 박막을 형성시킬 수 있고, 박막 내의 불순물 농도를 감소시킬 수 있다. 시간 당 막 성장 속도가 느리다는 것이 ALD 기술을 실리콘 반도체 공정에 적용하기 어려운 이유였지만 반도체 소자의 미세화에 따라 얇고 두께를 정밀하게 제어해야 할 메모리용 유전막, 확산 방지막, 게이트 유전막 등의 수요가 많아지기 때문에 ALD 기술은 핵심적인 반도체 제조 기술 중의 하나가 되고 있다.

[최신 응용 분야]

High-k 게이트 절연막: HfO₂, ZrO₂ 등 고유전율 물질의 ALD 증착은 현재 5nm 이하 모든 첨단 CMOS 공정의 표준으로 자리잡았다. ALD를 통해 등가 산화막 두께(EOT) 0.7nm 이하를 달성하고 있다.

3D NAND ONO 적층: 수백 층의 산화막·질화막을 교대로 증착하는 3D NAND 공정에서 층간 두께 균일성을 확보하기 위해 ALD가 필수적으로 활용된다.

GAA FET 게이트 절연막: 채널 나노시트의 상·하·좌·우 사방을 HfO₂ 게이트 절연막으로 균일하게 코팅하는 것은 CVD로는 불가능하며, ALD만이 유일한 해결책이다. 삼성전자 SF3(3nm GAA) 공정에서도 ALD가 핵심 공정으로 적용되고 있다.

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기