메모리 소자 기타

기출문제 풀이

기출문제 ❶

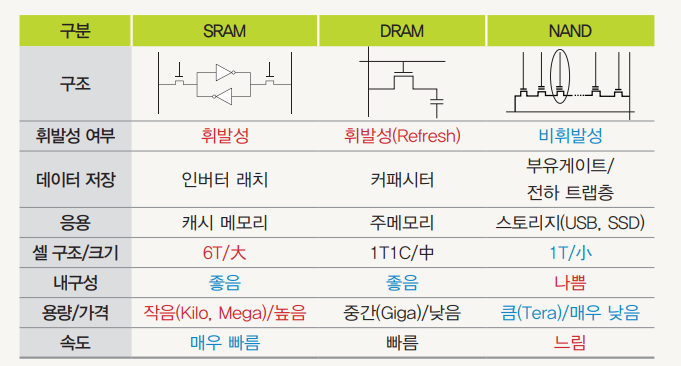

DRAM, SRAM, 낸드 플래시 메모리를 비교 설명하시오.

STEP1 접근 전략

설명형, 비교형의 복합형 문제로 난이도는 중하 수준이며 출제 빈도가 높다. •가장 기본적인 세 가지 메모리 소자의 구조, 원리, 특징 중 중요 핵심만을 비교 설명한다. •(판서 가능 시) 구조는 단면도나 도식(회로도)을 간략히 그려 설명한다.

STEP2 답안 구조화 TIP

Q DRAM, SRAM, 낸드 플래시 메모리 비교?

STEP3 모범답안

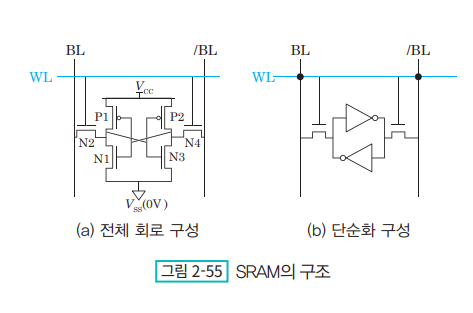

SRAM(Static Random Access Memory)은 단위 셀이 데이터 저장소인 두 개의 CMOS 인버터의 입력과 출력이 서로 맞물린 래치(Latch) 회로와 워드라인(WL)의 신호에 따라 이 래치 회로와 비트라인(BL)의 연결을 제어하는 두 개의 nMOS를 포함해 모두 6개의 트랜지스터(Tr)로 구성된 메모리 소자로, 서로 반대 데이터가 저장된 래치 회로 양단의 전압 차이로 ‘1’과 ‘0’을 기록하고 읽는 원리입니다. 데이터의 임의 접근(Random access)이 가능하고, 전하 저장 방식이 아닌 래치 회로의 상태에 따라 데이터가 결정되는 원리이므로 컴퓨터의 캐시 메모리로 사용될 만큼 빠릅니다. 하지만 전원이 끊기면 데이터가 사라지는 휘발성 소자이며 소비 전력이 상대적으로 높고 6개의 트랜지스터로 구성된 만큼 셀 크기가 커 대용량화가 어려우므로 가격이 비싸다는 단점이 있습니다. 데이터의 보존을 위해 아무런 동작을 하지 않아도 되는 특성 때문에 정적(Static)이라 표현합니다.

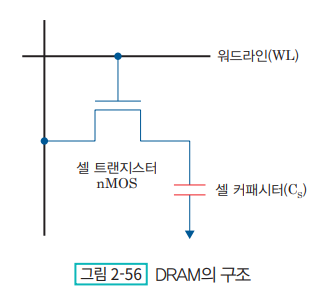

이에 반해 DRAM(Dynamic Random Access Memory)은 데이터가 저장되는 커패시터(Cap)와 이 Cap과의 연결 여부를 제어하는 스위치 역할을 하는 한 개의 nMOS(Cell Tr)로 구성되며, Cap의 전하 유무에 따라 ‘1’과 ‘0’ 데이터가 비트(Bit) 단위로 저장되는 원리입니다. 쓰기(Writing) 동작은 Cell Tr을 On시켜 BL을 통해 Cap에 전하를 충전 또는 방전시킴으로써 데이터를 저장하고, 읽기 동작 역시 Cell Tr이 On된 상태에서 Cap에서 BL로의 전하의 충전 또는 방전에 의해 BL의 전위가 바뀌는 것을 감지 증폭기(Sense amplifier)가 읽어내는 원리입니다. 단위 셀 크기가 SRAM에 비해 훨씬 작고 임의 접근이 가능하며 SRAM에 비해서는 느리지만 속도도 빨라, 컴퓨터의 주메모리로 사용됩니다. 그러나 휘발성인 데다, 커패시터에 저장된 데이터가 시간에 따라 소멸되어 주기적으로 데이터를 다시 써 주는 리프레시(Refresh) 동작을 해주어야 하는 단점이 있어 SRAM과는 달리 동적(Dynamic)이라고 합니다.

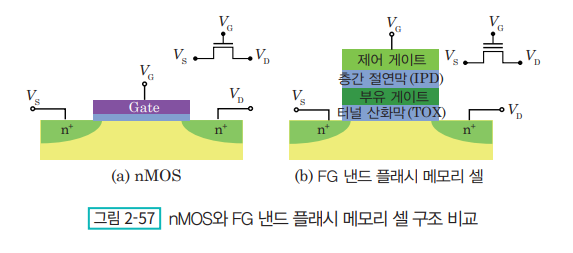

낸드 플래시 메모리는 일반 nMOS Tr에 터널 산화막(TOX)과 전하가 저장되는 부유 게이트(FG)나 전하 포획층(Charge trap layer)을 추가한 1Tr 구조로, 셀의 크기가 가장 작고 MLC(Multi-Layer Cell), TLC(Triple-Layer Cell) 등의 기능으로 저가의 대용량 메모리의 구현이 가능하여 USB 혹은 SSD와 같은 대용량 스토리지 메모리로 사용됩니다. 전원이 공급되지 않아도 데이터를 잃지 않는 비휘발성이라는 장점이 있지만 속도가 느리고 임의 접근이 안 되며, 절연막을 통해 전자를 주입하고 소거하는 동작으로 내구성이 떨어진다는 단점이 있습니다.

꼬리 질문 1 DRAM의Refresh효율을 개선하는 방법에 대해 설명하시오. |

Refresh 동작은 DRAM의 성능 및 전력 손실에 악영향을 미칩니다. 즉, Refresh 동작 중에 있는 메모리 부분에 대한 정상적인 읽기 및 쓰기가 불가능하고, Refresh 동작에는 데이터의 읽기 및 복원과 같은 작업이 포함되기 때문에 많은 전력을 소비합니다. Refresh 효율을 개선하는 공정 및 소자적인 방법은 Cell Cap을 증가시키고 누설 전류를 감소시켜 데이터 보유시간(Retention time)을 증가시키거나, DRAM의 집적도 증가로 인한 WL 및 BL당 Cell 수 증가에 따른 WL 및 BL 기생 저항 및 정전 용량을 감소시켜 * |

핵심 이론 정리

1. 메모리 소자 계층도(Hierarchy)

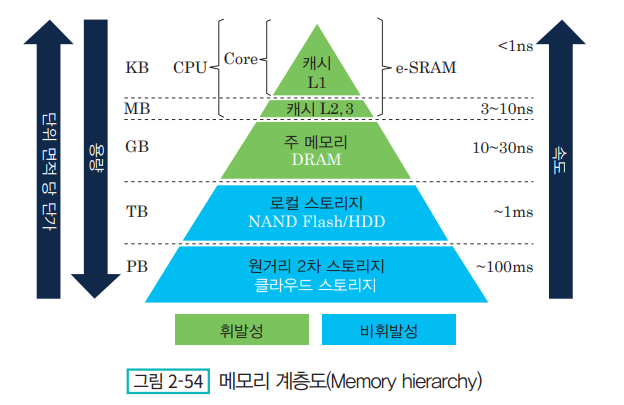

전통적인 폰 노이만(Von Neumann) 구조의 컴퓨터 시스템에 사용되는 메모리 계층도(Hierarchy)는 [그림 2-54]와 같다.

그 다음은 DRAM보다 많이 느리지만 단위 실리콘 면적당 메모리 용량을 매우 크게 하여 제품 단가를 낮춘 낸드 플래시 메모리이다. 주로 SSD(Solid State Driver)나 외장 USB(Universal Serial Bus) 메모리 형태로 사용되며, 단가의 하락에 힘입어 기존의 하드 디스크 드라이버(Hard Disk Driver, HDD)를 빠르게 대체 중에 있다.

마지막으로 클라우드 스토리지는 클라우드 컴퓨팅(Cloud computing)의 한 갈래로서, 인터넷 관련 업체에 의해 제공되는 저장 공간에 본인의 정보를 저장해 두고, 이것이 필요할 때마다 가지고 있는 각종 단말기를 통해 정보를 불러올 수 있다. 속도가 느리고 보안상 문제 및 인터넷이 연결된 곳에서만 접근이 가능하다는 등의 단점이 있다.

전체적으로 계층도에서 아래로 갈수록 동작 속도는 느려지지만, 메모리 용량은 증가하고 이에 따라 가격은 내려가는 양상이다. 또한 SRAM과 DRAM은 전원이 인가되지 않으면 데이터가 사라지는 휘발성(Volatile) 메모리인 데 반해 나머지 메모리는 데이터가 사라지지 않는 비휘발성(Non-Volatile) 메모리이다.

2. SRAM(Static Random Access Memory)

SRAM은 Static Random Access Memory의 약자로서, 워드라인(Word line, WL)과 비트라인(Bit line, BL)이 선택되면 임의로(Random access) 읽고 쓰는 것이 가능하다. SRAM의 단위 기억 소자(Cell)는 [그림 2-55]와 같이 데이터 저장소인 두 개의 CMOS 인버터의 입력과 출력이 서로 맞물린 래치(Latch) 회로와, WL의 신호에 따라 이 래치 회로와 BL의 연결을 제어하는 두 개의 nMOS를 포함해 모두 6개의 트랜지스터(Tr)로 구성된 메모리 소자이다. 서로 반대 데이터가 저장된 래치 회로의 양단 전압 차이로 ‘1’과 ‘0’을 기록하고 읽는 원리이다. 데이터의 임의 접근(Random access)이 가능하고, 전하 저장 방식이 아닌 래치 회로의 상태에 따라 데이터가 결정되는 원리이므로 컴퓨터의 캐시 메모리로 사용될 만큼 빠르다는 장점은 있다. 반면 전원이 끊기면 데이터가 사라지는 휘발성 소자이며 소비 전력이 상대적으로 높고 6개의 트랜지스터로 구성된 만큼 셀 크기가 커 대용량화가 어렵고 가격이 비싸다는 단점이 있다. 데이터의 보존을 위해 아무런 동작을 하지 않아도 되는 특성 때문에 정적(Static)이라 한다. 따라서 SRAM은 빠른 속도의 CPU와 연동되는 캐시 메모리로 주로 사용된다.

3. DRAM(Dynamic RAM)

DRAM은 Dynamic Random Access Memory의 약자로서, 단위 기억 소자는 [그림 2-56]과 같이 1개의 nMOS 트랜지스터와 1개의 커패시터를 가진 단순한 구성의 메모리이다. 때문에 SRAM 대비 높은 집적도를 가지며 동일 비용으로 대용량 메모리를 제작하는 데 유리하다. 하지만 기억 소자로 사용되는 커패시터의 특성상 전원이 공급되고 있는 동안에, 일정한 주기로 다시 기록(Refresh)해 주지 않으면 데이터가 자연히 사라지는 특징을 가지고 있다. 플래시 메모리에 비해 속도가 매우 빠르고 SRAM에 비해 대용량에 유리하다. 따라서 PC의 메인 메모리에 주로 사용된다. DRAM은 전하의 충방전을 통해 커패시터에 논리값을 저장한다. 메모리 어레이 상의 각 셀은 행 주소와 열 주소를 가지고 있어 행 주소와 열 주소가 선택되면 SRAM과 같이 셀에 임의 접근(Random access)이 가능하다.

4. 낸드 플래시(NAND Flash) 메모리

기본적인 낸드 플래시(NAND Flash) 메모리의 단위 셀은 [그림 2-57]과 같이 nMOS 구조에 부유 게이트(Floating Gate, FG)가 추가된 구조로, 이 FG에 전자를 주입하거나 제거함으로써 데이터를 저장하는 원리이다. FG에 전자가 있으면 프로그램(Program) 상태로 ‘0’으로 인식하고 FG에 전자가 없으면 소거 상태(Erase)로 ‘1’로 인식한다. 쓰기 동작은 CG에 강력한 양전압을 인가하면 p형 기판으로부터 음전하를 띤 전자가 터널 산화막(Tunnel Oxide, TOX)을 통과하여 FG에 주입되고 이렇게 절연체로 둘러싸인 FG에 갇힌 전자는 전원이 공급되지 않아도 외부로 유출되지 않아 데이터가 보존되므로 비휘발성 메모리인 것이다.

한편, 낸드 플래시에 데이터를 프로그래밍하기 위해서는 FG 내의 전자를 모두 제거해 주어야 한다. 저장될 데이터가 ‘0’인지 ‘1’인지 모르는 상황에서 FG에 전자가 남아 있으면 제대로 데이터를 기록할 수 없기 때문이다. 이러한 동작을 소거 동작이라 하고, 방법은 프로그램 동작의 반대이다. p형 기판에 고전압을 인가하여 p형 기판 쪽으로 전자를 끌어내리는 원리이다. 마지막으로 읽기 동작은 전자가 있는(프로그래밍된) 셀의 문턱 전압은 0V보다 크고, 전자가 없는(소거된) 셀의 문턱 전압은 0V보다 작아 중간 정도의 전압을 게이트에 인가하여 트랜지스터를 통한 전류의 유무를 기준으로 ‘0’과 ‘1’을 판독하게 된다. 낸드 플래시 셀은 하나의 트랜지스터 구조이므로 셀의 크기가 가장 작고, MLC(Multi-Layer Cell), TLC(Triple-Layer Cell) 등의 기능으로 저가의 대용량 메모리의 구현이 가능하여 USB 메모리 혹은 SSD와 같은 대용량 스토리지 메모리로 사용되고, 전원이 공급되지 않아도 데이터를 잃지 않는 비휘발성이라는 장점은 있다. 하지만 속도가 느리고 임의 접근이 안 되며, 절연막을 통해 전자를 주입하고 소거하는 동작이 진행되므로 내구성이 떨어진다는 단점이 있다.

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기