메모리

학습 포인트 |

본 단원에서는 반도체 집적회로를 구성하는 개별 부품의 구성 요소와 그 의미는 무엇이며, 각 구성 요소를 이루는 소자(Device)에는 어떤 것들이 있는지, 그리고 그 원리는 무엇인지 학습한다. 반도체를 구성하는 핵심 소자인 PN 접합 다이오드와 MOSFET에 대한 기초 지식을 바탕으로 대표적인 메모리 소자인 SRAM, DRAM 그리고 낸드 플래시의 동작 원리와 최신 기술에 대해 알아보도록 하자. |

개념 맵 |

1 메모리 소자 계층도(Memory hierarchy)

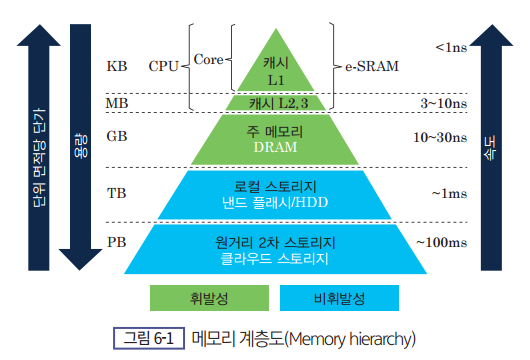

전통적인 폰 노이만(Von Neumann) 구조의 컴퓨터 시스템에 사용되는 메모리 계층도(Memory hierarchy)는 [그림 6-1]과 같다. 계층도의 최상위에는 캐시(Cache) 메모리가 위치해 있으며, 주로 중앙 처리 장치(Central Processing Unit, CPU)에 내장되어(Embedded) 빈번하게 사용하는 데이터를 저장하는 등 CPU와 긴밀하게 통신하는 메모리이다. 이는 메모리 중에서 가장 빠르지만 단위 면적당 단가가 가장 높은 SRAM으로 구성되어 있다.

캐시 메모리의 바로 아래층에는 컴퓨터의 주 메모리(Main memory) 역할을 하는 DRAM(Dynamic Random Access Memory)이 위치하고 있다. DRAM은 SRAM보다는 느리지만 단순한 구조로 이루어져 있어, 가격이 저렴하면서 대용량의 데이터를 저장할 수 있다는 장점이 있다. DRAM의 아래층으로 내려오면 낸드 플래시(NAND Flash) 메모리가 있다. 낸드 플래시 메모리는 DRAM보다 많이 느리지만, 단위 실리콘 면적당 메모리 용량을 크게 하여 제품 단가를 낮춘 메모리이다. 주로 SSD(Solid State Driver)나 외장 USB(Universal Serial Bus) 메모리 형태로 사용되며, 단가 하락에 힘입어 기존의 하드 디스크 드라이버(Hard Disk Driver, HDD)를 빠르게 대체하고 있는 중이다. 마지막으로 계층도의 최하위에는 클라우드 스토리지(Cloud storage)가 있다. 이는 클라우드 컴퓨팅(Cloud computing)의 한 갈래이며, 인터넷상으로 제공되는 저장 공간에 본인의 정보를 저장해 두고, 필요할 때마다 본인의 단말기를 통해 정보를 불러올 수 있는 기술이다. 매우 편리한 기능이지만 속도가 느리고, 보안상의 문제 및 인터넷이 연결된 곳에서만 접근이 가능하다는 등의 문제가 있다.

전체적으로 계층도를 정리해보면, 계층도의 아래로 갈수록 동작 속도는 느려지지만, 메모리 용량은 증가하고 이에 따라 가격은 내려가는 양상이다. SRAM과 DRAM은 전원이 인가되지 않으면 데이터가 사라지는 휘발성(Volatile) 메모리인 데 반해, 나머지 메모리는 데이터가 사라지지 않는 비휘발성(Nonvolatile)메모리이다. 이어지는 절에서는 이 중 SRAM, DRAM, 낸드 플래시 메모리에 대해 상세히 설명하고자 한다.

2 SRAM(Static Random Access Memory)

(1) CMOS 인버터 회로

CMOS 디지털 회로를 구성하는 가장 기본적인 논리 게이트이자, 논리값을 반전시키는 기능을 수행하는 CMOS 인버터의 구조와 동작 원리, DC 특성 등에 대해 알아보도록 하자.

①CMOS 인버터의 구조와 동작 원리

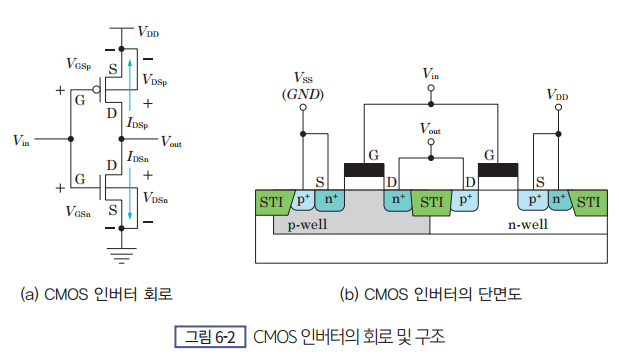

통상 CMOS 인버터는 [그림 6-2(a)]과 같이 증가형(Enhancement-type) pMOS가 부하(Load) 소자로, 증가형 nMOS가 구동(Driver) 소자로 구성된다. pMOS의 소스(Source)는 전원 VDD에 연결되고, nMOS의 소스는 접지 VSS에 연결되며, 입력 Vin은 nMOS와 pMOS의 게이트(Gate)에, 출력 Vout은 부하 소자와 구동 소자의 드레인 접점에서 얻어진다.

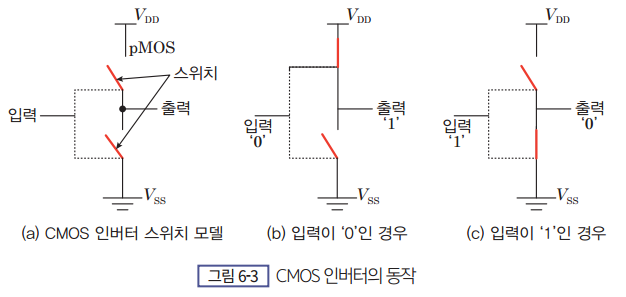

[그림 6-2(b)]는 n-well과 p-well로 구성된 Twin well CMOS 공정으로 제작된 CMOS 인버터의 단면도이다. pMOS의 기판(n-well)은 n+ 확산영역(n-well 컨택)을 통해 VDD에 연결되고, nMOS의 기판(p-well)은 p+ 확산영역(p-well 컨택)을 통해 VSS에 연결된다. n-well 컨택에 의해 n형 기판과 pMOS소스/드레인의 PN 접합에, p-well 컨택에 의해 p-well과 nMOS 소스/드레인의 PN 접합에 역방향 바이어스가 각각 인가되어 pMOS와 nMOS가 정상적으로 동작할 수 있게 된다. 개략적인 CMOS 인버터의 동작은 [그림 6-3]과 같다. [그림 6-3(b)]와 같이 입력 Vin이 논리값 ‘0’(0V)인 경우에 pMOS는 도통되고 nMOS는 차단 상태가 되어, 출력전압 Vout은 VDD가 되며, 부하 소자가 도통되어 출력에서 논리값 ‘1’이 얻어지므로 부하 소자인 pMOS를 풀업(Pull-up) 소자라 한다. 반대로, [그림 6-3(c)]와 같이 입력 Vin이 논리값 ‘1’(VDD)인 경우에, pMOS는 차단 상태가 되고 nMOS는 도통되어, 출력전압 Vout은 0V가 된다. 구동 소자가 도통되어 출력에 논리값 ‘0’이 얻어지므로 구동 소자인 nMOS를 풀다운(Pull-down)소자라고 한다.

②CMOS 인버터의 전달 특성과 잡음 여유

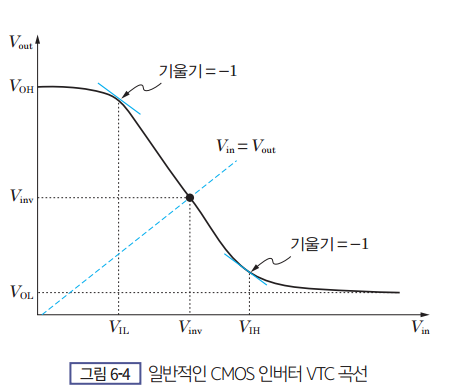

CMOS 인버터 회로에 인가되는 입력전압 Vin의 변화에 따른 출력전압 Vout의 변화를 전압 전달 특성(Volage Transfer Characteristic, VTC) 또는 DC 전달 특성이라고 한다. [그림 6-4]는 x축을 Vin으로, y축을 Vout으로 하는 일반적인 CMOS 인버터의 VTC 곡선이다. Vin이 0에 가까우면, Vout은 전원전압 V,에 가까운 값(논리 ‘1’)이 되며, 반대로 Vin이 VDD에 가까우면, Vout은 0V에 가까운 값(논리 ‘0’)이 되어 입력과 출력의 논리값이 서로 반대가 되는 관계를 보인다.

[그림 6-4]의 VTC 곡선의 y축에서는 인버터의 출력전압과 관련된 파라미터들이 정의되는데, 논리 ‘1’과 논리 ‘0’에 대한 출력전압 VOH와 VOL을 각각 정의할 수 있고, 이때 VOH와 VOL의 차이를 논리 스윙(Logic swing)이라고 한다. 통상 VOH가 전원 전압 VDD에 가까울수록, VOL이 0V(VSS)에 가까울수록 양호한 DC 특성을 보인다고 할 수 있다.

VTC 곡선의 x축에서는 인버터의 입력전압과 관련된 파라미터가 정의되는데, 논리 ‘0’으로 인식될 수 있는 최대 입력전압을 VIL이라 하고, 논리 ‘1’로 인식될 수 있는 최소 입력전압을 VIH라고 정의한다. VIH과 VIL은 VTC 곡선의 기울기가 -1인 점에서 각각 정의된다. 또한 VTC 곡선에서 Vin과 Vout이 동일해지는 점을 스위칭 문턱 전압(Switching threshold voltage, Vinv)으로 정의한다. 통상 디지털 회로의 전압은 VDD 및 VSS의 변동, 신호 간 간섭 등 다양한 원인들에 의해 이상적인 값과 차이가 날 수 있는데, 이러한 전압 변동은 회로 동작에 전기적인 잡음으로 작용한다. 논리 게이트가 이러한 잡음의 영향에 얼마나 둔감한지는 잡음여유(Noise margin)로 표현한다.

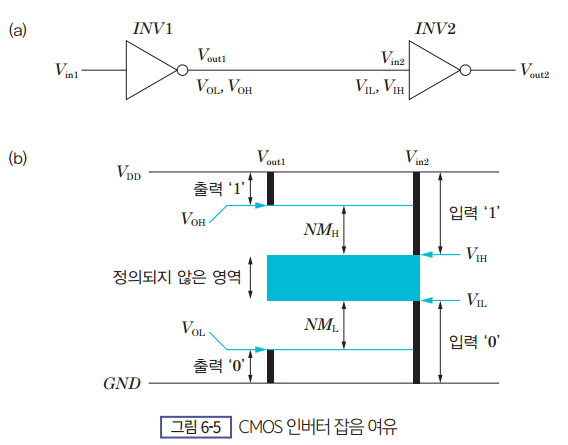

[그림 6-5(a)]와 같이 동일한 특성을 갖는 두 개의 인버터가 직렬로 연결된 경우, 두 번째 인버터가 제대로 동작하기 위해서는 INV1의 VOL, VOH와 INV2의 입력전압 파라미터 VIL, VIH 사이에는 VOL < VIL, VOH > VIH 조건이 충족되어야 한다. 즉, INV1의 VOL이 INV2의 VIL보다 작아야 하며, INV1의 VOH가 INV2의 VIH보다 커야 정상적인 논리 동작이 가능하다. 이를 토대로 인버터의 잡음 여유를 [그림 6-5(b)]와 같이 나타낼 수 있으며, 논리 ‘0’에 대한 잡음여유(Noise Margin Low, NML)와 논리 ‘1’에 대한 잡음여유(Noise Margin High, NMH)를 다음과 같이 정의할 수 있다.

NML = VIL - VOL

NMH = VOH - VIH

이로부터 VOL이 0V에 가까울수록 논리 ‘0’에 대한 잡음여유가 커지고, VOH가 VDD에 가까울수록 논리 ‘1’에 대한 잡음여유가 커짐을 알 수 있다. 즉, VIL과 VIH가 논리 스윙 범위의 중앙에 가까울수록 잡음여유가 커지는 것이다. 인버터의 논리 동작이 정상적으로 수행되기 위해서는 잡음여유가 0보다 커야 하며, 잡음여유가 클수록 전압 변동에 대한 영향을 적게 받아 회로가 안정적으로 동작할 수 있다.

③CMOS 인버터의 DC 특성

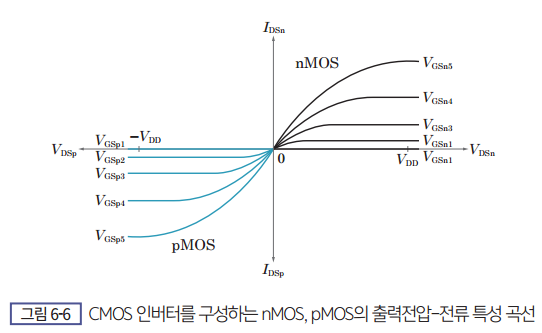

앞서 살펴 본 CMOS 인버터의 DC 전달 특성은 CMOS 인버터를 구성하는 pMOS와 nMOS의 전압-전류 특성 곡선([그림 6-6] 참조)으로부터 얻을 수 있다.

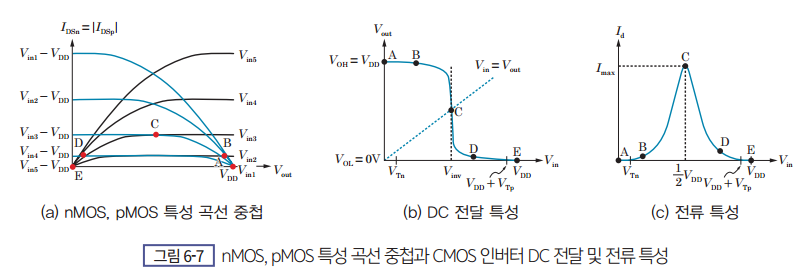

[그림 6-6]과 같이 nMOS, pMOS가 별개로 존재할 경우에는 각각의 입력전압에 따라 출력전류를 독립적으로 조절할 수 있으나 인버터 회로가 구성되면 입출력 단자를 공유하므로 [그림 6-7(a)]와 같이 nMOS, pMOS가 가질 수 있는 바이어스가 고정되어 출력전압 및 전류가 특정 조건으로 한정된다. [그림 6-7(a)]에는 A부터 E까지의 5가지 입력전압에 대한 nMOS와 pMOS의 동작 모드가 나타나 있고, [그림 6-7(b)]와 [그림 6-7(C)]에는 각 입력전압에 따른 CMOS 인버터의 DC 전달 및 전류 특성을 보여 주고 있으며, 이들 전체를 정리하여 [표 6-1]에 나타내었다.

표 6-1 입력 전압에 따른 CMOS 특성

구분 | A점 | B점 | C점 | D점 | E점 |

입력전압 (Vin) | 0 ≤ Vin1 ≤ VT | VTn < Vin2 < | Vin3 ≈ | VDD + VTp ≥ Vin5 ≥ VDD | |

nMOS | 차단 | 포화 | 포화 | 선형 | 선형 |

pMOS | 선형 | 선형 | 포화 | 포화 | 차단 |

출력전압 (Vout) | VDD | ≈ | < | 0 | |

전류(Id) | 0 | Id > 0 | ≈lmax | Id > 0 | 0 |

0 \le V_{in1} \le V_{tn} 인 경우(A점): pMOS는 선형 모드이고, nMOS는 차단 모드이므로, 출력전압은V_{out} = V_{OH} = V_{DD} 가 된다.V_{tn} < V_{in2} < \frac{1}{2}V_{DD} 인 경우(B점): pMOS는 선형 모드이고, nMOS는 포화 모드로 동작하며, 출력전압은\frac{1}{2}V_{DD} < V_{out} < V_{DD}

가 된다.V_{in3} \approx \frac{1}{2}V_{DD} 인 경우(C점): pMOS와 nMOS가 모두 포화 모드로 동작하며, 출력전압은V_{out} \approx \frac{1}{2}V_{DD} 가 되고, 이때 최대 전류가

흐르게 된다.

\frac{1}{2}V_{DD} < V_{in4} < V_{DD} + {V_{tp}}^2 인 경우(D점): pMOS는 포화 모드, nMOS는 선형 모드로 동작하며, 출력전압은V_{out} < \frac{1}{2}V_{DD} 가

된다.

V_{DD} + V_{tp} \ge V_{in5} \ge V_{DD} 인 경우(E점): pMOS는 차단 모드이고, nMOS는 선형 모드로 동작하므로,V_{out} = V_{OL} = 0V 가

된다.

VTp2: pMOS의 문턱 전압(Threshold voltage)

(2) SRAM 개요

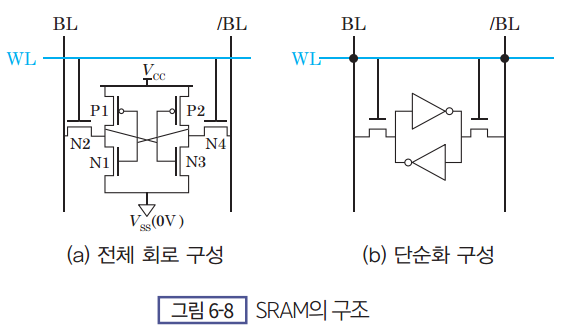

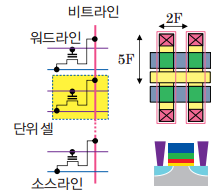

SRAM은 정적 랜덤 액세스 메모리(Static Random Access Memory)를 의미하며, 속도가 빠른(고속) 특성 때문에 컴퓨터를 비롯한 모든 전자 장치의 캐시 메모리(Cache memory)로 주로 사용된다. SRAM의 셀 구조는 [그림 6-8]과 같이 6개의 트랜지스터(6T SRAM)3로 구성되어 있으며, 데이터 저장 역할을 하는 교차 결합의 CMOS 인버터(Inverter)와 데이터를 읽고 쓸 때 데이터의 입출력선 역할을 하는 비트라인(Bit-Line, BL 또는 /BL), 그리고 메모리 셀을 연결하거나 끊는 등의 스위치 역할을 하는 2개의 엑세스(Access) nMOS로 구성된다.

P1, P2, N1, N2, N3, N4 트랜지스터3

CMOS 인버터의 nMOS(N1, N3)를 풀다운(Pull-down) 트랜지스터, pMOS(P1, P2)를 풀업(Pullup)트랜지스터라고 하며, pMOS의 소스에는 동작 전압(VCC)이, nMOS의 소스에는 VSS(0V)가 인가된다. 액세스 nMOS의 게이트를 워드라인(Word-Line, WL)이라 하는데, 한쪽은 CMOS 인버터에, 다른 한쪽은 비트라인 쌍(BL, /BL)에 연결된다. 비트라인은 항상 BL과 /BL 쌍으로 구성되며, /BL은 BL 논리값의 상보(Complementary)4 값을 갖는다.

상보4: 서로 모자란 부분을 보충함. 여기서는 서로 반대의 데이터를 갖는다는 의미임.

데이터 저장 원리는 간단하다. 예를 들어 첫 번째 인버터의 입력이 논리 ‘1’이면 출력은 논리 ‘0’이 되고, 이 출력이 다른 두 번째 인버터의 입력이 되어 출력은 논리 ‘1’이 된다. 이는 첫 번째 인버터의 입력 값과 같은 값이며, SRAM에 전력이 공급되는 한 신호의 입력 논리는 계속 유지(Latch)될 것이다. 따라서 커패시터(Capacitor) 회로를 사용하는 DRAM(Dynamic RAM)처럼 전하 누출이 일어나지 않아 주기적인 리프레시(Refresh) 동작이 필요하지 않으므로, 동적(Dynamic)이라는 말 대신에 정적(Static)이라는 용어를 쓰게 된 것이다. 또한 SRAM의 Random Access(임의 접근)는 임의의 메모리 위치 주소가 주어졌을 때, 여러 메모리 셀 중에서 원하는 셀에 바로 접근이 가능하다는 의미로 사용하게 되었다.

SRAM은 DRAM에 비해 동작 속도가 훨씬 빠르다. 이는 DRAM에서 필요한 리프레시 동작 시간과 쓰기 및 읽기 동작 시 커패시터를 충·방전시킬 시간이 필요하지 않기 때문이다. 그러나 6개의 트랜지스터로 구성되는 만큼 셀의 면적이 크고, 고 집적화가 어렵다는 단점이 있다. 이 외에도 전원이 꺼지면, 데이터를 저장하고 있는 교차 결합 인버터의 전원(VDD, VSS)이 공급되지 않아 데이터를 유지할 수 없다는 단점이 있다(휘발성 메모리).

(3) SRAM의 읽기(Read) 동작

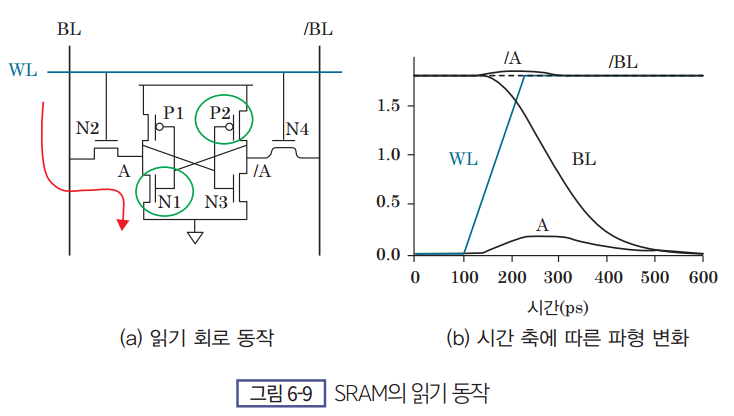

SRAM의 읽기(Read) 동작은 [그림 6-9]와 같다.

ⅰ) 먼저 단자 A에 논리 ‘0’, /A에 논리 ‘1’이 저장되어 있다고 가정한다.

ⅱ) 이 상태에서 N1, P2 트랜지스터는 ON 상태, N3, P1은 OFF 상태이다.

ⅲ) 읽기 동작 전 대기 상태에서 이미 예비 충전(Pre-charge)되어 있던 양 비트라인(BL, /BL)의 예비 충전 전원을 끊어 부유(Floating)

시킨다.

ⅳ) 워드라인(WL)을 ON시킨다.

ⅴ) BL에 충전되어 있던 전하가 N2 및 N1을 통해 접지로 빠지면서 BL의 전위는 0V로 내려가 단자 A의 논리 ‘0’이 BL에 반영된다. 이때, 단자 A의 전위가 BL의 높은 전위에 의해 일시적으로 상승하게 되는데, N2 대비 N1 트랜지스터의 전류 구동 능력이 낮으면 이러한 전위의 상승이 심해져 논리 값이 바뀌어 버리는 불량이 발생할 수 있다. 따라서 통상, N1 트랜지스터의 폭(Width)은 N2의 폭보다 크게 설계한다 (WN1≒1.5WN2).

ⅵ) 단자 /A는 원래 논리 ‘1’이었으므로 /BL의 논리 ‘1’에 대해 순간적인 전위의 상승을 보이지만 별 문제 없이 원래의 값을 유지하게 된다.

ⅶ) 전압 감지 증폭기(Sense Amplifier, S/A)가 BL과 /BL의 전위차를 감지 및 증폭하여 데이터를 외부로 내보낸다.

ⅷ) 워드라인을 OFF시킨다.

(4) SRAM의 쓰기(Write) 동작

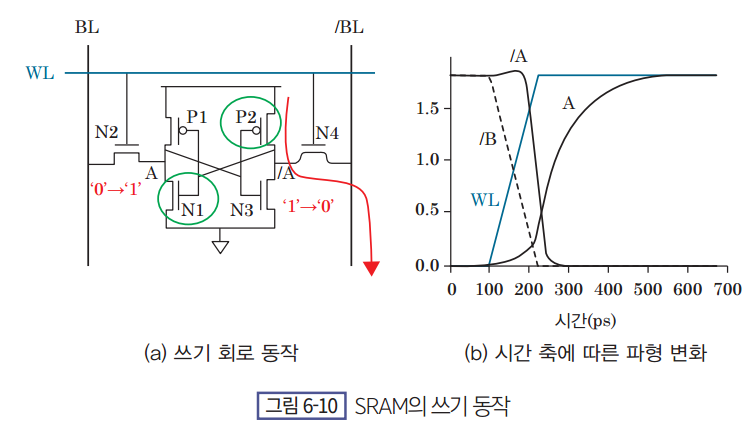

SRAM의 쓰기(Write) 동작은 [그림 6-10]과 같다.

ⅰ) 단자 A에 논리 ‘0’, /A에 논리 ‘1’이 저장되어 있다고 가정한다.

ⅱ) 이 상태에서 N1, P2 트랜지스터는 ON, N3, P1은 OFF 상태이다.

ⅲ) 이제, 이전과는 반대로 A에 논리 ‘1’, /A에 논리 ‘0’을 쓰고자 한다.

ⅳ) 외부에서 BL에 논리 ‘1’, /BL에 논리 ‘0’에 해당하는 전압을 인가한다.

ⅴ) 워드라인(WL)을 ON시킨다.

ⅵ) ON 상태였던 P2와 N4 트랜지스터를 통해 0V로 인가된 /BL로 전류가 흐르면서 단자 /A의 전위가 내려간다. 이때, ON 상태에 있던 P2 트랜지스터의 전류 구동 능력보다 N4의 전류 구동 능력이 커야 /A 단자의 전위가 내려갈 수 있다(WN4≒1.5WP2).

ⅶ) 내려간 단자 /A의 전위로 인해 단자 A의 전위는 올라가고 단자 A와 /A의 논리 값이 이전 상태와 반대로 바뀌어 쓰기 작업이 달성된다.

ⅷ) 워드라인을 OFF시킨다.

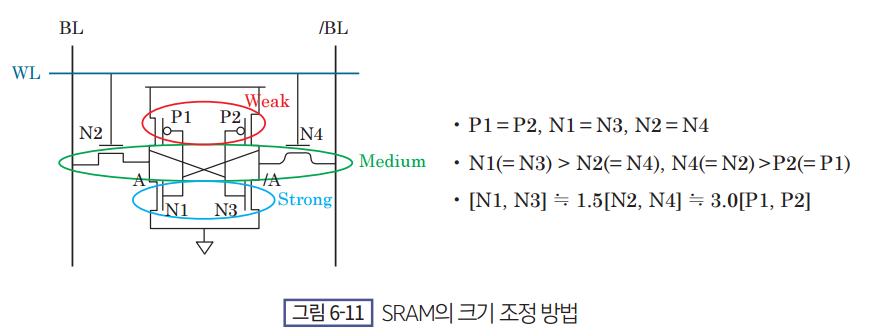

(5) SRAM 셀 크기 조정(Sizing)

앞에서 설명한 SRAM의 동작을 정리하면, 읽기 동작과 쓰기 동작에서 한가지 상충된 사실을 이끌어 낼 수 있다. 읽기 동작 시에는 비트라인(BL) 전위에 의해 셀의 논리 값이 바뀌지 않아야 하는 반면, 쓰기 동작 시에는 셀이 새로운 값으로 바뀌어야 한다는 사실이다. 이를 위해, [그림 6-11]과 같이 셀의 트랜지스터 크기(Size)를 정밀히 조정할 필요가 있다. 즉, 두 인버터를 구성하는 nMOS, pMOS와 액세스 nMOS의 크기가 대칭적으로 동일해야 하며, 그 크기는 인버터 풀 다운 nMOS(N1, N3), 액세스 nMOS(N2, N4), 풀업 pMOS(P1, P2) 순이어야 한다.

3 DRAM(Dynamic Random Access Memory)

DRAM은 1966년 IBM의 연구원이었던 R.H Dennard에 의해 발명되었고, 이후 수많은 발전을 거듭하여 서버, PC 등의 컴퓨팅(Computing) 장치는 물론, 모바일(Mobile) 기기 및 TV 등을 포함한 거의 모든 전자 기기에 사용되고 있다. 상대적으로 빠른 동작 속도와 큰 메모리 용량 덕분에 주 메모리(Main memory) 역할을 하고 있고, 반도체 산업에서 매우 중요한 위치를 차지하는 메모리 소자이다.

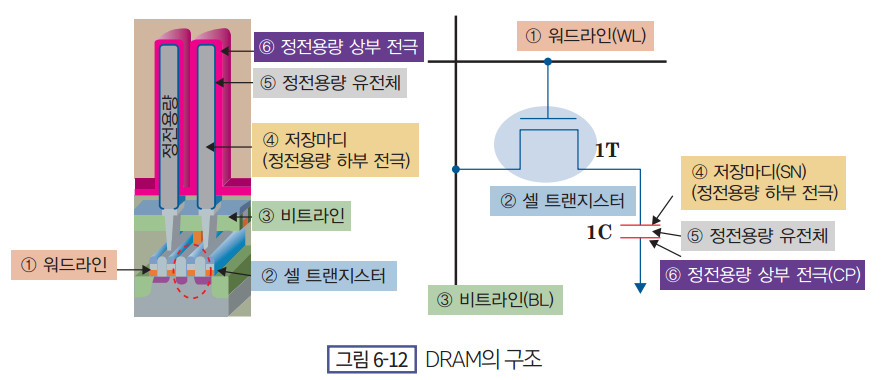

(1) DRAM 셀(Cell)의 구조

기본 DRAM 셀은 [그림 6-12]와 같이 MOS 트랜지스터(Transistor) 1개와 커패시터(Capacitor) 1개로 구성된 1T1C 구조를 갖는다. 각 셀에는 1비트(Bit)의 정보가 저장될 수 있다. DRAM 셀에서 MOS트랜지스터는 스위치 역할을 하고, 커패시터는 데이터 저장의 역할을 한다.

세부적으로 DRAM 셀의 구조를 살펴보도록 하자. 먼저 셀 트랜지스터의 한쪽은 데이터가 드나드는 비트라인(BL)과 연결되고, 다른 한쪽은 데이터가 저장되는 셀 커패시터에 연결되어 있다. 셀 트랜지스터는 비트라인과 커패시터 사이를 연결하거나 끊는 스위치 기능을 하여, 접근(Access) 또는 관통(Pass) 트랜지스터라고도 불린다. 이 트랜지스터의 게이트(Gate)를 워드라인(Wordline, WL)이라고 하는데, 뒤에서 설명할 가로, 세로 메트릭스(Matrix) 구조의 셀 어레이(Cell array)에서 가로(Row, 행, X) 주소(Address)가 지정됐을 때 선택되는 라인(Line)을 말한다. 워드라인은 원래 n형으로 고농도 도핑된 다결정 실리콘 물질이면서 2차원 평면 구조였으나, 최근에는 텅스텐 또는 티타늄 질화물(TiN)과 같은 금속 물질과 3차원 입체 구조로 변화하였다. 다음, 비트라인(BL)은 텅스텐 등의 금속 물질로 되어 있으며, 쓰기나 읽기 동작 시에 셀 외부에서 셀 내부로(쓰기), 혹은 그 반대 방향(읽기)으로 데이터가 이동하는 통로 역할을 하는 선이다. 후술할 가로, 세로 매트릭스 구조의 셀 어레이에서 세로(Column, 열, Y) 주소가 지정됐을 때, 바로 이 비트라인이 선택된다. BL은 항상 반대의 데이터를 갖는 /BL와쌍(Pair)으로 동작하며, 그 이유에 대해서는 후술할 DRAM 셀의 읽기(Read) 동작에서 상세히 설명하도록 하겠다.

데이터를 저장하는 셀 커패시터에 대해 살펴보자. 셀 커패시터의 두 전극 중 셀 트랜지스터에 가까운 하부 전극은 스토리지 노드(Storage Node, SN)라 하고, 상부 전극은 셀 플레이트(Cell Plate, CP)라고 한다. 두 전극은 초기에 다결정 실리콘 물질이었다가 최근 티타늄질화물(TiN) 또는 루테늄(Ru) 등의 금속 물질로 변화되었다. 두 전극 사이에는 유전체가 삽입되어 있는데, 이 또한 초기에는

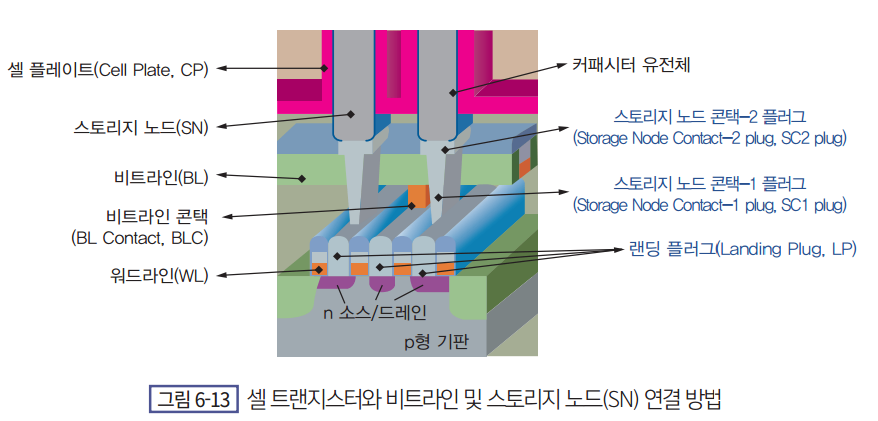

nMOS의 소스는 드레인 대비 낮은 전압이 인가되는 단자이므로 DRAM 셀의 경우는 비트라인(BL)이나 커패시터의 스토리지 노드(SN) 중 높은 전압이 인가되는 쪽이 드레인이 된다. 즉, 소스와 드레인이 정해져 있지 않은 구조인 것이다. 지금부터는 셀 트랜지스터의 소스와 드레인 접합(Junction)과 비트라인(BL) 및 스토리지 노드(SN)가 어떻게 연결되는지 알아보도록 하겠다. [그림 6-13]과 같이 셀 트랜지스터의 게이트(WL, 워드라인) 사이에는 n형 불순물이 도핑된 다결정 실리콘층이 형성되는데 이를 랜딩 플러그(Landing Plug, LP)라고 한다. 여기서 비트라인(BL)이 비트라인 콘택(BL Contact, BLC)을 통해 이 랜딩 플러그(LP)와 접속하고, 셀 트랜지스터와 연결된다. 커패시터의 스토리지 노드(SN)부는 랜딩 플러그(LP) 위에 n형 불순물이 도핑된 다결정 실리콘의 스토리지 노드 콘택-1과 2 플러그(Storage Node Contact 1&2, SC1&2 plug)를 순차적으로 형성함으로써, 스토리지 노드(SN)와 셀 트랜지스터를 연결시킨다. DRAM 제작 공정은 업체마다 상이하고 복잡하므로, 본 서에서는 다루지 않기로 한다.

(2) DRAM 셀에 사용되는 내부 전압

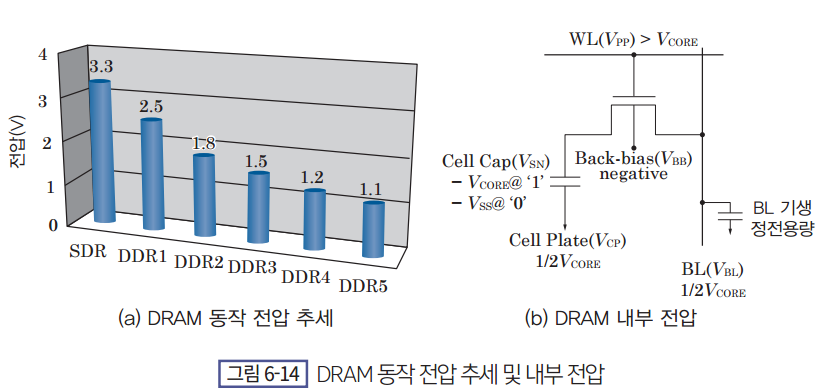

DRAM의 외부에서 인가되는 동작 전압은 내부의 전압 생성 회로를 거쳐 다양한 전압 수준으로 변환되어 사용된다. 동작 전압은 저 전력화 추세에 따라 기존 3.3V의 SDR(Single Data Rate DRAM)에서 현재는 D(Double) DR-5의 1.1V까지 감소되어 왔다([그림 6-14(a)] 참조).

DRAM의 내부 전압에는 셀 커패시터의 스토리지 노드에 걸리는 전압(VSN)과 트랜지스터의 게이트에 걸리는 워드라인 전압, 그리고 VBL 및 VCP, VBB가 있는데, 순서대로 알아보기로 하자. 우선, [그림 6-14(b)]와 같이 셀 커패시터의 스토리지 노드(SN)단에 걸리는 전압 중 논리 ‘1’을 나타내는 전압을 코어 전압(Core voltage, VCORE)이라고 한다.5 즉, ‘1’이 저장된 경우에는 셀 커패시터의 스토리지 노드(SN)에 코어 전압(VCORE)이 걸리고, ‘0’이 저장된 경우에는 접지 전압(VSS)이 인가된다는 것이다. 코어 전압(VCORE)은 DRAM의 동작 전압보다 낮은 값을 갖는다.

물론 논리 ‘0’은 접지 전압(VSS) 0V임.5

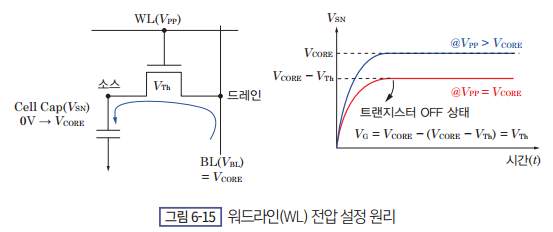

셀 트랜지스터의 게이트(WL)에는 VPP라는 전압이 인가된다. 이 전압은 DRAM에서 사용되는 전압 중 가장 높은 전압으로서, DRAM 내의 승압 회로에 의해 생성된다. 이렇게 높은 전압을 설정하는 이유는 셀에 논리 ‘1’ 저장 시, 비트라인(BL)에 인가된 코어 전압(VCORE)이 셀 트랜지스터를 통해 스토리지 노드(SN)에 온전히 전달되게 하기 위함이다. 셀에 논리 ‘1’을 저장한다는 것은 워드라인(WL)에 전압을 인가하여 셀 트랜지스터를 ON시킨 후, 외부로부터 비트라인(BL)에 논리 ‘1’의 코어 전압(VCORE)을 인가하여 코어 전압(VCORE)이 스토리지 노드(SN)까지 전달되도록 하는 동작을 의미한다. 만약 [그림 6-15]와 같이 워드라인(WL) 전압이 코어 전압(VCORE)에 비해 충분히 높지 않다면, 쓰기 동작에서 비트라인(BL) 대신 상대적으로 전압이 낮은 스토리지 노드(SN) 접합부가 소스가 된다(해당 스토리지 노드(SN)가 논리 ‘0’ 데이터를 저장하고 있는 경우). 그리고 시간이 경과함에 따라 소스 전압이 상승해 워드라인(WL)인 게이트의 전압(VG)과 소스인 스토리지 노드 접합부 전압(VS)의 차이(VG -VS, VGS)가 셀 트랜지스터의 문턱 전압(VTh)과 같게 되는 순간, 셀 트랜지스터는 OFF 상태가 된다. 더 이상 스토리지 노드(SN) 접합부의 전압이 상승하지 않아 스토리지 노드(SN)의 전압이 코어 전압(VCORE)에 도달하지 못하게 되는 것이다. 따라서 워드라인(WL) 전압은 코어 전압(VCORE)보다 높게 설정해야 하며, 통상 ‘코어 전압(VCORE) + 3VTh 레벨’ 또는 게이트 산화막의 신뢰성 등을 고려한 적정 수준으로 설정해야 한다. 또한, 트랜지스터를 OFF하기 위해서는 통상 0V를 게이트에 인가하는데, 소자 미세화로 인해 트랜지스터의 문턱 전압이 감소하면서 OFF 상태 누설 전류(IOFF)를 무시하지 못하게 되었고, 0V가 아닌 음의 전압을 인가해 오프 상태 누설 전류(IOFF)를 억제하는 방안이 제안되어 사용 중에 있다. 이를 부-워드라인 전압(Negative Wordline, NWL) 구조라 한다.

다음은 비트라인(BL) 예비 충전 전압(Pre-charge voltage)을 의미하는 VBL과 셀 커패시터의 셀 플레이트 전압을 의미하는 VCP이다. 두 전압 모두

마지막으로 음의 전압을 인가해주는 기판 전압(VBB)이 있다. 이렇게 기판 전압에 음전압을 인가하는 목적에는 두 가지가 있다. 첫째, 기판 바이어스 효과에 의해 셀 트랜지스터의 문턱 전압을 증가시켜 오프 상태 누설 전류(IOFF)를 줄이기 위함이고, 둘째, 셀 트랜지스터의 소스, 드레인과 기판 사이의 공핍 영역 폭(Depletion width)을 증가시켜 비트라인 기생용량(CB)을 감소시킬 수 있기 때문이다.

(3) DRAM의 아키텍처(Architecture)6

아키텍처6: 컴퓨터의 기능적 구조(소프트웨어) 또는 물리적 구조(하드웨어)를 의미함. 여기서는 DRAM의 회로 구성 또는 구조를 의미함.

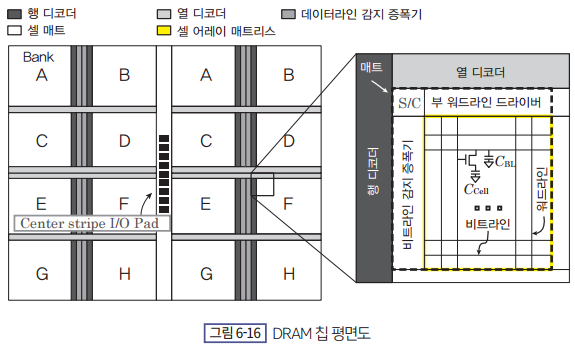

업체 및 제품에 따라 상이하지만, 기본적인 DRAM 칩(Chip)의 평면도(Floor plan)는 [그림 6-16]과 같다. DRAM 칩은 크게, 주변 회로(Peripheral circuitry), 코어 회로(Core circuitry) 및 셀 에레이(Cell array)로 구성되며, 코어 회로와 셀 어레이를 합쳐 셀 매트(Cell mat)라고 한다. 주변 회로는 칩 중앙부의 가로, 세로 라인에 각종 제어회로 및 입출력 패드(I/O pad), 그리고 행(Column)과 열(Row)의 디코더(Decoder) 등으로 구성된다. 코어 회로는 감지 증폭회로(Sense Amplifier, S/A) 및 부 워드라인 드라이버(Sub-Wordline Driver, SWD), 그리고 Sub-hole Control(S/C) 회로로 구성되며, 각각은 다음과 같은 역할을 한다.

감지 증폭회로(Sense Amplifier, S/A): BL과 /BL 사이의 미세한 전압 차이를 감지하고, 논리 ‘1’(VCORE)과 논리 ‘0’(VSS)으로 증폭시키는 역할을 한다.

부 워드라인 드라이버(Sub-Wordline Driver, SWD): 열 디코더에서 신호를 받아 해당 셀 매트 내 셀 어레이의 워드라인에 고전압인 VPP를 인가하여 워드라인을 선택하는 역할을 한다.

Sub-hole Control(S/C) 회로: 감지 증폭회로(S/A)와 부 워드라인 드라이버(SWD)가 교차하는 부분의 공간(Hole)

이 외에도, [그림 6-16]의 평면도에서 ‘Bank’라는 개념을 찾을 수 있다. 뱅크(Bank)란 셀 매트를 블록 형태로 구분한 것을 말한다. DRAM은 내부에서 입출력을 공유하지만 독립적으로 제어가 가능하므로, 마치 복수의 DRAM이 내부에 존재하는 것처럼 동작한다. 또 한가지, 바로 셀 효율(Cell efficiency)이라는 중요한 파라미터가 있는데 이는 전체 칩 면적에서 셀 어레이가 차지하는, 즉 순수하게 셀이 차지하는 면적의 비율로 정의되며, 통상 40~50% 수준이다. 이 값이 클수록 칩이 경제적으로 설계되었다는 의미이고, 모든 회로 설계는 JEDEC(Joint Electron Device Engineering Council) 등의 사양을 기본적으로 만족해야 한다.

(4) DRAM의 동작 원리

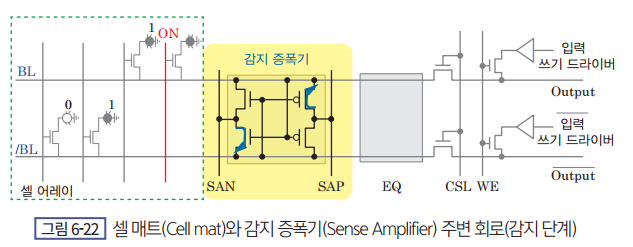

① DRAM 셀 어레이와 감지 증폭기(Sense Amplifier, S/A) 회로

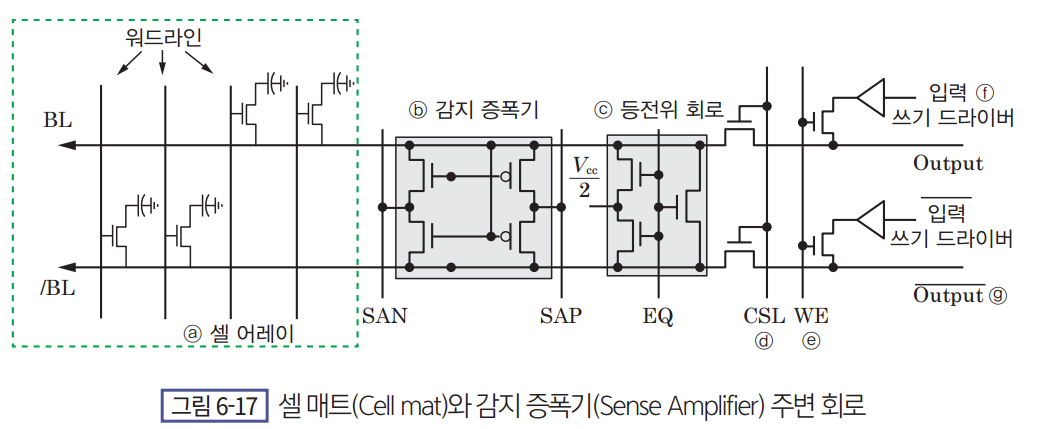

DRAM의 동작 원리를 설명하기 전에, 셀 매트 내 셀 어레이와 감지 증폭기(S/A) 회로의 구조를 설명하고자 한다. 후술할 내용들은 셀 어레이 구조 중에서도 [그림 6-17]에 나타낸 폴디드 비트라인(Folded BL) 구조를 기준으로 하겠다. [그림 6-17]의 좌측부터 보면, 점선 박스로 둘러진 부분이 ⓐ 셀 어레이(Cell array)이고, 그 우측의 회로가 ⓑ 감지 증폭기(S/A)이다. 감지 증폭기는 SRAM 셀과 같이 CMOS 인버터의 입출력이 서로 교차되어 있다. 그 우측의 회로는 ⓒ 등전위 회로(Voltage Equalization Circuit)인데, 대기(Stand-by) 상태의 BL과 /BL을 예비 충전(BL pre-charge)시켜 동일 전위로 만들어 주는 역할을 한다. 등전위 회로의 우측에 보이는 라인은 ⓓ CSL(Column Select Line)이다. 이 신호가 ON되면 해당 행(Column)에 달려 있는 트랜지스터의 게이트가 열려, 데이터가 셀에서 외부로 ⓖ Output을 통해 나가거나(Read), 외부에서 셀로 Input을 통해 들어올 수(Write) 있게 된다. 맨 우측의 회로는 쓰기(Write) 동작 시에 사용되는 회로로, ⓔ WE(Write Enable) 신호가 들어오면(물론 CSL도 ON 상태에서) ⓕ 입력 쓰기 드라이버(Input write driver)에서 BL과 /BL을 타고 데이터가 들어와 셀에 저장된다.

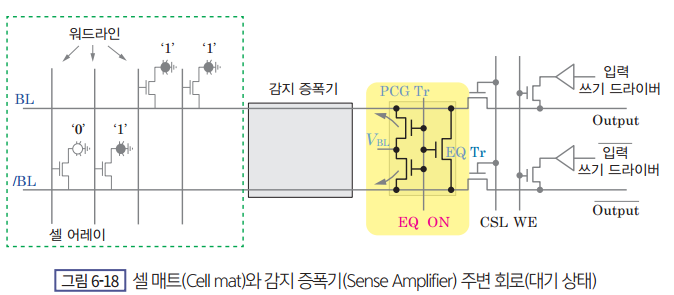

② 대기(Stand-by) 상태

대기 상태에서는 ‘BL과 /BL을 동일한 전위로 만드는 등전위 트랜지스터(EQ transistor)’와 ‘BL에 예비 충전 전압(VBL)을 공급하는 2개의 예비 충전 트랜지스터(PCG(Pre-charge) transistor)’의 게이트(EQ)에 전압을 인가하여 3개의 트랜지스터를 모두 ON시킨다. 그러면 BL과 /BL 라인은 예비 충전(Pre-charge)되어 예비 충전 전압 VBL(=

③ 읽기(Read) 동작

▣ 접근 단계 (Access step)

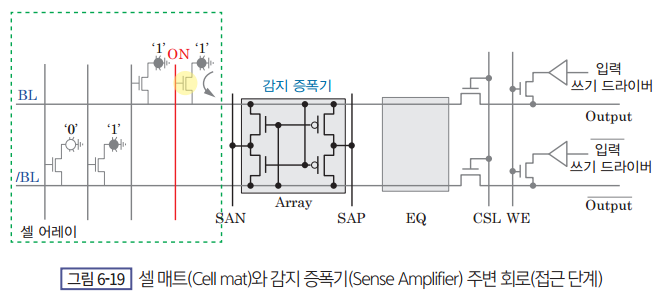

ⅰ) [그림 6-19]와 같이, EQ에 0V를 인가하여 등전위 트랜지스터(EQ Tr)와 예비 충전 트랜지스터(PCG Tr)를 OFF시키면, BL과 /BL 라인은 부유(Floating) 상태가 되어 예비 충전 전압(VBL)의 공급이 끊기게 된다. 하지만 BL과 /BL의 기생 커패시터에 충전된 전하에 의해, BL과 /BL은 예비 충전 전압(VBL)을 당분간 유지한다.

ⅱ) 이러한 부유 상태에서, 셀 에레이 내 논리 ‘1’이 저장된 목표 셀(Target cell)의 워드라인(WL)이 선택(ON)된다([그림 6-19]의 붉은색 선).

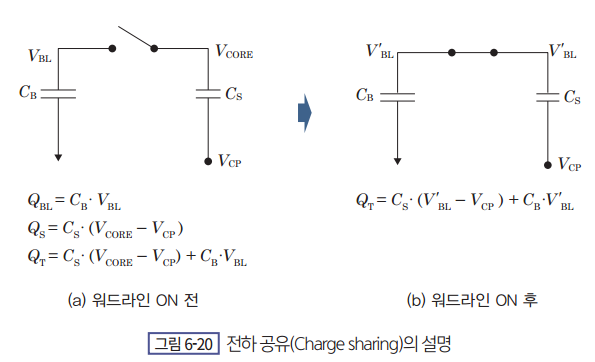

ⅲ) VCORE(논리 ‘1’)로 충전되어 있던 셀 커패시터 내의 전하가 셀 트랜지스터를 통해 BL로 나와 BL의 기생 커패시터의 전하와 전하 공유 (Charge sharing)를 하게 된다. 이 과정은 DRAM동작에서 가장 중요한 부분이므로, 좀 더 상세히 설명하도록 하겠다. 먼저, [그림 6- 20]의 각 회로의 중앙에 셀 트랜지스터를 스위치로 모사하였고, 스위치의 좌측은 BL의 기생 커패시터, 우측은 셀 커패시터를 나타내었다.

셀 커패시터의 상부 전극인 스토리지 노드(SN)에는 코어 전압(VCORE)이 인가되어 논리 ‘1’ 상태이고, 다른 쪽 전극인 셀 플레이트(CP)에는 VCP(=

여기서 VCP는 계산 과정에서 소거되어 V'BL에 영향을 주지 않으므로, VCP는 셀 커패시터의 누설 전류를 최소화할 수 있는

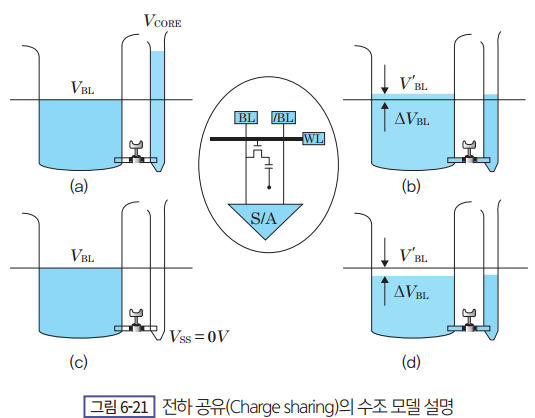

지금까지 설명한 내용을 좀 더 이해하기 쉽게 수조 모델로 알아보자. [그림 6-21]처럼 전기 소자인 커패시터를 물을 담는 수조라고 하면, 수조의 크기를 정전용량(Capacitance, C)으로 모사할 수 있다. 정전용량의 차이에 따라 큰 수조는 기생 커패시터, 작은 수조는 셀 커패시터를 나타내는데, 이는 BL에 수백~수천 개의 셀이 달려 있어 BL의 기생 커패시터 정전용량(pF7 수준)이 의도적으로 만든 셀 커패시터의 정전용량(fF8 수준)에 비해 크기 때문이다. 그리고 하늘색으로 나타낸 수조 속 물의 양은 전하(Q)를 나타내고, 수조 속 물의 높이가 바로 전위(전압)를 의미한다.

pF7: picoF이며 10-12F를 의미함.

fF8: femtoF이며 10-15F를 의미함

[그림 6-21(a)]는 셀 커패시터에 논리 ‘1’ 상태의 고전압(VCORE)이 인가되어 있고, 비트라인(BL)은

ⅳ) 한편, DRAM은 이렇게 변화된 전위(V'BL)를 가지고 어떻게 논리 ‘0’ 혹은 논리 ‘1’을 구분해 낼 수 있을까? [그림 6-19]의 DRAM 셀 어레이에서 목표 셀(Target cell)이 연결된 BL과 다르게, /BL은 이 상태에서도 여전히 예비 전압(VBL)으로 예비 충전(Pre-charge)된 상태이다. 그리고 이 BL과 /BL의 전위차(ΔVBL)를 가지고 논리 ‘0’과 ‘1’을 구분할 수 있다는 것이다.

앞의 수조 모델에서와 같이 ΔVBL은 실제로도 매우 작은 값이며, ΔVBL이 가능한 한 클수록 DRAM의 오작동을 방지할 수 있다. 따라서 다음 식에 의해 코어 전압(VCORE)과 CS가 클수록, CB는 작을수록 더 큰 ΔVBL을 얻을 수 있다. 이때 코어 전압(VCORE)은 DRAM 설계 시 결정되는 설계 변수 값이다.

위 식에서 CB/CS 비율(CB/CS ratio)이 소자·공정 측면에서 매우 중요하며, 우리가 다양한 방법으로 셀 정전용량을 증가시키고 비트라인 기생 정전용량을 줄이는 이유가 여기에 있다.

▣ 감지 단계(Sensing step)

이제는 이 작은 전압 차이(ΔVBL)를 크게 증폭하는 단계가 필요하다. 즉, 목표 셀(논리 ‘1’)이 달린 BL은 코어 전압(VCORE) 수준으로, 다른 쪽 /BL은 VSS(0V)로 크게 증폭하는 것이다. 이때 사용하는 장치가 감지 증폭기(Sense Amplifier, S/A)이고, 작은 전압 차이를 감지해 큰 전압으로 증폭하는 역할을 한다.

감지 증폭기(S/A)는 SRAM 셀과 유사하게 두 개의 교차 결합(Cross coupled)인 CMOS 인버터(Inverter)로 구성된다. BL과 /BL 간 작은 전압 차이(ΔVBL)가 감지 증폭기(S/A) 회로 양단에 걸리면, nMOS 감지 증폭기 제어 신호인 SAN(VSS)이 켜지고 /BL의 전위를 끌어내리게 된다. 즉, SAN이 켜지면 감지 증폭기의 아래쪽 nMOS의 전도도가 증가하여 /BL이 VBL에서 0V로 하강하게 된다는 것이다. 유사하게, pMOS 감지 증폭기 제어 신호인 SAP(VCORE)는 BL을 논리 ‘1’인 코어 전압(VCORE)으로 끌어올린다. SAN 및 SAP 제어 신호는 감지 증폭기(S/A)가 각각의 최대(VCORE) 또는 최소 전압(0V)으로 구동되도록 하는 역할을 한다.

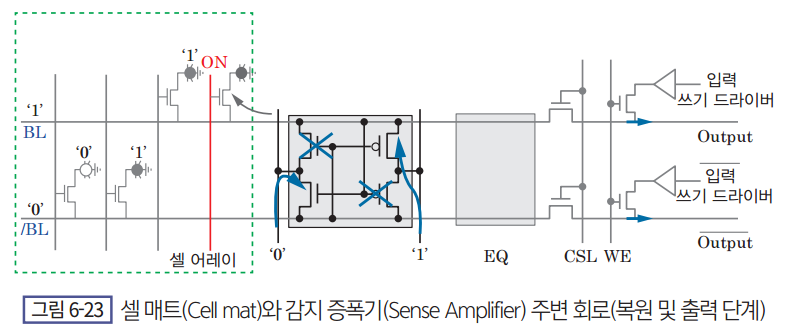

▣ 복원 및 출력 단계(Restore&Output step) ([그림 6-23] 참조)

이 단계에 와서도 워드라인(WL)은 여전히 ON 상태로 있다 따라서 코어 전압(VCORE) 및 VSS로 완전히 벌어진 BL과 /BL 전압은 셀 트랜지스터를 통해 셀 커패시터의 전하를 복원하게 된다. 즉, 셀 커패시터에 전하가 재 충전되면서 앞서 설명한 파괴적 읽기(Destructive readout)의 문제가 해결된다는 말이다. 이와 동시에, 그림의 CSL(Column Select Line)에 전압이 인가되면 CPU로부터 요청된 데이터가 Output line을 통해 내보내진다. 그리고 모든 동작이 완료되면 워드라인(WL)에 0V가 인가되면서 셀 트랜지스터가 OFF되고, EQ는 ON이 되어 다시 대기 상태로 돌아간다.

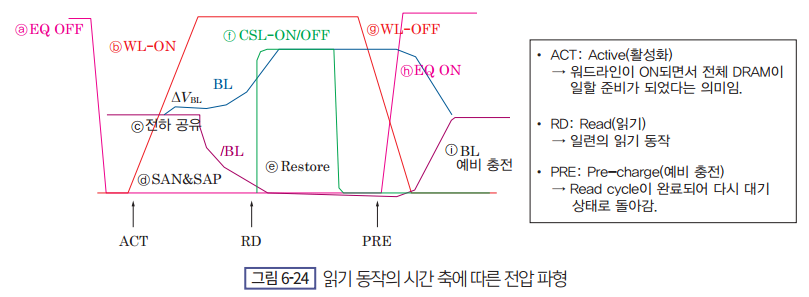

지금까지 설명한 읽기 동작을 시간 축에 대한 전압 그래프([그림 6-24] 참조)로 정리해 보자. 전체 읽기 동작 시간은 수십ns 수준이며, 이 그래프를 통해 우리가 왜 BL 예비 충전 전압(VBL)을

④ 쓰기(Write) 동작

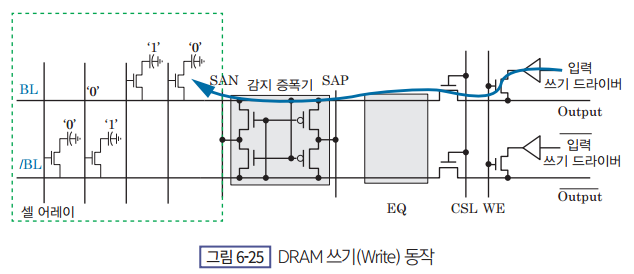

[그림 6-25]는 DRAM의 쓰기(Write) 동작을 나타낸다. 데이터를 저장할 행과 열 주소(Address)가 지정되면, 워드라인(WL)과 CSL이 ON되고, CPU로부터 쓰기 명령어(WE 신호)가 입력된다. 그러면 신규 데이터가 입력 쓰기 버퍼(Input write buffer)를 거쳐 목표 셀(Target cell) 및 감지 증폭기(S/A)의 데이터를 덮어 씌우고(Over-writing), 이전의 데이터는 바뀌게 된다. 이후 다시 워드라인(WL)이 OFF되고 대기 상태로 돌아감으로써 쓰기 작업이 완료된다.

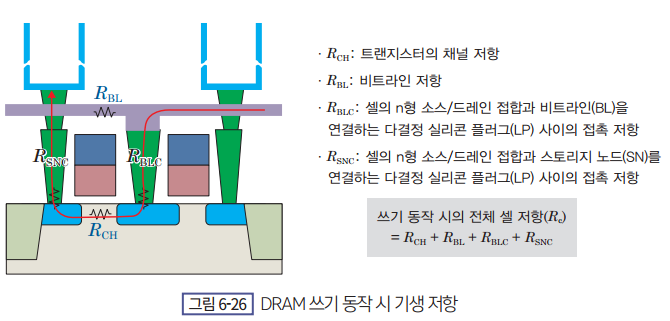

쓰기 동작에 있어서 메모리 셀의 저항이 중요시되는데, 이러한 셀 저항은 [그림 6-26]과 같은 기생저항으로 구성된다. 이들 저항이 높을 경우, 정해진 쓰기 시간 내에 셀 커패시터로의 전하 저장이 충분히 이루어지지 못하는 문제가 있으며, DRAM의 미세화(Scaling)에 따라 이는 더 심각해진다. 한가지 대안으로 워드라인(WL)에 인가되는 전압(VPP)을 증가시켜 트랜지스터의 채널 저항(RCH)을 감소시킬 수 있으나, 게이트 산화막의 신뢰성과의 합치점을 찾는 노력이 필요하다.

⑤ 리프레시(Refresh) 동작

ⅰ) 셀 누설 전류(Cell leakage current)

DRAM은 셀 커패시터에 전하를 저장하는 방식의 메모리 소자이므로, 다양한 경로를 통한 전하 유출은 데이터 손실 문제를 일으킨다. 이에 본 절에서는 셀 어레이(Array) 내에 어떤 누설 경로가 있고, 그 원인과 대책은 무엇인지 알아보도록 하자.

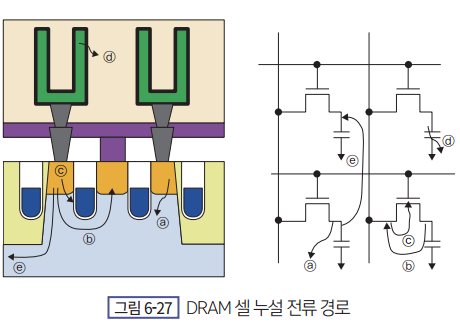

[그림 6-27]의 ⓐ는 셀 커패시터의 스토리지 노드(SN)와 연결된, 셀 트랜지스터에서 발생하는 PN 접합 누설 전류이다. PN 접합 누설 전류의 원인은 두 가지로 나눌 수 있다. 먼저 순수한 접합부에서의 누설 전류이다. 이는 접합부의 고농도 도핑에 의한 고 전계 형성 또는 공정 문제(이온 주입 및 플라즈마에 의한 손상, 금속 오염, STI 접경부 결함 등)에 의한 PN 접합의 결함(Defect)으로 발생한다. 대책으로는 적절한 채널 도핑에 의한 전계 감소 및 저손상 공정, 손상 회복을 위한 열처리 공정 적용 등이 있다. 또 다른 원인은 게이트에 의해 유도된 드레인 누설 전류(Gate Induced Drain Leakage, GIDL)이다. 이 내용은 MOSFET 단원에서도 다룬 내용으로, 스토리지 노드(SN) 접합부와 게이트가 겹치는 부분에서 발생하는 누설 전류이다. 이는 전하 보유 능력(Retention time) 특성에 가장 많은 영향을 주는 인자로 알려져 있으며, 특히 부 워드라인 전압(Negative wordline, NWL) 구조에서 이 문제가 더욱 심각해질 수 있다. 발생 원인 및 대책에 대해서는 MOSFET 단원을 복습하기 바란다.

ⓑ는 셀 트랜지스터의 OFF 상태 전류로서, 단 채널 효과 및 낮은 문턱 전압이 주 원인이다. 스토리지 노드(SN) 접합부의 전계 증가를 최소화하면서 OFF 상태의 누설 전류를 감소시킬 수 있는 구조적 대책 또는 채널 도핑 농도 증가와 같은 대책이 필요하다. 이것은 후술할 소자 격리를 통한 누설 전류(ⓔ)와 함께, 정적 리프레시(Static refresh) 특성은 물론 주변 셀의 동작 환경에 의해 영향을 받는 동적 리프레시(Dynamic refresh) 특성이 악화되는 원인이 된다.

ⓒ는 대기 상태에서 스토리지 노드(SN) 접합부와 게이트 산화막 사이에 흐르는 누설 전류이다. 이는 게이트 산화막이 국부적으로 얇아지거나 공정 과정에서 생길 수 있는 핀 홀(Pin hole)등의 결함으로 인해 스토리지 노드(SN)의 전하가 게이트로 빠져나가는 현상이다. 실리콘을 식각하여 채널 길이를 증가시키는 RCAT(Recess Channel Array Transistor) 등의 구조에서 발생할 수 있으며, 균일한 산화막을 얻지 못할 때 얇아진 국소 부분으로 전계가 집중되면서 누설 전류가 생긴다. 실리콘 기판의 결정면에 따라 균일한 두께의 산화막을 형성할 수 있는 라디칼(Radical) 산화 방식 등을 적용하여 해결할 수 있다.

ⓓ는 셀 커패시터의 유전체를 통한 누설 전류를 가리킨다. DRAM은 셀 커패시터에 전하를 저장하는 방식의 메모리 소자이므로, 셀의 정전용량을 가능한 한 증가시켜야 한다. 물론 정전용량의 증가에 따라 충·방전 시간으로 인한 소자 속도 저하가 있을 수 있으나, 충·방전 시간에 영향을 줄 만큼 큰 정전용량을 얻는 것이 현대 공정 기술에서는 불가능하다. 따라서 정전용량을 증가시키기 위해 커패시터의 유전체 두께를 감소시키는 방법을 사용하는데, 이 경우 직접 터널링에 의한 누설 전류 문제가 발생할 수 있다. 앞서 고 유전율 절연막 금속게이트(HKMG) MOSFET에서 설명한 바와 같이, 고 유전율(High-k) 물질을 상대적으로 두껍게 증착하여 대응하고 있지만, 워낙 커패시터 면적이 좁기 때문에 정전용량 확보와 누설 전류 감소의 양립이 생기게 마련이다. 이는 DRAM 미세화(Scale-down) 시 가장 큰 제약 사항 중 하나이다.

ⓔ는 셀 도면상 가까운 활성(Active) 영역 간의 소자 격리를 통한 누설 전류이다. 원인으로는 주로 포토9 및 식각10 공정 등에 의한 물리적 불량(패턴 및 임계 선폭(Critical Dimension, CD) 불량 등)이 있으나, 필드(Field) 위를 지나가는 게이트에 의한 기생 필드 트랜지스터 문턱 전압 저하로 인한 누설 전류도 가능한 원인이다. 이에 대해서는 적정 필드 차단 이온 주입(Field stop ion implant) 조건을 찾아 적용하는 것으로 대응할 수 있다.

포토 공정9: 집적회로 제조 과정에서 감광성 고분자 물질(포토레지스트)을 이용해, 마스크(Mask) 상의 회로 패턴을 웨이퍼에 전사시키는 공정

식각 공정10: 반도체 공정 과정 중 하나로, 웨이퍼에서 필요한 회로 패턴을 제외한 나머지 부분을 제거하는 과정

심화개념 |

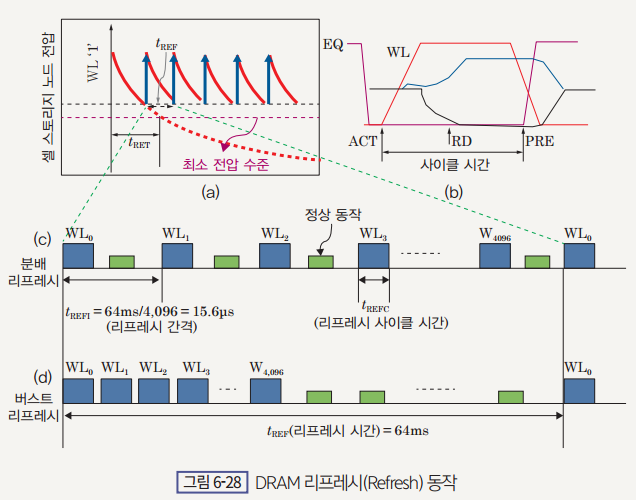

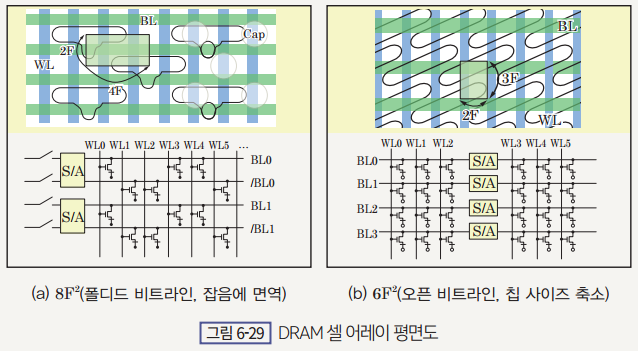

ⅱ) 리프레시(Refresh) 동작 원리 [그림 6-28(a)]와 같이, DRAM 메모리 셀에 논리 ‘1’을 쓴 후 일정 시간이 지나면, 셀에서 다양한 경로를 따라 누설 전류가 발생하여 셀 커패시터의 스토리지 노드(SN) 전압이 감소하게 된다. 이렇게 데이터를 쓴 시점부터 감지 증폭기(S/A)가 감지 가능한 최소 전압 수준까지 전압이 떨어지는 시간을 데이터 보존시간(Retention time, t RET)이라 한다. 이 시간이 경과하기 전에 주기적으로 해당 셀에 데이터를 다시 써 주는 리프레시(Refresh) 동작이 필요하다. 최근 DRAM의 데이터 보존시간은 고밀도, 고속 및 저전력의 필요성으로 인해, 더 긴 시간을 요구하게 되었다. 일반적으로 리프레시는 워드라인(WL) 단위로 동작하므로, 특정 워드라인(WL)을 ON시켜 그 워드라인(WL)에 달려 있는 전체 셀을 리프레시한 후 다른 모든 워드라인(WL)을 순차적으로 ON시켜 리프레시를 진행한다. 그 후 다시 동일한 워드라인(WL)을 리프레시하게 되는데, 이렇게 동일 워드라인(WL) 간 리프레시하는 시간 간격을 리프레시 시간(Refresh time, t REF)이라 정의한다. 따라서 데이터 보존시간(tRET)은 리프레시 시간(tREF)보다 반드시 커야 하고, 공정, 온도 및 셀 특성 등에 민감하게 의존하기 때문에 리프레시 시간(tREF)을 신중히 선택해야 한다. [그림 6-28(b)]와 같이, 리프레시 동작은 읽기(Read) 동작과 유사하다. 다만, 읽기 동작은 CSL을 ON시켜 읽은 데이터를 외부로 출력시키지만, 리프레시 동작은 외부로 출력시키지 않는다. 워드라인(WL)의 ON을 통해 그 안에 달려 있는 전체 셀의 데이터를 다시 쓰기(Re-store)만 하여 완료하는 것이다. 이렇게 한 개의 워드라인(WL)당 리프레시에 걸리는 시간을 리프레시 사이클 시간(Refresh cycle time, t REFC)이라 한다. 집적도가 높아짐에 따라 워드라인(WL)당 달리는 셀 수가 증가하므로, 리프레시 사이클 시간(tREFC)이 증가하게 된다. [그림 6-28(c)] 및 [그림 6-28(d)]처럼 리프레시 시간(tREF) 동안 모든 워드라인(WL)을 띄워 리프레시시켜야 하는데, 이때 리프레시 간격(Refresh interval, t REFI)은 모두 N개의 워드라인(WL)이 있는 경우에 리프레시 시간을 워드라인(WL) 개수로 나눈 시간(tREF/N)으로 정의된다. 따라서 리프레시 간격(tREFI)은 리프레시 시간(tREF)과 DRAM의 구조, 즉 DRAM을 몇 개의 워드라인(WL)으로 구성할 것인가에 의해 결정된다. [그림 6-28(c)]와 같이 리프레시 시간(tREF)이 64ms이고, 워드라인(WL) 수가 4K(4,096)개이면 리프레시 간격(tREFI)은 15.6μs가 된다. DRAM의 리프레시 방법은 다양하지만, 가장 기본이 되는 분배(Distributed) 리프레시([그림 6-28(c)] 참조)와 버스트(Burst) 리프레시([그림 6-28(d)] 참조), 2가지 방식을 간략히 설명한다. 버스트 리프레시는 모든 행(Row)이 순차적으로 접근(Access)될 때까지 일련의 리프레시 주기를 수행하되, 리프레시 동안 다른 명령어는 허용하지 않는다. 리프레시 동안 DRAM은 정상적인 동작을 수행할 수 없어 일시적으로 성능이 감소하고, 최대 전력 소모가 증가하는 문제가 생긴다. 반면, 분배(Distributed) 리프레시는 균일 간격으로 리프레시를 분산 실행하는 방법이다. 리프레시가 수행되지 않는 행(Row)은 외부 접속이 가능하므로 메모리 동작의 지연을 최소화할 수 있어 유리하다. (5) DRAM 셀 어레이 평면도(Layout) DRAM 셀 어레이의 구조는 크게 폴디드 비트라인(Folded BL) 구조와 오픈 비트라인(Open BL) 구조로 나눌 수 있다. [그림 6-29]에 두 가지 구조의 평면 구조를 나타내었으며, 앞 절의 DRAM 동작 원리는 폴디드 비트라인 구조를 기준으로 설명하였다. [그림 6-29(a)]의 폴디드 비트라인 구조는 BL과 /BL쌍이 하나의 셀 매트 내에 존재하도록 구성된다. 비트라인 쌍은 동일한 감지 증폭기(S/A)에 연결되며, 배치상 바로 인접하여 위치한다. 만약 폴디드 비트라인 구조에서 WL0과 BL0이 선택된다면, 메모리 셀은 하나만 선택되고, /BL0과 WL0에 연결된 메모리 셀은 존재하지 않으므로 /BL0와 /BL 간의 ΔVBL이 생성될 수 있다. 즉, BL과 /BL로 구성된 한 개의 행(Column) 내에서는 워드라인(WL)당 1개의 셀만이 연결되어야 하므로, [그림 6-29(a)]와 같은 평면도가 되는 것이다. [그림 6-29(b)]의 오픈 비트라인(Open BL) 구조의 경우, 워드라인(WL)과 BL이 교차하는 지점마다 모두 셀이 연결되어 있다. 그래서 같은 셀 어레이에 있는 BL과 /BL 쌍이 동일한 감지 증폭기(S/A)를 공유할 수 없게 된다. 오픈 비트라인 구조는 선택된 셀과 이웃한 셀 어레이의 BL이 쌍을 이뤄 동일한 감지 증폭기(S/A)에 연결되며, 두 BL 간의 전위차를 감지 증폭기(S/A)가 감지해 내는 구조이다. 예를 들어 좌측 셀 어레이의 WL0과 BL0이 선택되는 경우, 우측 셀 어레이에는 해당 BL에 선택된 셀이 없으므로 /BL0으로 되고, BL0과 /BL0이 쌍을 이루어 감지 증폭기(S/A)가 ΔVBL을 감지 및 증폭하게 된다. 폴디드 비트라인 구조는 BL과 /BL이 물리적으로 바로 옆에 위치하여, 제조 공정상 동일 형상으로 제작될 확률이 높아 잡음에 강한 장점이 있지만, 오픈 비트라인 구조에 비해 셀 면적이 거의 2배가량 커지는 단점이 있다. 반면 오픈 비트라인 구조는 셀 면적이 감소할 수 있다는 장점이 있지만, 서로 다른 셀 어레이의 BL, /BL 쌍을 비교한다는 점에서 잡음에 취약할 수 있다. 다음은 각 구조별 셀 평면도(Layout)에 대해 간략히 언급하고자 한다. 먼저, 최소 배선 폭(Minimum Feature Size, MFS, F)이라는 용어에 대한 정의가 필요한데, 이는 각 공정으로 구현 가능한 최소 패터닝 치수(Critical Dimension, CD)를 의미한다. 주로 워드라인(행) 또는 비트라인(열) 피치(Pitch)11의 절반 피치(Half pitch)로 정의된다. 폴디드 비트라인 구조는 BL 방향으로 4F(WL 4 half pitch), WL 방향으로 2F(BL 2 half pitch)가 되어, 셀 면적은 8F2가 된다. 두 셀이 동일한 활성층(Active)에 형성되고, BL이 형성되는 BL 콘택(BL Contact, BLC) 역시 두 셀이 공유하는 구조이다. 활성층 중앙부의 BL 콘택(BLC)이 형성될 부분이 돌출된 이유는 활성층의 양단 날개 부분에 형성될 SN 콘택(SN Contact, SNC)과 BL이 만나지 않게 하기 위함이다. 이에 반해 오픈 비트라인 구조의 셀 평면도는 BL과 SN 콘택(SNC)의 쇼트(Short)12를 방지하기 위해 활성층을 일정 각도 경사지게 하였고, 비어 있는 공간까지 활용할 수 있도록 WL과 BL이 만나는 지점마다 셀이 형성되는 레이아웃(Layout)이다. BL 방향으로 2F(WL2 half pitch), WL 방향으로 3F(BL 3 half pitch)가 되어, 셀 면적은 6F2이다. DRAM 제품의 미세화에 따라, 60nm 기술 노드(Node) 이하부터는 셀 효율(Cell efficiency) 향상을 위해 오픈 비트라인 구조와 6F2 셀이 적용되었다. 이론적으로는 8F2에서 6F2로 설계 레이아웃이 변경될 경우, 칩 사이즈가 약 25% 정도 줄어드는 효과가 생긴다. 다음 절에서 언급하겠지만, 가장 작은 셀 구조인 4F2 셀(WL, BL 방향 모두 2 half pitch)은 수직형 셀 트랜지스터(Vertical Channel Array Transistor, VCAT)를 갖는 셀로서, 상당 기간 업체별로 개발되어 왔으나 아직 상용화에 성공하지 못하였다. 이에 대해서는 다음 절에서 좀 더 상세하게 다루도록 하자. 피치(Pitch)11: 주기적으로 배열된 선들의 선폭과 선과 선 사이의 간격을 합친 값 쇼트12: 전기 회로의 두 점 사이의 절연(絶緣)이 잘 되지 않아 두 점 사이가 접속되는 현상. 합선과 유의어 |

심화개념 |

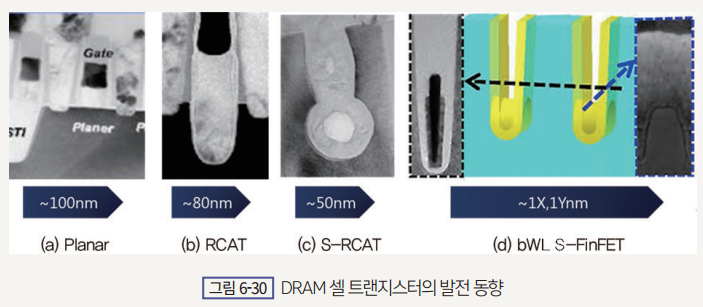

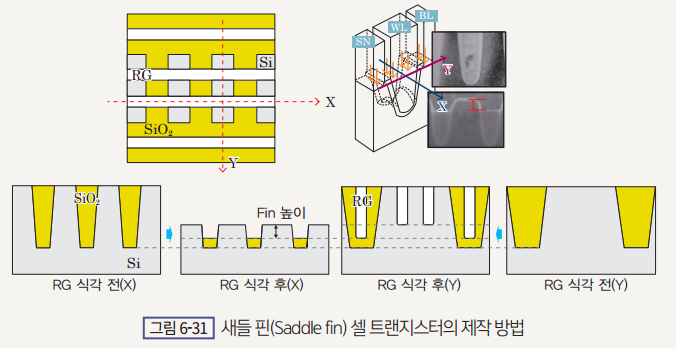

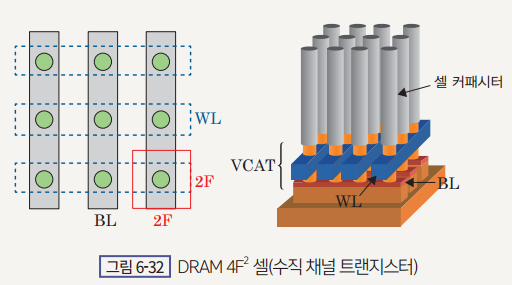

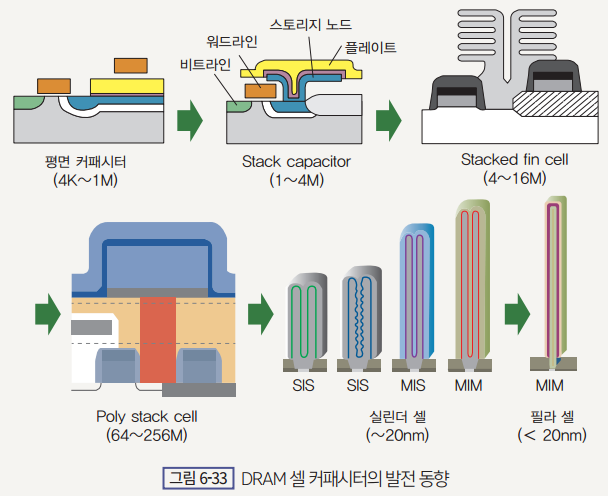

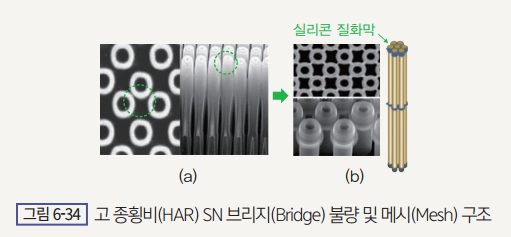

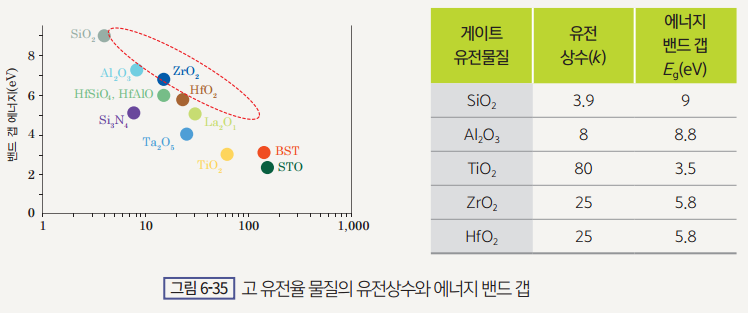

(6) DRAM의 미세화(Scaling) 동향 DRAM 제조 업체들은 지속적으로 다음 단계의 미세화(Scaling)를 추진하고 있지만, 메모리 기술이 물리적 한계에 근접함에 따라 몇 가지 문제에 직면하고 있다. 현재 첨단 DRAM 제품은 15~18nm공정을 기반으로 하고 있으며, DRAM의 물리적 한계라고 알려져 있는 10nm 세대의 제품 양산화를 위해 연구개발을 진행 중에 있다. 궁극적으로 새로운 메모리(New memory)로 대체하려는 노력을 상당기간 하고 있으나, 아직까지 완전 교체에는 이르지 못하고 있다. 하지만 시스템 제조 업체들은 5G 및 인공지능과 같은 새로운 데이터 집약적 애플리케이션을 위해, 계속해서 더 큰 대역폭13과 더 빠른 DRAM을 원하고 있는 상황이다. 이에 맞춰 DRAM 공급 업체는 DDR514 및 HBM(High-Bandwidth Memory, 고 대역폭 메모리) 등과 같은 새롭고 더 빠른 대역폭의 제품으로 대응하고 있다. 그러나 DRAM 기술 난이도의 증가로 인해, 업체들의 DRAM 스케일링이 느려져 이전의 스케일링 속도를 따라가지 못하고 있다. 따라서 이번 절에서는 DRAM 셀의 주요 구성 요소인 셀 트랜지스터와 셀 커패시터의 동향(Trend) 및 미세화(Scaling)의 문제점들에 대해 알아보도록 하자. 대역폭13: 여러 가지 다른 주파수의 성분이 분포되어 있는 주파수 범위의 폭 DDR514: Double Data Rate 5 메모리 ① 셀 트랜지스터 셀 트랜지스터는 전술한 바와 같이 DRAM의 셀 커패시터와 비트라인(BL) 사이에서 스위치 역할을 하는 nMOS이다. DRAM 제품의 최소 선폭15이 100nm 이하로 축소됨에 따라 [그림 6-30(a)]와 같은 기존의 평면 트랜지스터(Planar Cell Array Transistor, PCAT)는 단 채널 효과(SCE)에 의한 OFF 상태 누설 전류가 발생하게 된다. 이러한 누설 전류의 억제를 위해 채널 도핑을 증가시키면, 반대급부로 셀 커패시터의 스토리지 노드(SN)와 접하는 PN 접합부의 전계가 증가하고 접합 누설 전류도 증가하여 전하 보존(Retention) 특성이 악화된다. 이러한 DRAM 셀 트랜지스터의 단 채널 효과(SCE)를 개선하기 위해, [그림 6-30(b)]의 함몰형 채널 어레이 트랜지스터(Recess Channel Array Transistor, RCAT)라는 혁신적인 소자가 도입되었고, 이를 시작으로 다양한 3차원 셀 트랜지스터가 개발 및 생산되었다. 최소 선폭15: 반도체 칩에 사용되는 회로 선폭의 최솟값 RCAT은 채널이 형성될 부분의 실리콘을 적정 깊이로 식각한 함몰 게이트(Recess gate) 구조를 가진다. 이 구조 덕분에 채널 길이를 증가시켜 채널 도핑을 감소시킬 수 있으므로, 평면 트랜지스터(PCAT)에서 문제되었던 단 채널 효과(SCE) 및 전하 보존 특성 문제를 해결할 수 있다. 그러나 DRAM기술이 80nm 이하로 축소됨에 따라 RCAT의 하단 바닥 곡률이 뾰족해지면서, 문턱 전압과 기판 효과(Body effect)의 증가, 문턱 전압 이하 스윙(Sub-threshold Swing, SS) 및 DIBL 특성 악화 등 한계에 달하게 되었다. 이를 개선하기 위해 나온 것이 [그림 6-30(c)]의 S-RCAT(Spherical-Recess Channel Array Transistor)이다. 이 구조는 두 단계의 식각 공정을 통해 함몰 채널의 하단부를 구 형태(Spherical)로 만들었고, RCAT에서 문제되었던 채널 하단부 곡률 반경을 증가시킴으로써 문턱 전압을 포함한 RCAT의 문제점을 상당 부분 해결할 수 있었다. 이 구조는 40~50nm 기술 노드까지 적용되었으나, 40nm 이하로 축소되면서 S-RCAT의 직선 부분과 구형 함몰 부분이 만나는 목(Neck) 부분에 전계가 집중되는 문제가 생겼다. 이는 전하 보존 특성의 악화를 비롯한 다양한 신뢰성 열화를 초래하였고, 구동 전류 부족 문제도 대두되었다. 이러한 S-RCAT의 문제를 해결하고자 등장한 구조가 [그림 6-30(d)]의 새들 핀(Saddle Fin, S-Fin)이다. S-Fin은 RCAT의 채널 하단에 핀(Fin) 구조를 형성하고, 게이트가 이 핀 형태의 채널을 감싸는 3차원 트랜지스터 구조이다. 일반적인 로직용 FinFET과 달리 말의 안장 모습을 하고 있다고 하여 Saddle(안장)이라 불린다. 이 구조는 채널 3면을 게이트로 제어하기 때문에 게이트 제어 능력이 향상되어 단 채널 효과(SCE)를 개선했고, 핀의 높이만큼 채널 폭(Width)이 증가하여 전류 구동 능력도 향상시킬 수 있었다. 현재는 30nm 이하 DRAM 셀 트랜지스터에 적용 중이다. 한편 [그림 6-31]에 제시한 S-Fin 구조의 제작 과정을 보면, 활성(Active) 영역과 필드(Field) 영역에 함몰 채널을 만드는 것은 일반적인 RCAT 제작 과정과 같으나, 필드 쪽의 산화막을 일정량 추가 식각하여 핀 구조를 형성하는 차이점이 있다. S-Fin 구조는 문턱 전압(VTh)이 핀 폭과 높이에 민감하기 때문에 안정적인 특성 확보를 위해 핀 치수를 균일하게 유지하는 것이 중요하다. S-Fin의 등장 이후로는, S-Fin과 비슷한 시점에 개발된 매몰 워드라인(Buried Wordline(bWL)) 기술도 함께 사용되어, [그림 6-30(d)]와 같은 bWL S-FinFET 형태가 생겨나게 되었다. 이 bWL은 기판 표면 아래로 워드라인을 매몰시켜 비트라인과 워드라인 사이의 기생 정전용량(CB)을 감소시켰고, 감지 여유도(Sensing margin)를 대폭 개선하여 궁극적으로 전력 소비를 낮출 수 있는 구조이다. bWL은 TiN/W와 같은 금속 게이트를 사용하여 워드라인의 저항을 감소시킬 뿐만 아니라, 높은 일 함수(Work function)로 인한 문턱 전압의 상승으로 채널 도핑을 더 낮게 가져갈 수 있어 데이터 보존 특성을 향상시킬 수 있다. 또한 다결정 실리콘에서의 게이트 공핍이 없어 문턱 전압 분포의 개선 효과도 얻을 수 있는, 다양한 장점을 가진 기술이다. bWL S-Fin 이후로도, [그림 6-32]와 같은 4F2 셀에 사용되는 수직 채널 트랜지스터(Vertical Channel Array Transistor, VCAT) 구조 등의 후보들이 등장하고 있으나, 부유 몸체 효과(Floating body effect)와 비트라인(또는 워드라인)끼리의 정전용량 결합(Capacitive coupling), 공정상의 어려움 등으로 난항을 겪고 있다. 이로써 DRAM을 대체할 신규 메모리의 상용화에 일정 시간이 필요할 것으로 보이므로, 당분간은 현재의 bWL S-Fin 구조의 개선을 통한 미세화가 계속될 것으로 전망된다. ② 셀 커패시터 앞서 설명했듯이, DRAM 셀 커패시터는 2개의 전극과 그 사이에 삽입된 유전체(Insulator)로 구성되어 있으며, 셀 트렌지스터의 접합부와 연결되는 하부 전극을 스토리지 노드(SN), 다른 한쪽의 상부 전극을 셀 플레이트(CP)라고 한다. DRAM은 셀 커패시터를 충·방전시킴으로써 데이터를 저장(Write)하고 읽어(Read)낸다. 따라서 데이터를 안정적으로 저장하고 감지하려면 최소 정전용량이 필요하다. 셀 커패시터의 최소 정전용량은 과거 20~25fF/Cell 정도였으나, 점차 감소하여 최근 ~10fF/Cell수준까지 내려가게 되었다. 이는 감지 증폭기 및 관련 구동 회로의 최적화 덕분에 가능해진 것이다. 셀 커패시터의 정전용량은 다음 식을 통해 구할 수 있으며, 정전용량을 증가시키기 위해서는 절연체 박막 두께(d)의 감소나 커패시터 유효 표면적(A)의 증가, 또는 고 유전율(k)의 물질을 사용해야 한다. (ε0: 진공에서의 유전율(8.854 × 10-12F/m), k: 유전체의 유전상수, A: 커패시터의 면적, d: 필름 두께) DRAM의 미세화에 따라 커패시터의 크기 축소가 요구됐지만, 이는 곧 정전용량의 감소를 동반하므로 다른 방안이 필요하게 되었다. 그래서 [그림 6-33]과 같이 2차원 평면 구조에서 평면적은 줄이되, 수직 치수(Vertical dimension)를 증가시켜 3차원적으로 면적을 늘려 왔다. 3차원 커패시터 전극의 형상에는 실린더(Cylinder)와 필라(Pillar, 기둥) 형태가 있다. 실린더 방식은 높이에 비해 전극의 면적을 크게 확보할 수 있지만, 공정이 복잡하고 공간이 좁아 구현이 어렵다. 이에 비해 필라 형태는 모양이 단순하지만, 최소 정전용량을 확보하기 위해 실린더 대비 기둥의 높이를 증가시켜야 한다. 이로 인해 고 종횡비(High Aspect Ratio, HAR) 구조(16nm 기술 노드에서 정전용량(CS) 10fF/Cell 기준으로 했을 때 ~100 수준)가 되어, 증착 및 식각 공정의 난이도가 상승하는 문제를 초래한다. 이러한 문제에 대해 기둥을 두 단계로 분리해 형성함으로써 종횡비를 완화시키는 방법이 있으나, 이 또한 반대급부로 공정 수의 증가 및 고도의 공정 정밀도 제어를 요구한다. 높이의 증가는 기계적 한계에도 직면하게 되는데, [그림 6-34(a)]처럼 고 종횡비(HAR)의 스토리지 노드(SN)끼리 서로 들러붙는 브리지(Bridge) 불량이 일어날 수 있다. 이러한 불량을 방지하기 위해 스토리지 노드(SN)를 [그림 6-34(b)]와 같이 실리콘 질화물(SiN) 그물(Net)로 서로 엮는 메시(Mesh) 구조가 제안되었다. 구조적 변화와 함께 스토리지 노드(SN)와 셀 플레이트(CP) 전극의 물질도 변화되었다. 다결정 실리콘에서 금속으로 변경된 이유는, High-k 유전체 막의 결정화를 위해 산소 분위기에서 열 처리가 이루어질 때, 스토리지 노드(SN) Poly-Si의 계면에 유전율이 낮은 SiO2층이 형성되고, 이로 인해 등가 산화막 두께(EOT)가 증가는 문제를 방지하기 위해서이다. 이때 금속 물질로는 주로 티타늄 질화물(TiN) 또는 루테늄(Ru) 등이 사용된다. 마지막으로 고 유전율 물질의 적용에 대해 설명한다. 기존에 사용하던 실리콘 산화막 페로브스카이트16: ABX3 화학식(A, B는 양이온, X는 음이온)을 갖는 결정 구조로, 절연체·반도체·전도체의 성질은 물론 초전도 현상까지 보이는 특별한 구조의 금속 산화물 |

4 낸드 플래시 메모리

낸드 플래시 메모리는 DRAM 대비 동작 속도는 느리지만, 고용량, 저비용의 장점을 살려 대부분의 디지털 기기(USB 메모리, 스마트폰, 태블릿 PC, SSD 등)에 적용되는 메모리 소자이다. 전원을 끄더라도 저장된 데이터를 유지할 수 있는 비휘발성 저장 특성을 가지며, 전류 구동 능력이 좋은 nMOS로 되어 있다. 현재는 기존의 2차원 부유 게이트 셀(Floating Gate Cell, FG)의 미세화 어려움 때문에 전하 포획 플래시(Charge Trap Flash) 및 3차원 낸드 플래시 구조로 변경되어 개선 및 발전 중에 있다. 이에 대해서는 후에 다시 설명하도록 하겠다.

(1) 부유 게이트(Floating Gate) 낸드 플래시(NAND Flash) 메모리

① 기본 구조

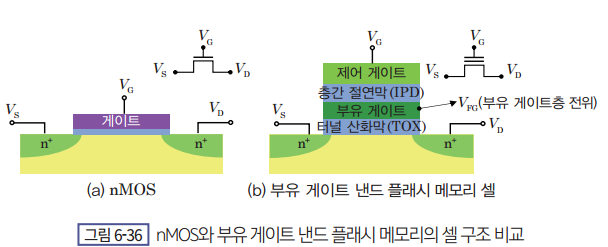

[그림 6-36]에 nMOS와 부유 게이트(FG) 낸드 플래시 메모리의 셀 구조를 나타내었다. 부유 게이트(FG) 낸드 플래시에 부유 게이트(Floating gate)와 층간 절연막(Inter Poly Dielectric, IPD)이라는 절연체가 존재한다는 것을 제외하면, 두 가지 모두 동일한 트랜지스터 동작을 하는 nMOS 소자이다. 부유 게이트(FG) 낸드 플래시의 기호는 [그림 6-36]의 오른쪽 상단에 나타낸 것과 같으며, nMOS 게이트에 선을 하나 더 추가한 모습이다. 각 구성 요소들의 기능은 다음과 같다.

제어 게이트(Control Gate, CG): 셀을 선택하는 워드라인(Wordline)으로, 페이지 단위의 셀들이 워드라인에 연결되어 있다. 기존 n+ 다결정 실리콘에서 WSi, CoSi(또는 NiSi)을 거쳐, 최근에는 매립(Gap fill) 성능이 우수한 W 또는 Co 금속 게이트로 발전하였다.

부유 게이트(Floating Gate, FG): 데이터(전자)를 저장하는 기능을 하며 n+ 다결정 실리콘 물질로 구성되어 있다. 전체가 유전체로 둘러싸여 셀 단위로 격리되어 있으므로, 전원이 꺼지더라도 저장된 데이터를 유지할 수 있는 비휘발성 메모리의 특성을 갖는다.

층간 절연막(Inter Poly Dielectric, IPD): 부유 게이트(FG) 내 전자가 제어 게이트로 이탈되는 것을 방지하는 절연막이다. 통상 ONO(산화막-질화막-산화막) 구조로 되어 있다.

터널 산화막(Tunnel Oxide, TOX): 셀의 쓰기(Program) 또는 소거(Erase) 동작 시에 전자가 통과(Tunneling)하는 산화막이다.

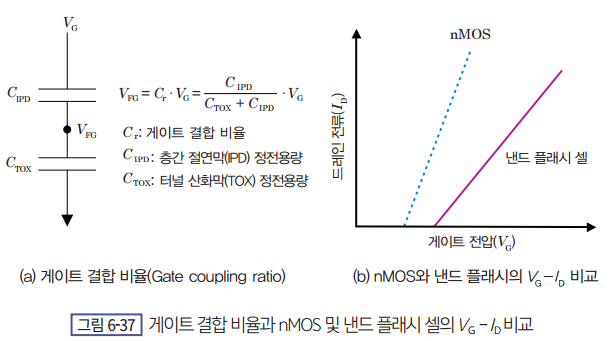

부유 게이트(FG) 낸드 플래시는 외부로부터 제어 게이트에 전압(VG)이 인가되지만, 실제 트랜지스터 동작은 셀 내부의 부유 게이트 전위(VFG)의 영향을 받는다. 부유 게이트 전위(VFG)는 층간 절연막(CIPD)과 터널 산화막(CTOX) 간 결합 정전용량(Coupling capacitance)에 의해 결정된다. 즉, 층간 절연막(IPD)에 의해 외부에서 걸어 준 전압(VG)의 일정량만 부유 게이트(VFG)에 인가된다는 것이다.

(Cr: 게이트 결합 비율, VG: 외부에서 인가된 전압)

[그림 6-37(b)]와 같이, 같은 크기의 일반적인 nMOS와 낸드 플래시 셀에서의 게이트 전압 대비 드레인 전류(VG - ID)의 특성을 비교해 보면, 동일 게이트 전압에서 낸드 플래시의 드레인 전류 감소 현상이 발생한다. 이는 게이트 결합 비율(Cr)만큼의 문턱 전압 증가 및 ID - VG의 기울기 감소에서 기인한 것이다. 따라서 동일 게이트 전압(VG)으로 더 높은 플로팅 게이트 전압(VFG)을 가져가기 위해서는 게이트 결합 비율(Cr)의 증가, 즉 층간 절연막 유전상수(CIPD)를 크게 해 주어야 한다. 이를 위해서는 층간 절연막(IPD)을 통한 누설 전류를 최소화하면서 유전상수를 증가시켜야 한다. 이러한 이유 때문에, 통상 층간 절연막(IPD)은 ‘실리콘 산화막-실리콘 질화막-실리콘 산화막’의 ONO(Oxide-Nitride-Oxide) 구조를 사용한다. 이외에 부유 게이트와 제어 게이트 간 중첩 면적도 확보하여야 한다.

② 동작 원리

낸드 플래시의 동작은 부유 게이트에 전자를 집어 넣는 프로그램(Program) 동작과 부유 게이트로부터 전자를 제거하는 소거(Erase) 동작, 그리고 부유게이트 내 전자의 유무에 따라 데이터를 읽어내는 읽기(Read) 동작으로 나눌 수 있다. 프로그램과 소거 동작은 전자를 p형 기판에서 부유 게이트로, 또는 그 반대 방향으로 전자를 이동시키는 파울러-노드하임 터널링(Fowler-Nordheim Tunneling, FN 터널링) 현상을 이용하게 된다. 이에 대해서는 MOSFET 단원을 참조하기 바란다.

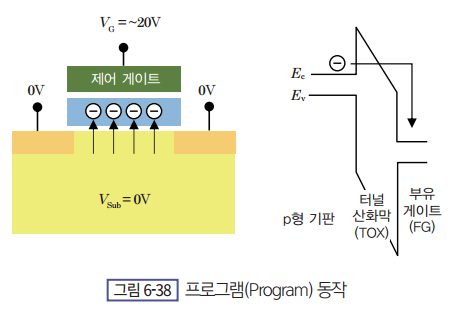

ⅰ) 프로그램(Program) 동작

프로그램 동작은 [그림 6-38]과 같이 소스, 드레인 및 기판을 모두 접지(0V)한 상태에서, 제어 게이트(VG)에 높은 양의 전압(~20V)을 인가함으로써 이루어진다. 이렇게 되면 p형 기판에 있던 전자가 FN 터널링을 하게 되고, 터널 산화막을 통과해 부유 게이트로 이동하게 된다. 이 때문에 전기가 끊기더라도 부유 게이트 내에 전자(데이터)가 남아 비휘발성 메모리로 동작하게 된다.

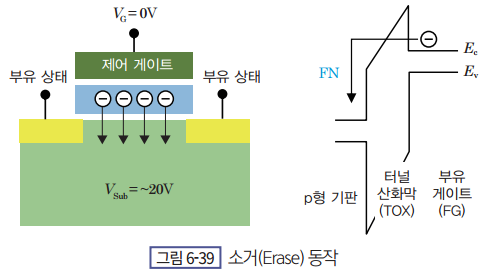

ⅱ) 소거(Erase) 동작

소거 동작은 [그림 6-39]와 같이 프로그램 동작과는 반대로, 제어 게이트를 접지(0V)한 상태에서 p형 기판에 고전압(~20V)을 인가하여 이루어진다. 마찬가지로 FN 터널링 현상을 이용해 부유 게이트 내의 전자를 p형 기판으로 이동시킴으로써, 부유 게이트 내에 있는 전자를 소거시킨다. 이때 소스와 드레인은 부유 상태(Floating)로 둔다. 낸드 플래시의 ‘플래시(Flash)’라는 용어도 바로 이 소거 동작에서 비롯된 것이며, 메모리 셀들을 한 번의 동작으로 섬광(Flash)처럼 지울 수 있다는 데서 유래하였다. 프로그램 동작과의 차이점은 셀 어레이(Array) 내의 블록(Block) 단위로 이루어져 게이트 영역만 충전시키면 되었던 프로그램 동작에 비해, 소거 동작은 상대적으로 넓은 영역을 충전시켜야 한다는 점이다. 또 프로그램 시 p형 기판에서 제공되는 많은 수의 전자를 부유 게이트에 밀어 넣을 수 있었던 것과 다르게, 소수의 전자를 모두 빼내야 하기 때문에 프로그램 속도(~μs) 대비 매우 느리다(~ms).

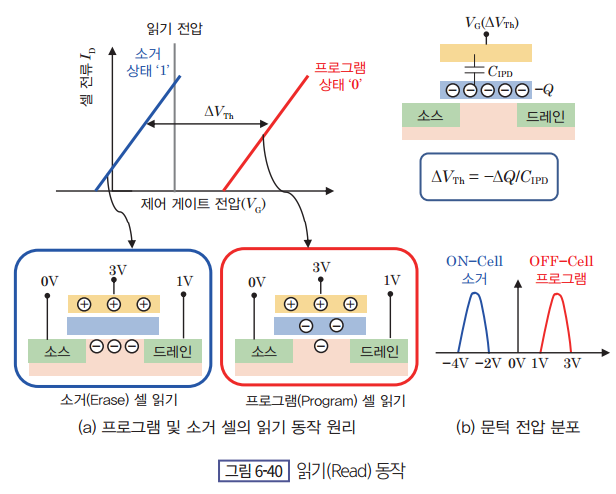

ⅲ) 읽기(Read) 동작

읽기(Read) 동작은 프로그램과 소거 동작으로 인한 부유 게이트 내 전자 수의 변동에 의해 발생한 트랜지스터의 문턱 전압 차이만 감지하면 되므로, 프로그램 및 소거 동작 시와 같이 제어 게이트에 높은 전압을 인가할 필요가 없다. 따라서 프로그램과 소거 동작으로 인해 부유 게이트에 저장된 전하량의 차이를 제어 게이트와 부유 게이트 사이 유전체의 정전용량(CIPD)으로 나눠주면 문턱 전압의 차이를 구할 수 있다(ΔVTh = -ΔQ/CIPD). 즉, 문턱 전압이란 반전층을 형성할 수 있는 개수만큼의 전자를 유기하기 위해 게이트에 가하는 전압이므로, [그림 6-40(a)]와 같이 프로그램 상태에서는 이미 부유 게이트에 전자가 채워져 있어, 전자가 없을 때와 동일한 전압을 인가할 경우 부유 게이트 내의 전자 수를 제외한 만큼의 전자만이 채널에 유기된다. 그러므로 채널의 반전을 위해서는 더 높은 전압을 인가해야 하고, 이는 문턱 전압의 증가를 의미한다. 소거 상태의 셀은 부유 게이트에 전자가 없으므로 반대 원리로 문턱 전압이 감소한다. 이에 따라 프로그램과 소거 상태의 문턱 전압의 중간 수준에 해당하는 적절한 읽기 전압(Read voltage)을 게이트에 인가하면, 프로그램 상태의 셀은 전류 흐름이 없는 프로그램 상태(‘0’)가 되고, 소거 상태의 셀은 문턱 전압이 감소하여 읽기 전압 인가 시 전류가 흐르는 소거 상태(‘1’)가 된다. 이와 같은 문턱 전압의 변동은 제작 공정상의 차이가 아닌 부유 게이트의 전위차로 인해 발생하는 것이므로, [그림 6-40(a)] 상단의 게이트 전압-셀 전류 그래프상 직선의 기울기에는 변화가 없고 문턱 전압의 변동만 보이게 된다. 프로그램 및 소거 동작 후 전체 메모리 셀의 문턱 전압 분포를 그려보면 [그림 6-40(b)]와 같은 분포를 가지게 되며 분포의 변동 폭이 작을수록 좋은 셀 특성을 보인다고 말할 수 있다.

③ 부유 게이트 낸드 플래시의 문제점

부유 게이트 낸드 플래시는 십수 년에 걸쳐 120nm에서 1Xnm까지 축소되어 생산성이 개선되었으나, 더 이상의 미세화(Scale-down)는 넘기 어려운 장벽에 직면하게 되었다. 이를 공정적 문제와 소자적 문제로 나누어 설명한다.

▣ 공정적 문제

ⅰ) 포토 공정 장비의 한계

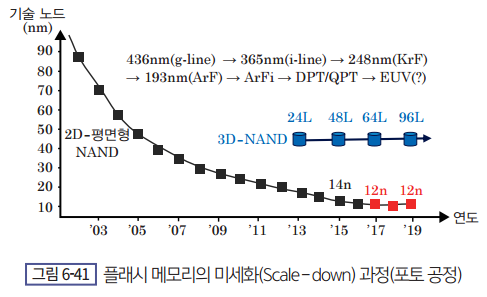

[그림 6-41]과 같이 1Xnm급 제품에 적용되는 ArF 액침 노광(ArF Immersion)과 다중 패터닝(Multi patterning) 기술은 비용 및 기술 측면에서 이미 한계에 와 있는 상태이다. 극자외선(EUV) 노광 기술 역시 아직 미성숙 기술이며, 낸드 플래시와 같은 저가 메모리 제품에 사용하기에는 투자 효율성 측면에서 문제가 있다.

ⅱ) 워드라인 및 비트라인 배선 저항 및 배선 간 정전용량 증가

소자 미세화에 의한 라인의 선폭 및 라인 간 간격 감소에 의해 저항 및 정전용량이 증가하였고, 이에 따른 RC 지연17 감소를 위해 저저항 및 저 유전율 물질을 적용 중에 있으나 현재 한계에 봉착하였다.

워드라인 물질의 변화: Poly Si →WSi → CoSi(or NiSi) → W

비트라인 물질의 변화: W → Al → Cu

Space 영역 매립 물질의 변화: Nitride → Oxide → Air-Gap(에어 갭)

RC 지연17: 회로의 속도를 의미하며, 회로를 구성하는 저항(R)과 정전용량(C)의 곱으로 표현함.

ⅲ) 수평 방향 축소 대비 수직 방향 축소의 어려움으로 발생되는 공정 문제

수직 방향 축소는 다음과 같은 이유로 수평 방향 축소 못지 않게 난이도가 높다.

터널 산화막(TOX) 및 층간 절연막(IPD)의 두께: 부유 게이트 내 저장된 전자의 유출 방지로 인해 두께 감소가 어려움.

부유 게이트의 두께: 결합 정전용량(Cr)의 보존을 위해 제어 게이트와 부유 게이트 간 중첩 면적(Overlap area)의 확보가 필요하여 두께 감소가 어려움.

이러한 수직 방향 축소의 어려움으로 인해, 전기적으로는 동작 전압 축소(Scaling)가 어려워졌고, 고 종횡비의 게이트 적층 구조로 인해 세정 공정18 등에서 발생되는 패턴의 붕괴(Collapse)또는 휨(Bending) 현상도 문제시되었다. 이에, 고 종횡비 패턴 사이의 골을 채울 수 있는 좋은 매립 특성을 지닌 다결정 실리콘 및 금속 요소 공정 기술의 개발이 필요하게 되었다.

세정 공정18: 웨이퍼 표면의 파티클(Particle)을 비롯한, 가능한 모든 불순물을 물리·화학적 방법으로 제거하는 공정

▣ 소자적 문제

ⅰ) 부유 게이트 내 전자 수의 감소

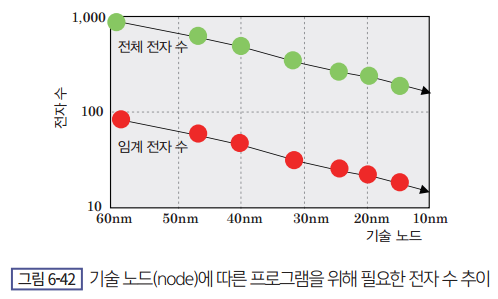

[그림 6-42]와 같이, 소자의 미세화에 따른 부유 게이트와 제어 게이트 사이의 정전용량 감소는 임계 전자 수를 급격히 감소시켜 문턱 전압 변동의 문제를 일으킬 수 있다. 이는 정전용량이 감소함에 따라 부유 게이트에 저장되는 전하량(Q)도 감소하기 때문이다.

예를 들어, 부유 게이트에 100개의 전자를 저장할 수 있다고 했을 때, 1개의 전자를 잃게 되더라도 1/100만큼의 매우 작은 문턱 전압(VTh) 손실만 발생한다. 하지만 부유 게이트에 10개의 전자를 저장 가능한 경우에는 1개의 전자를 잃으면, 1/10만큼의 매우 큰 문턱 전압 손실이 발생하게 된다. 이에 따라 전하 보존 능력(Retention)과 같은 신뢰성 불량을 유발함은 물론, 후술할 다중 전하 저장 셀 특성, 즉 MLC(Multi Layer Cell), TLC(Triple Layer Cell) 등의 제품 특성에도 악영향을 주게 된다.

ⅱ) 이웃한 셀(Cell) 간 누설 전류

앞서 설명한 수직 방향 축소의 어려움으로 인해 절연막의 두께 감소가 이루어지지 않으면, 프로그램 전압의 감소도 어려워진다. 따라서 수평 방향 축소에 따른 워드라인 간격의 감소에 따라 제어 게이트 간 또는 부유 게이트 간 누설 전류, 그리고 항복(Breakdown) 문제가 발생한다. 이에 대한 해결책으로 워드라인 및 소자 격리(STI) 사이의 절연막 일부를 실리콘 산화막 대신 빈 공간(Air gap, 에어 갭)으로 형성하여 누설 전류 경로를 차단해 개선하는 방법이 있다. 이는 다음 항에서 설명할 인접 워드라인 간의 정전용량 결합(Capacitive coupling)에 의한 간섭 현상을 개선하는 데도 적용된다. 그러나 이 기술 또한 그 이상의 미세화가 진행될 시에는 대안이 없는 것이 문제이다.

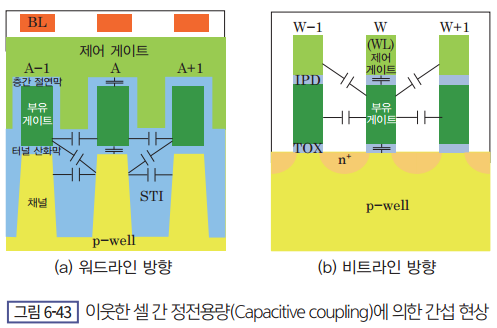

ⅲ) 읽기(Read) 동작 시 판별 셀 간의 좁은 간격

[그림 6-43]과 같이 수평 방향 축소가 진행됨에 따라 선택 셀과 이웃한 제어 및 부유 게이트 간 간격이 감소하게 된다. 이로써 정전결합(Coupling capacitance)에 의한 프로그램 문턱 전압 자체와, 분포의 변동과 같은 간섭 현상(Interference)을 야기하게 되는데, 이러한 간섭 현상을 상호 혼선(Cross-talk)이라고 한다. 이를 감소시키는 방안에는, 먼저 공정·소자적으로 부유 게이트 간 간격을 확보하는 공정의 개발과 에어 갭(Air-gap) 등 저 유전율 물질의 적용, 그리고 부유 게이트 두께의 감소 등을 들 수 있다. 소프트웨어적으로는 이웃 셀의 문턱 전압 변동에 영향을 주는 이웃 셀 수의 감소 등 다양한 알고리즘적인 대책이 있다.

이러한 부유 게이트의 공정, 소자적 문제에 대한 다양한 대책에도 불구하고, 10nm 이하 부유 게이트 낸드 플래시 구조의 연장은 이미 한계치에 도달한 상태였다. 그래서 대부분의 낸드 플래시 업체들은 그 대책으로 전하 포획(Charge trap) 셀을 기반으로 하는 3차원 낸드 셀(3D NAND Cell) 구조로 전환하게 된 것이다.

심화개념 |

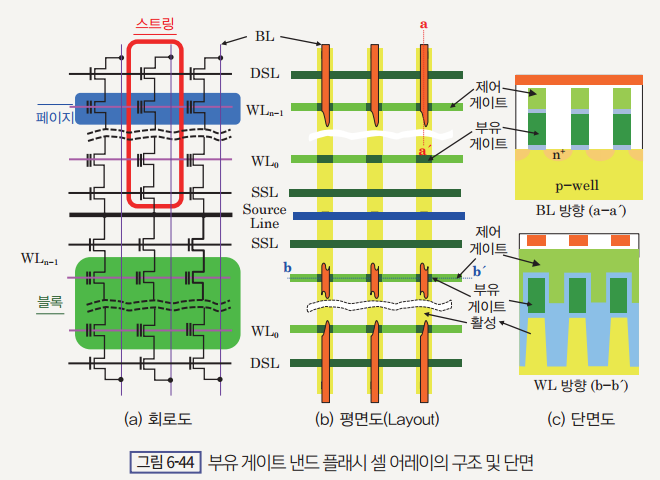

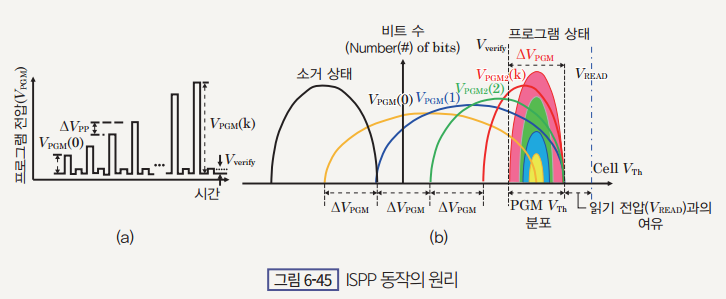

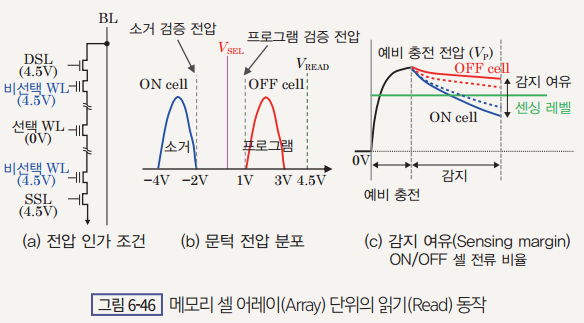

(2) 낸드 플래시 메모리 셀 어레이(Array)와 어레이에서의 동작 원리 ① 셀 어레이(Cell array) 구조 낸드 플래시 셀의 어레이는 [그림 6-44]와 같이 횡(Column) 방향으로는 하나의 제어 게이트(워드라인)에 달려 있는 셀들의 집합인 페이지(Page)로 구성되어 있고, 종(Row) 방향으로는 DSL(Drain Select)트랜지스터와 SSL(Source Select) 트랜지스터 및 셀들이 직렬로 연결되어 있는 스트링(String)으로 구성되어 있다. 한 페이지에 달려 있는 셀 수(비트라인 수)와 한 스트링에 달려있는 셀 수(워드라인 수)를 곱하면 블록(Block) 단위의 셀 수가 결정된다. DSL 트랜지스터는 모든 블록을 공유하는 비트라인을 특정 선택 스트링과 연결시켜주는 스위치이며, SSL 트랜지스터는 해당 스트링을 접지에 연결되어 있는 소스 라인과 연결시켜주는 스위치이다. 이때, 프로그램(Program) 동작은 워드라인에 전압을 인가하여 행해지므로, 프로그램의 최소 단위는 페이지이고, 읽기(Read) 동작은 셀의 데이터를 스트링을 통해 판별하므로, 최소 단위는 스트링이 된다. 또한 블록은 소거(Erase)의 기본 단위이다. 이렇게 블록을 구분하는 이유에는 소거 동작을 블록 단위로 빠르게 하기 위한 목적과 함께, 소거를 하지 않아야 할 블록과는 전기적·물리적으로 격리하기 위한 목적이 있다. 한편, 낸드 플래시의 페이지는 실제 데이터가 저장되는 데이터 어레이(Data array)와 ECC(Error Check Correction)19 등이 저장되어 있는 스페어 어레이(Spare array)로 구성되어 있다. [그림 6-44(c)]의 비트라인과 워드라인 방향으로의 단면 구조를 통해, 부유 게이트(FG)의 모든 면이 절연체로 격리되어 있음을 알 수 있다. ECC(Error Check Correction)19: 읽기 동작 시 불량 셀이 발생하면 먼저 처리하는 역할을 함. ② 셀의 문턱 전압 분포 개선 프로그램 방법(ISPP) 다양한 공정상의 불균일 문제로 인해, 각 셀들은 동일한 프로그램 제어 게이트 전압에 대해서도 다양한 문턱 전압 분포를 보인다. 이렇게 프로그램 문턱 전압 분포가 넓어지면, 후술할 MLC(Multi Level Cell)나 TLC(Triple Level Cell)에 있어 읽기 판정 불량을 일으키고, 다양한 신뢰성 문제를 야기하게 된다. 따라서 프로그램 시 이러한 문턱 전압의 분포를 최소화할 수 있는 방법이 필요한데, ISPP(Incremental Step Pulse Programming) 방법을 통해 이를 해소할 수 있다 프로그램 시 높은 전압을 한 번에 인가하여 진행하게 되면, 문턱 전압 분포가 매우 커질 우려가 있다. 따라서 [그림 6-45(a)]와 같이 게이트 전압을 점진적으로 올리면서 매 상승 때마다 셀의 문턱 전압을 확인(Verify)하는 과정이 필요하다. 이때 목표로 하는 문턱 전압에 도달한 셀은 프로그램을 중단(Inhibit)시키고, 아직 목표 문턱 전압에 도달하지 못한 셀에 대해서는 인가하는 전압을 조금 더 증가시킨다. 이로써 결과적으로는 문턱 전압 분포를 최소화하면서 목표한 문턱 전압에 도달할 수 있게 되는 것이다. [그림 6-45(b)]와 같이 ISPP 동안 문턱 전압 분포는 소거 상태에서 프로그램된 상태로 이동한다. 첫 번째 프로그램 펄스(VPGM(0))에서 가장 빠른 셀은 충분히 프로그램되어 확인한 문턱 전압(Vverify)보다 문턱 전압이 더 높지만, 가장 느린 셀은 Vverify보다 문턱 전압이 낮다. 다음 번 인가한 조금 더 높은 프로그램 펄스(ΔVPGM)는 셀 임계 전압 분포를 프로그램 상태로 더 이동시키고, 셀 임계 전압이 Vverify + ΔVPGM의 범위에 분포되면 프로그램 동작이 완료된다. 따라서 프로그램 펄스(ΔVPGM) 범위가 좁을수록, 즉 펄스 인가 및 확인 루프(Loop) 횟수가 많을수록 분포는 더 양호해진다. 하지만 그만큼 프로그램 시간이 더 길어진다는 트레이드 오프(Trade-off) 관계가 성립되어, 목적에 맞게 적절히 사용해야 한다. ③ 셀 어레이에서의 읽기(Read) 동작 셀 어레이에서의 읽기 동작은 다음과 같은 과정으로 진행된다. ⅰ) 읽고자 하는 셀의 비트라인(BL)에 예비 충전(Pre-Charge) 전압을 인가 ⅱ) 읽기 동작 직전, 예비 충전 전압의 인가 중지 → 비트라인 부유 상태(Floating)가 됨. ⅲ) 읽고자 하는 셀(선택 셀)의 워드라인에 읽기 전압(VSEL) ~0V 인가 ⅳ) 나머지 비선택 셀의 워드라인에는 프로그램된 셀도 ON 상태가 될 수 있는 고전압(VREAD, ~4.5V)을 인가(단, 프로그램 전압보다 낮은 전압이어야 함) ⅴ) 만약 선택된 셀이 소거 상태의 셀일 경우, 전체 셀 스트링(String)을 통해 비트라인에 예비 충전된 전하가 방전되어 비트라인 전위가 내려감. ⅵ) 반대로 선택된 셀이 프로그램 상태의 셀이면 선택된 셀이 OFF 상태가 되어 비트라인에 예비 충전된 전하가 방전되는 데 많은 시간이 걸림. ⅶ) 센싱 시점에서 센싱 레벨 대비 비트라인 전위의 고저에 따라 ‘1’, ‘0’이 판정됨. |

(3) 낸드 플래시 메모리의 종류(SLC, MLC, TLC)

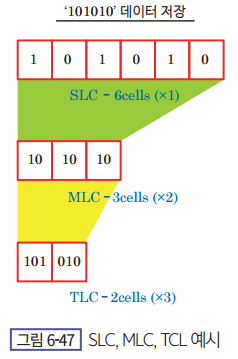

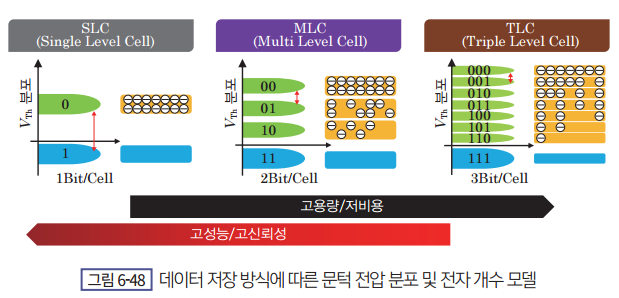

USB나 SSD와 같은 저장 장치에 사용되는 낸드 플래시 메모리는 그 성능 및 가격 측면에서 차이가 있다. 이러한 차이는 기억의 최소 단위인 비트(Bit)를 기준으로, 한 개의 셀에 몇 비트를 저장할 수 있느냐에 따라 몇 가지 종류로 분류할 수 있다. 한 개의 셀에 ‘0’ 또는 ‘1’의 2가지 상태로 구분하여 1비트 데이터를 저장하는 방식을 SLC(Single Level Cell)라 하고, 한 개의 셀에 ‘00’(소거), ‘01’, ‘10’, ‘11’(프로그램)의 4개 상태로 나누어 2비트 데이터를 저장하는 방식을 MLC(Multi Level Cell)라 한다. 또 한 개의 셀에 ‘000’ 부터 ‘111’까지 8개의 상태로 구분하여 3비트 데이터를 저장하는 방식을 TLC(Triple Level Cell)라고 하는데, 이들 모두 현재 상용화되어 있는 상태이다. 최근에는 1개의 셀에 4비트 데이터를 저장하여 총 16개의 상태를 구분할 수 있는 QLC(Quadruple Level Cell)도 속속 출시되고 있다. 예를 들어 [그림 6-47]과 같이 ‘101010’이라는 데이터를 SLC, MLC, TLC에 각각 저장하는 경우, SLC는 6개의 셀이 필요한 반면, MLC는 3개, TLC는 2개의 셀로도 데이터의 저장이 가능하다는 것이다. 다시 말해 물리적인 셀 수는 같지만 데이터 저장 방법에 따라 고용량화가 가능하다는 이야기이다. 그러면 이러한 MLC나 TLC는 어떻게 구현 가능한 것일까?

먼저 SLC는 [그림 6-48]과 같이 부유 게이트 셀 또는 전하 포획 셀의 전하 저장층(부유 게이트 또는 전하 포획 질화막) 내 전자의 존재 여부만을 확인하여 ‘1’과 ‘0’을 구분한다. 그리고 MLC와 TLC는 저장층 내의 전자 수를 정밀히 제어하여 하나의 셀에서 여러 가지의 문턱 전압(분포)을 보이도록 한 후, 각 문턱 전압(분포)별로 해당되는 데이터 값을 정해 여러 비트를 저장하는 방식이다.

(4) 전하 포획 낸드 플래시(Charge Trap Flash, CTF) 메모리

① 기본 구조

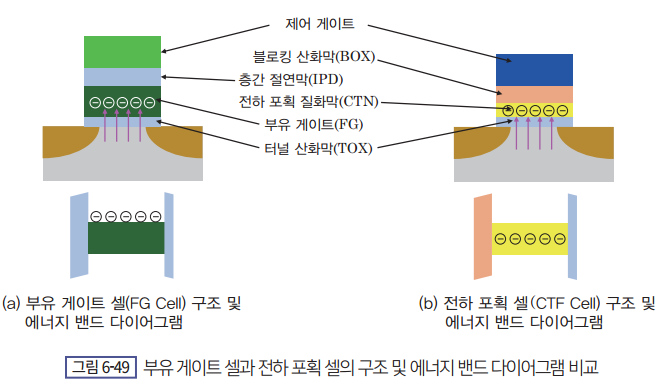

[그림 6-49]와 같이 부유 게이트 셀(FG Cell)과 전하 포획 셀(CTF Cell)은 구조적으로 전하가 저장되는 물질에 차이가 있다. 전도체인 n형으로 도핑된 다결정 실리콘(n-doped poly-silicon)을 사용하는 부유 게이트 셀과 달리, 전하 포획 셀은 실리콘 질화막(Si3N4)을 전하 포획 질화막(Charge Trap Nitride, CTN)으로 사용한다. 이 때문에 전하 포획 셀에서는 부유 게이트 셀에서 필요한 부유 게이트 패터닝 공정을 생략할 수 있어, 공정이 상대적으로 단순해진다는 장점이 있다. 또한 부유 게이트 셀에서는 제어 게이트(Control gate) 아래의 절연층을 층간 절연막(Inter Poly Dielectric, IPD)이라고 하지만, 전하 포획 셀에서는 블로킹 산화막(Blocking Oxide, BOX)이라고 부른다. 블로킹 산화막(BOX)은 ONO(산화막-질화막-산화막)로 구성된 층간 절연막(IPD)과 달리 고 유전율(High-k)의 물질을 사용하는데, 이 이유에 대해서는 뒤에서 설명하겠다. [그림 6-49]의 에너지 밴드 다이어그램과 같이 부유 게이트 셀은 전도체인 다결정 실리콘의 전도대역에 자유전자 형태로 전하가 저장되는 반면, 전하 포획 셀은 실리콘 질화막의 금지대역 내 포획 사이트(Trap site)에 포획 전자 형태로 전하가 저장된다는 특징이 있다.

지금부터는 부유 게이트 셀과의 구조적 차이에 의해 전하 포획 셀이 갖게 되는 장점에 대해 설명한다. 먼저 부유 게이트 셀에서는 게이트 결합 비율(Gate coupling ratio)을 확보하기 위해 부유 게이트의 다결정 실리콘을 두껍게 해야 하는 반면, 전하 포획 셀의 전하 포획 질화막(CTN)은 두께가 두꺼울 경우 오히려 프로그램이나 소거 동작 시에 오동작을 일으킬 수 있어 두께를 상대적으로 얇게 가져갈 수가 있다. 또, 부유 게이트 셀에서는 부유 게이트에 전도체 물질인 다결정 실리콘을 사용하므로 부유 게이트 간간섭 효과(Interference)가 발생하지만, 전하 보존층으로 절연체인 전하 포획 질화막(CTN)을 사용하는 전하 포획 셀은 이러한 간섭 효과가 없어 수평 방향 축소(Scale-down) 시에도 프로그램 셀의 문턱 전압 분포를 균일하게 가져갈 수 있다는 장점이 있다. 마지막으로, 전하 포획 셀은 자유전자 대신 쉽게 이동할 수 없는 포획 전자 형태로 전하가 저장되어 터널 산화막(TOX)을 통한 전자의 탈출이 어려우므로, 터널 산화막(TOX) 두께를 상대적으로 얇게 할 수 있다. 따라서 동일 프로그램 전압에서 더 많은 수의 전자를 저장할 수 있어 프로그램 문턱 전압을 높일 수가 있다. 역으로 해석해 보면 동일 전자 수 확보를 기준으로 했을 때 부유 게이트 셀 대비 프로그램 전압을 낮출 수 있게 되는 것이다. 그 밖에도 터널 산화막(TOX)의 두께 감소로 인해 산화막 내 포획되는 전자 수가 감소하여, 빈번히 반복되는 프로그램과 소거 과정에서 발생하는 터널 산화막(TOX) 열화에 의한 프로그램 및 소거 반복 내성(Endurance)도 개선된다.

② 동작 원리 및 특성

기본적인 동작은 부유 게이트 셀에서와 유사하다. 프로그램 동작은 제어 게이트에 고전압을 인가한 경우 p형 기판에 있는 전자가 FN 터널링을 통해 터널 산화막(TOX)을 거쳐 전하 포획 질화막(CTN)의 포획 사이트(Trap site)에 포획되는 방식이다. 이러한 포획 특성은 실리콘 질화막 내의 포획 사이트의 밀도 및 포획 에너지 수준 등과 같은 실리콘 질화막의 물성과 관련이 있다.

소거 동작 또한 기판에 양의 높은 전압을 인가하는 방식은 부유 게이트 셀과 유사하다. 하지만 전하 포획 셀에서는 상대적으로 부유 게이트 셀 대비 전자를 빼내기가 어려우므로, 반대로 p형 기판에서 전하 포획 질화막(CTN)으로의 정공 주입 과정이 필요하게 된다. 이러한 정공 주입은 2nm 이하의 얇은 터널 산화막(TOX)에서는 직접 터널링(Direct tunneling)에 의해 이루어지지만, 그 이상의 두께에서는 FN 터널링에 의해 정공 주입이 이뤄져야 한다.

(5) 3차원 낸드 플래시 메모리(3D NAND Flash Memory)

3차원 낸드 플래시 메모리는 2차원 구조의 부유 게이트 셀 및 전하 포획 셀의 미세화에 따른 각종 공정 및 소자상의 문제20를 해결하기 위해 등장하였다. 다시 한 번 그 주된 이유를 정리하면 ① 포토 공정의 한계, ② 부유 게이트 내 전자 수 감소, ③ 셀 간 간섭 현상 극복의 3가지로 대표할 수 있다.

RDF(Random Dopant Fluctuation), RTN(Random Telegraph Noise), CCI(Cell-to-Cell Interference) 등과 같은 소자상의 문제20

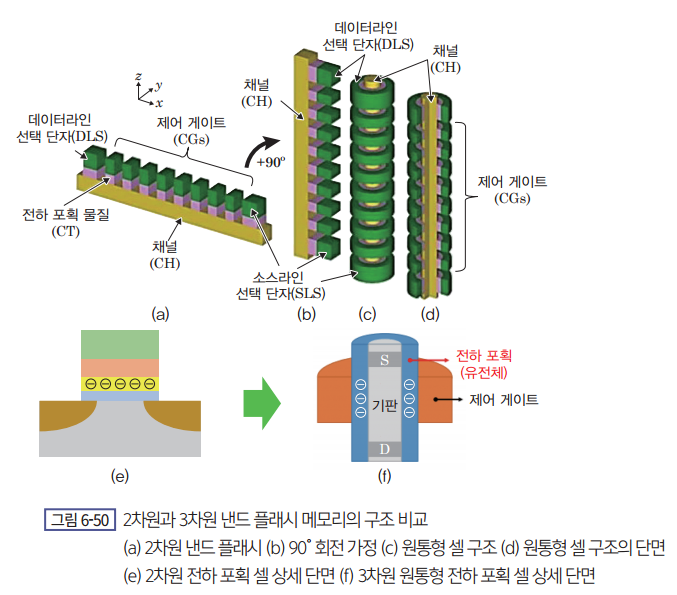

3차원 낸드 플래시 메모리는 [그림 6-50]과 같이 수직으로 서 있는 채널 주위로 층층의 제어 게이트(워드라인)가 감싸고 있는 3차원 원통형의 모습이다. 기판을 채널로 하는 2차원 셀 구조처럼 평면적 미세화에 따른 소자 집적도 증가가 아니라, 층 수를 증가시킴으로써 메모리 셀의 집적도를 향상시키는 기술이다. 따라서 층간 두께 조절이 곧, 2차원에서의 패턴 간 간격을 의미하므로 각 층의 박막 두께를 조절함으로써 공정적 측면에서의 포토 공정의 부담을 경감시킬 수 있다. 대신, 수직으로 다층의 박막을 쌓은 후 형성된 고 종횡비의 구조물을 깎고 다시 채워야 한다는 점에서, 고 난이도의 증착 공정과 식각 공정을 행해야 한다는 어려움은 있다. 또한 3차원 낸드 플래시는 부유 게이트가 아닌 전하 포획 셀을 적용21함으로써 얻을 수 있는 셀 간 간섭 현상 등 다양한 신뢰성 측면에서의 개선도 얻을 수 있다.

소수의 업체가 3차원에서도 부유 게이트 셀을 적용하고 있으나, 공정 비용 및 기술적 난이도 문제 때문에 대부분의 업체들은 전하 포획 셀 구조를 채택하고 있음.21

① 3차원 낸드 플래시 메모리 기술의 발전

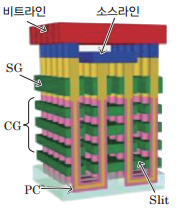

대표적인 3차원 낸드 플래시 메모리의 구조는 [표 6-2]와 같이 2009년 일본 도시바에서 개발한 P-BiCS와 한국 삼성전자가 개발한 TCAT(Terabit Cell Array Transistor)이다. 본 서에서는 TCAT 구조를 기본으로 설명한다.

표 6-2 P-BiCS와 TCAT 구조 비교

구분 | P-BiCS | TCAT |

구조 | ||

업체 | 일본 도시바(2009) | 한국 삼성전자(2009) |

형태 | U자 형(SONOS-CTF) | I자 형(MANOS-CTF) |

공정 | Gate First(게이트 퍼스트) | Gate Last(게이트 라스트) |

게이트 | GAA-Salicided Poly Silicon | GAA-Metal Gate(W or TaN) |

종횡비(A/R)22 | High | Very High |

기타 | 2007년 개발한 BiCS 구조를 개선 (Retention, Source selector 성능 등) | 2014년 이후 TCAT을 개선한 VNANDTM 출시 |

종횡비(Aspect Ratio, A/R)22: 홀(Hole) 구조에서 홀의 깊이와 폭의 비를 의미함. 종횡비가 클수록 공정 난이도는 증가함.

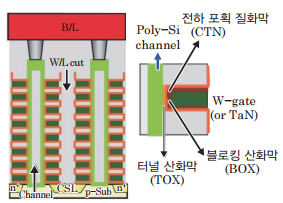

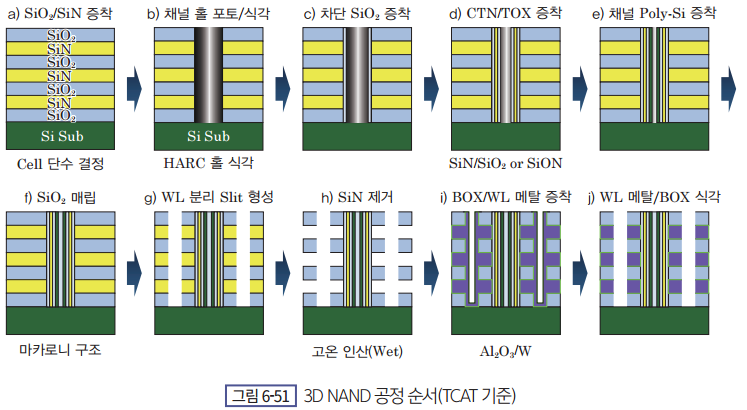

② 제조 공정

업체에 따라 차이가 있지만, 일반적인 전하 포획 셀(CTF Cell) 기반의 I자형 게이트(CG) 라스트 구조를 기준으로 3D NAND/V-NAND 플래시 셀 제작 공정을 설명하면 다음과 같다. a) 실리콘 기판에 산화막(SiO2)과 질화막(SiN)을 CVD 공정을 이용해 교대로 증착하고, b) 채널이 만들어질 구멍(Hole)을 포토 및 식각 공정을 통해 형성한다. 다음 c) SiN제거 시 차단 역할을 하는 산화막(SiO2)을 증착하고, d) CTN(SiN)과 TOX(SiO2)를 순차적으로 증착한 후 e) 수직 채널 형성을 위한 n+ 도핑된 다결정 실리콘을 증착한다. 이후 f) 산화막을 콘택 홀 내부 빈 공간에 매립하여 마카로니(Macaroni) 구조를 형성한다. g) 포토 및 식각 공정을 이용하여 워드라인(WL) 분리 영역에 슬릿(Slit)을 열고, h) 형성된 슬릿을 통해 고 선택비의 고온 인산(H3PO4) 용액으로 SiN을 제거한다. 그다음, i) BOX(High-k)와 CG(W)층을 연속 증착하고, j) 슬릿 영역 내 제어 게이트(CG)를 제거, 워드라인(WL)을 분리하여 산화막 분리층 사이에만 제어 게이트(CG)가 남게 하면서 공정이 마무리된다.

심화개념 |

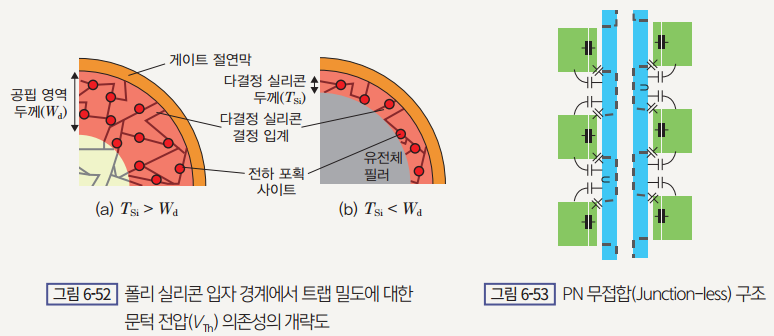

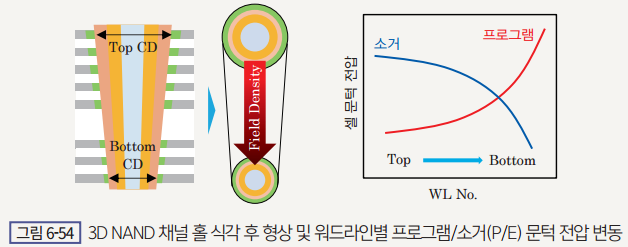

③ 3차원 낸드 플래시 셀 구조 및 주요 특성 ⅰ) Gate 구조(Gate All Around, GAA) 3차원 낸드 플래시의 게이트 구조는 제어 게이트가 채널을 완전히 감싸는 GAA(Gate All Around) 구조이다. 게이트가 채널을 완전히 지배하여 누설 전류를 감소시킨다는 장점은 있으나, 평면상의 단위 셀 내에 채널, 터널 산화막(TOX), 전하 포획 질화막(CTN), 블로킹 산화막(BOX) 및 워드라인이 모두 포함되어, 수평 방향의 축소(Scaling)가 어렵다는 문제도 있다. GAA 구조에서는 전속 밀도 차이로 인해 곡률 반경이 작을수록 전기장은 증가(D = εE)23하게 되는데, 이 차이로 인해 터널 산화막(TOX)에는 높은 전기장이, 블로킹 산화막(BOX)에는 상대적으로 낮은 전기장이 인가된다. 그 결과 프로그램 및 소거 효율을 향상시키고 동작 전압도 감소시켜 저전력 구현에도 유리하다. 이러한 원리 덕분에, GAA 구조의 도입은 전하 포획 셀에서의 전자 역 터널링에 의한 소거 포화 문제를 상당 수준 개선할 수 있게 하였다. 전하를 둘러싸는 임의의 폐곡면을 빠져나가는 전속(Flux)의 밀도(D)는 전기장(E)에 비례하며, 비례상수는 유전율(ε)인 가우스 법칙23 ⅱ) 채널 구조 3차원 낸드 플래시 셀의 채널은 단결정이 아닌 다결정 실리콘을 사용할 수밖에 없는데, 이는 높은 수율 확보와 고 종횡비의 콘택 홀 매립에 있어서 다른 선택의 여지가 없기 때문이다. 제조 공정 중에서 채널 콘택 홀을 다결정 실리콘으로 모두 매립하지 않고 중심부를 산화막으로 매립하는 마카로니(Macaroni) 구조를 적용하는 이유는 다결정 실리콘의 결정 입계(Grain boundary) 때문이다. 읽기(Read) 동작 시 [그림 6-52]와 같이 채널 공핍 영역(Wd)보다 다결정 실리콘의 두께(TSi)가 얇을 경우, 결정 입계에 포획되는 전하의 영향을 감소시킬 수 있어 문턱 전압 이하(Sub-threshold) 전류의 감소 및 스윙 특성 개선, 그리고 문턱 전압 변동 등을 개선시킬 수 있다. GAA 구조인 3D NAND는 채널 폭(Width)은 넓지만 다결정 실리콘 채널인 데다 [그림 6-53]과 같이 PN 무접합(Junction-less) 구조24를 가져 2차원 부유 게이트 셀 대비 동작 전류가 적다는 문제도 있다. 이러한 문제에 대한 해결책으로 큰 결정 입계 형성 및 단결정 실리콘과 유사한 박막 증착 기술이 핵심적으로 요구된다. PN 무접합 구조24: 실제 접합이 없으나 게이트 전압의 주변(Fringing) 효과로 인한 정전 결합으로 전자가 유기되어 가상의 접합이 일시적으로 생성되는 구조 ④ 3차원 낸드 플래시 메모리의 문제점과 대책 ▣ 공정상 문제 ⅰ) 고 종횡비 채널 홀 식각 3차원 낸드 플래시 제조 공정의 초반에 박막 증착 및 포토 공정을 진행하고, 이후 고 종횡비(High Aspect Ratio, HAR)의 채널 홀(Hole)을 식각하면, [그림 6-54]와 같은 모습이 된다. 반응성 이온 식각(Reactive Ion Etching, RIE)25의 특성상 아래로 내려갈수록 홀의 크기가 감소하게 되어 상, 하부 셀 간 특성 차이가 발생한다. 즉, 하단 터널 산화막(TOX)의 곡률 반경이 작아 더 큰 전계를 가지므로, 프로그램 문턱 전압이 증가하고, 소거 후에는 문턱 전압이 감소하는 현상이 일어나게 된다. 이 문제는 적층 수가 증가할수록 심각한 문제가 된다. 해결책으로는 각 워드라인에 인가하는 전압을 차별화하여 개선하는 알고리즘적 방법이 있다. 반응성 이온 식각25: 건식 식각 방법의 하나로, 이온과 활성종(Radical)에 의한 식각 방법

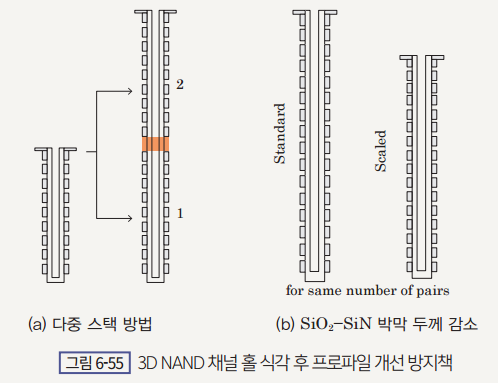

공정적 해결책으로는 두 가지를 들 수 있는데, 먼저 한 셀 스트링(String)을 일괄 제조하는 것이 아니라 [그림 6-55(a)]와 같이 두 개 이상의 스택(Stack)으로 나누어 제조하는 방법이다. 예를 들어 64개의 셀을 수직으로 적층하고자 할 때에는 먼저 32개의 셀 스트링을 제조한다. 그 후 32쌍의 박막에 채널 홀 식각과 전하 포획막 및 채널의 증착을 진행하여 1차 셀 스트링을 만든 다음, 그 위에 다시 32개의 셀에 대한 스택을 제조하는 2 스택 구성이다. 이와 같은 다중 계층 제조의 장점은 식각 및 증착 공정의 난이도가 감소한다는 것이다. 그러나 상하 계층 간의 정렬 정확도 문제 및 상부 계층 제조 시 하부 계층에 줄 수 있는 손상 문제를 예상할 수 있고, 제조 공정이 2단계로 이루어지므로 생산성의 감소를 초래한다.

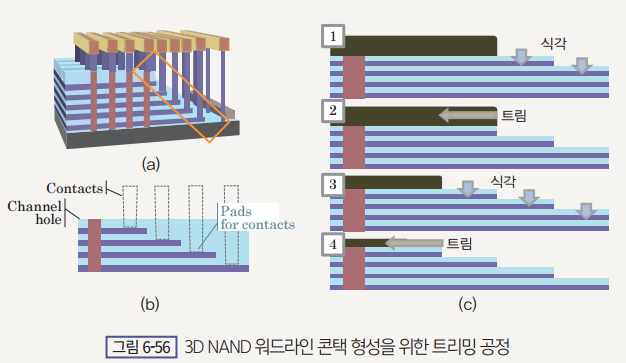

또 다른 공정적 해법은 제어 게이트 간 절연층인 SiO2 박막과 제어 게이트(워드라인)가 형성될 희생 SiN 박막의 두께를 줄여 동일 증착 층수로 전체 높이를 감소시키는 것이다. 이에 따라 식각 대상 종횡비도 완화되어 채널 홀의 프로파일을 개선할 수 있다. 그러나 이 방법은 제어 게이트(워드라인)의 두께 감소로 인해 전기 저항과 기생 정전용량이 증가한다는 문제가 있다. 또한, 인접한 셀 간의 전기적 간섭이 증가하고 얇은 절연막 간의 누설 전류 방지 등의 품질을 유지할 필요가 있다. ⅱ) 워드라인 계단(Staircase) 형성 기술 제어 게이트층은 결국 워드라인으로 이끌어 워드라인 디코더(Decoder)26와 연결되어야 한다. 이를 위해서는 각 층에서 개별적으로 워드라인을 이끌어 내야 하는데, 이때 필요한 것이 바로 [그림 6-56(a)]와 같은 계단식 구조이다. 예를 들어 32쌍 SiO2-SiN 막에서는 32개의 계단 모양 구조를 형성해야 한다. 제어 게이트층의 표면이 되는 계단 각 단의 표면을 노출시켜 이 표면에 수직으로 콘택 홀(Contact hole)을 형성하고, 상부의 금속배선층을 형성함으로써 워드라인과 연결한다. 워드라인 디코더26: 특정 워드라인을 선택할 수 있도록 하는 회로 장치

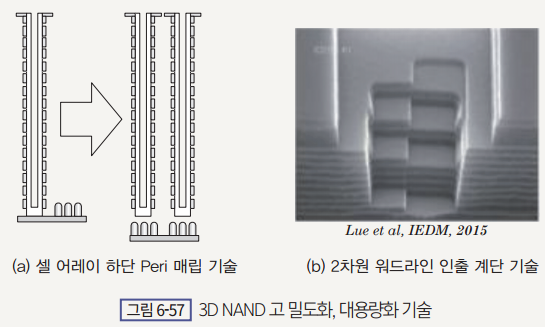

계단 패턴 형성 공정을 기존의 포토 및 식각 공정으로 한 단씩 형성하게 되면, 생산성이 매우 떨어진다. 이 때문에 고안된 기술이 ‘트림(Trim)’이라는 포토 공정 생략 기술이다. 먼저 포토 공정에 의해 포토레지스트 패턴을 형성하고, 식각 공정으로 SiO2-SiN 박막 1단만을 식각한다. 이후 포토레지스트를 제거하지 않고 포토레지스트의 측벽을 깎은(트리밍) 다음, 단 계단에 상당하는 부분의 표면을 노출시킨다. 다시 포토레지스트를 마스크로 하여, 다음 단의 SiO2-SiN 박막을 1단 식각하고, 같은 과정을 반복하면서, 계단 형상을 만드는 트림 과정이 이루어진다. 보통은 다중 챔버(Multi-chamber) 식각 장비를 사용하여 이러한 이종의 식각 공정을 1개의 장비 내에서 해결한다. 그러나 이 방법은 포토레지스트의 측벽을 식각하는 과정에서 상부도 일정량 식각되므로 층수가 올라감에 따라 추가 포토 공정을 필요로 한다. 그럼에도 불구하고, 개별적으로 포토 및 식각 공정을 하는 경우와 비교하면 생산성이 매우 높은 기술이다. ⅲ) 고 밀도화와 대용량화 3차원 낸드 플래시의 단면 구조를 보면 메모리 셀 어레이 이외의 부분에서 상당한 실리콘 면적이 존재한다. 실리콘 면적의 일부는 읽기 및 쓰기 동작의 제어와 데이터 외부 입출력 등을 담당하는 주변 회로가 차지하고, 나머지 면적은 셀의 제어 게이트를 워드라인으로 이끌어 내기 위한 계단 부분의 면적이다. 이러한 면적을 줄임으로써 저장 밀도를 향상시킬 수 있다. 주변 회로의 경우, 3차원 낸드 플래시 메모리 셀 어레이가 실리콘 기판을 거의 사용하지 않기 때문에, 셀 어레이의 바로 아래에 주변 회로의 많은 부분을 만들어 넣으면 주변 회로가 차지하는 면적을 크게 줄일 수 있다. 회사별로 이 기술을 부르는 명칭이 제각각이다. 삼성전자의 경우는 COP(Cell Over Periphery)라 하고, SK하이닉스는 PUC(Periphery Under Cell) 또는 4DNAND, 도시바는 CUA(Circuit-Under-Array), 마이크론은 CUA(CMOS Under the Array)라고 부른다. 다음은 계단 부분의 면적이다. 고 밀도화를 위해 적층 수를 증가시키면 계단이 차지하는 실리콘 면적이 증가한다. 그래서 국제 학회 등에서는 계단을 현재와 같은 선형이 아닌 나선 계단에 가까운 2차원 구조로 하여 계단 패턴의 실리콘 면적을 줄이는 기술이 제안되고 있다.

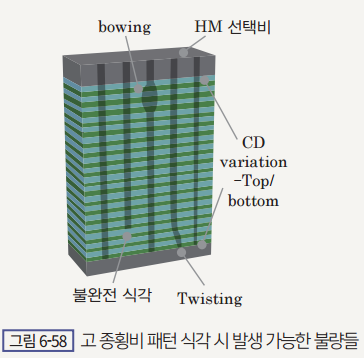

ⅳ) 고 종횡비 식각에서의 문제 고 종횡비 식각이 필요한 상황은 앞서 설명한 고 종횡비(HAR) 홀(Hole) 식각 외에 계단 구조의 제어 게이트와 주변 회로의 게이트에 ① 좁고 깊은 메탈 콘택 홀을 형성하는 공정과 메모리 셀의 ② 게이트 분리용 슬릿 형성 공정 등이 있다. 이러한 패턴 형성에 있어 문제시되는 것은 [그림 6-58]과 같은 다양한 패턴 불량이다. 대책으로는 고 선택비의 하드 마스크27 기술과 첨단의 이방성 식각 기술이 있다. 깊고 좁은 홀이나 슬릿 패턴의 식각이 진행됨에 따라 상부 입구 부근에서는 조금씩 홀 크기가 증가하게 되는데, 크기의 증가를 얼마나 줄일 수 있는지가 얼마나 층수를 높일 수 있는지를 좌우하게 된다. 이는 고 선택비의 하드 마스크 재료 및 공정 기술이 필요한 이유이기도 하다. 더욱 중요한 것은 한 장의 웨이퍼에 고 종횡비(20~40)의 홀이 1개가 아니라 1조 개가 넘는다는 것이다. 이러한 수많은 홀을 균일하게 형성한다는 것은 매우 어려운 기술이다. 더욱이 홀의 밀도가 높은 채널 홀 형성에 있어서는 한층 더 높은 균일성이 요구된다. 예를 들어, 채널 홀 모양이 조금이라도 왜곡되면 응력으로 인해 채널 홀 사이의 적층 박막이 쓰러지는 문제가 생긴다. 이러한 변형 없는 식각을 위해서는 고 이온 에너지, 높은 바이어스의 파워 식각 기술이 필요하며 균일도 높은 공정을 위해 대칭 챔버Symmetric chamber)의 설계와 공정 중 균일한 온도 제어가 필요하다. 패턴의 쓰러짐 또는 들뜸 불량 방지를 위해서는 박막 증착 시 균일도 개선과 더불어 응력을 최소화하고, 후속 식각 및 세정 시 가능하면 건식 세정(Dry cleaning) 공정을 선택할 필요가 있다. 하드 마스크27: 포토레지스트층 아래에 있으며, 식각 공정 시에 포토레지스트와 함께 실리콘 층을 보호하는 역할을 함

|

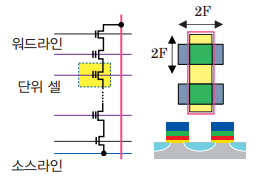

(6) 노아(NOR)와 낸드(NAND) 플래시 메모리

플래시 메모리의 대표적인 형태는 노아(NOR)형과 낸드(NAND)형으로, 그 명칭은 디지털 로직 회로 중 하나인 NOR와 NAND 게이트로부터 유래되었다. [표 6-3]과 같이 NOR형은 셀 간의 연결이 병렬로 되어 있어 데이터 읽기 시 임의 접근(Random access)이 가능하여 빠른 읽기 속도가 장점이나, 셀 단위로 프로그램해야 하므로 쓰기 속도가 느리다는 단점이 있다. 또, 각각의 전극선이 필요하여 셀 면적이 커지고 집적도가 낮아져 대용량 메모리로는 불리하다. 이에 반해 NAND형 플래시는 직렬로 되어 있어 임의 접근이 불가능하고, 각 셀에서 순차적으로 데이터를 읽어내는 방식이므로 NOR형 대비 읽기 속도가 느리지만, 메모리의 블록이 여러 페이지로 나누어져 있어 쓰기/소거 속도가 더 빠르다. 또 셀의 크기를 작게 가져가 고 집적화가 용이하다는 장점도 있다.

소거 동작의 원리는 NOR형, NAND형 모두 FN 터널링을 이용하지만, 프로그램에 있어서는 NAND형이 FN 터널링 원리를 적용하는 대신, NOR형은 셀별 임의 접근 방식 때문에 열 전자 주입(Hot electron injection) 원리를 적용한다. 여기서 열 전자 주입 원리란 게이트(~12V)와 드레인(~5V)에 전압을 인가한 고전계하에서, 전자가 소스에서 드레인으로 이동하면서 높은 에너지를 받아 열 전자(Hot electron)가 되고, 이로써 산화막의 에너지 장벽을 넘어 부유 게이트 내로 주입되게 하는 원리이다.

정리하면, NOR형은 집적도가 낮지만 개별 셀에 정보를 처리할 수 있고, NAND형은 개별 셀에 정보를 처리할 수 없지만 높은 집적도를 갖는 특징이 있다. 따라서 NOR형은 RAM처럼 실행 가능한 코드 저장 장치로 사용하기에 적합하고, NAND형은 다양한 이동식 저장 매체에 어울리는 방식이다.

표 6-3 NAND형과 NOR형 플래시 메모리 비교

구분 | NAND형 | NOR형 |

회로도, 평면도, 단면도 | ||

동작 원리 (프로그램/소거) | FN 터널링/FN 터널링 | 열 전자 주입/FN 터널링 |

장점 | 빠른 프로그램/소거 속도(~200μs/~2ms) Long P/E cycle(100k~1M) | 빠른 읽기 속도(~65ns) |

단점 | 느린 읽기 속도(~25μs) | 느린 프로그램/소거 속도(~4ms/~700ms) Short P/E cycle(10~100k) |

집적도/가격 | 높음/저가 | 낮음/고가 |

용도 | USB 메모리, SSD 등 저장 매체 | RAM처럼 실행 가능한 코드 저장 |

기출문제로 정리하기 ※기출문제를 읽고 스스로 답변해 본 후, 이와 관련된 ‘이론 페이지’의 내용을 확인하여 자신의 답안과 비교합니다. | 이론 페이지 |

최신 기출 1 DRAM, SRAM, 플래시 메모리의 차이점에 대해 설명하시오. | p.167~168 |

최신 기출 2 DRAM과 SRAM이 휘발성 메모리인 이유에 대해 설명하시오. | p.174, 189 |

최신 기출 2 DRAM과 SRAM이 휘발성 메모리인 이유에 대해 설명하시오. | p.174~176 |

최신 기출 4 CMOS 인버터의 동작 원리에 대해 설명하시오. | p.169 |

최신 기출 5 CMOS 인버터의 잡음 여유(Noise margin)에 대해 설명하시오. | p.169~171 |

최신 기출 6 DRAM의 기본 원리와 특성에 대해 설명하시오. | p.182~189 |

최신 기출 7 DRAM 누설 전류의 원인과 그 해결책에 대해 설명하시오. | p.189~191 |

최신 기출 8 DRAM의 미세화에 따라 소자에서 일어나는 문제점과 그 해결책에 대해 설명하시오. | p.196~198 |

최신 기출 9 DRAM의 리프레시 동작에 대해 설명하시오. | p.192~193 |

최신 기출 10 DRAM 셀 커패시터의 3차원 수직 구조의 문제점과 그 해결책에 대해 설명하시오. | p.199~201 |

최신 기출 11 낸드 플래시의 기본 원리와 특성에 대해 설명하시오. | p.204~206 |

최신 기출 12 SLC, MLC, TLC 낸드 플래시의 데이터 저장 방식에 대해 설명하시오. | p.213 |

최신 기출 13 전하 포획(Charge Trap Flash, CTF) 셀과 부유 게이트(Floating Gate, FG) 셀을 비교하여 설명하시오. | p.214 |

최신 기출 14 3D NAND 공정의 문제점과 원인 및 대책에 대해 설명하시오. | p.220~224 |

최신 기출 15 낸드(NAND)와 노아(NOR) 플래시 메모리의 차이에 대해 설명하시오. | p.225 |

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기