Pinch-off 현상이란 무엇입니까?

[핀치 오프(pinch-off)]

전계효과 트랜지스터(접합형)에 있어서, 역바이어스 전압을 점차 증가시켜 나가면 두 전극으로부터 채널에 공핍층이 생겨서 결국 채널이 폐쇄되고 드레인 전류가 컷 오프되는 현상. 핀치 오프에 의해서 전류가 흐리지 않게 되는 전극 간 전압을 핀치 오프 전압이라 한다.

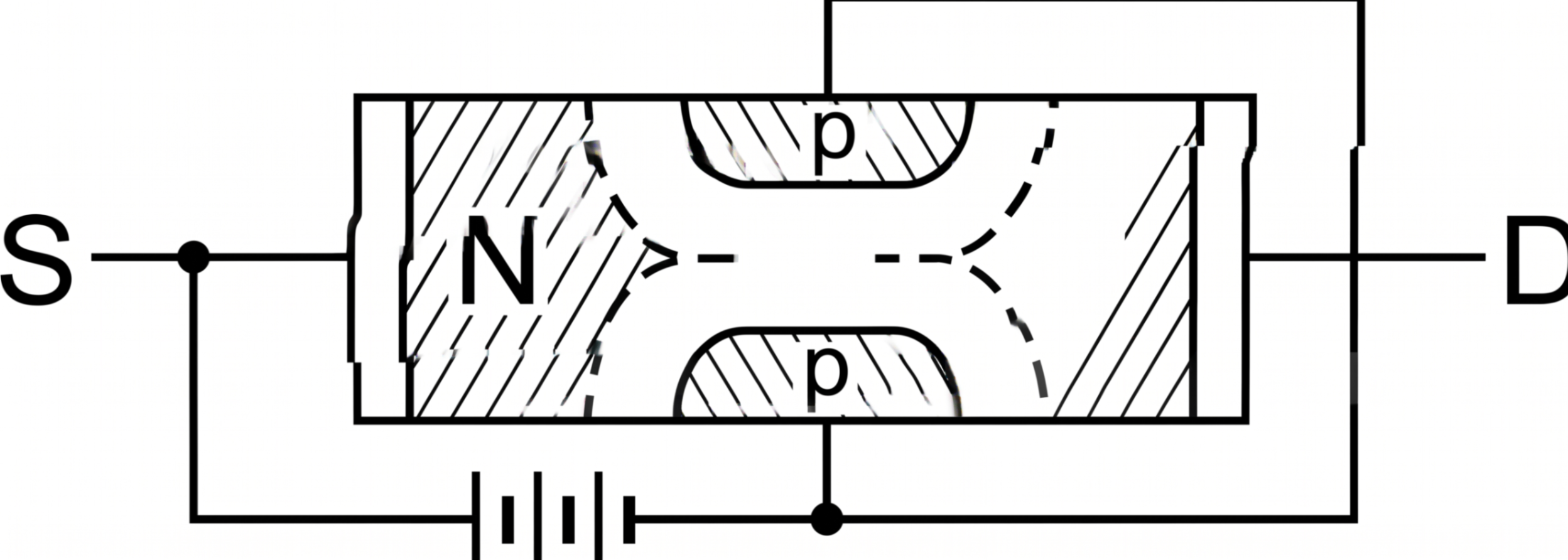

n 채널의 전계 효과 트랜지스터(접합형)를 생각해 보자. 이 디바이스의 게이트는 고농도의 p형 반도체가 확산되어 있으며, p+-n 접합부에는 공핍층이 생기지만 게이트가 고농도로 확산되어 있기 때문에 공핍층은 주로 n 채널 측으로 튀어 나와 있다.

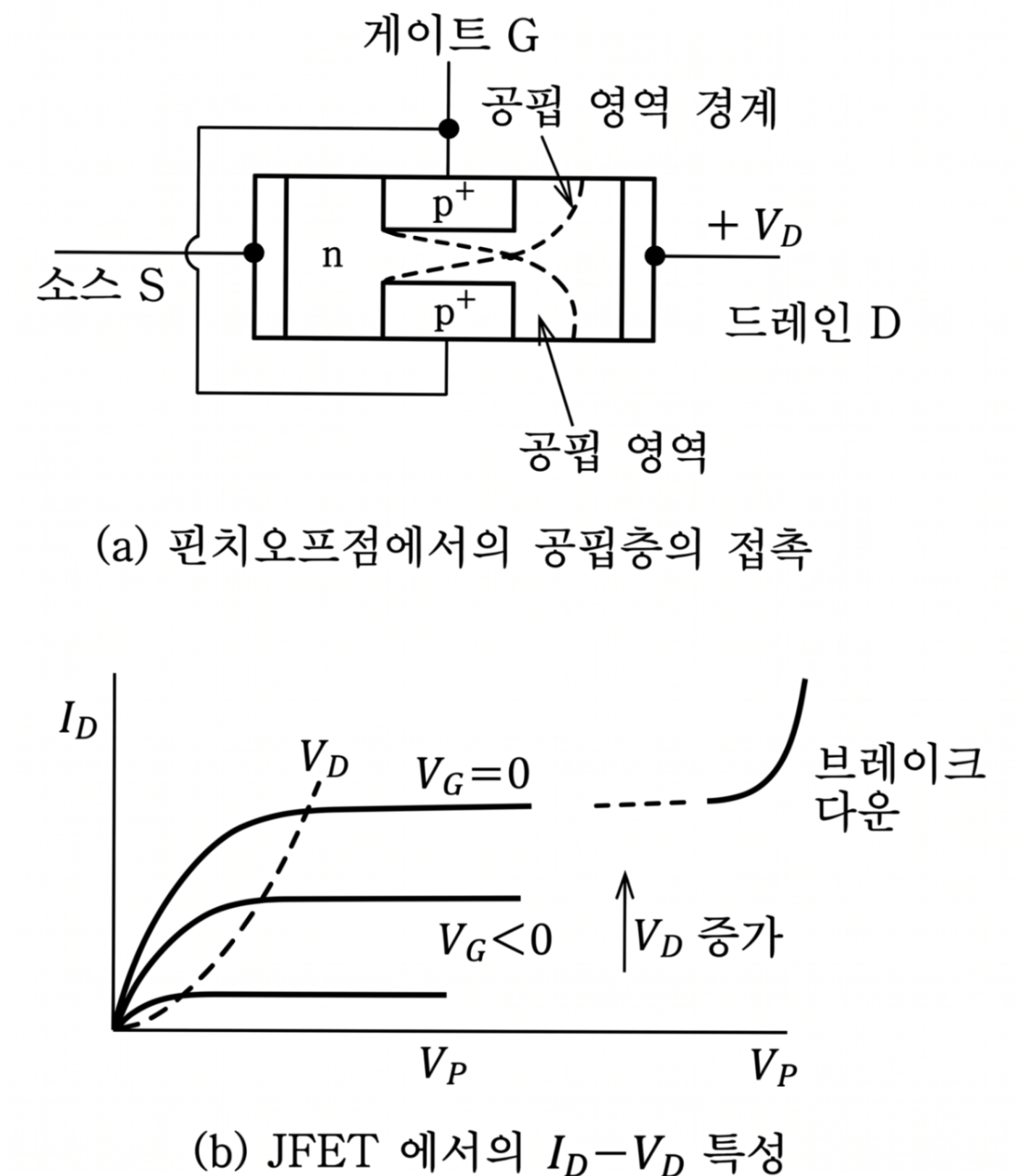

공핍층의 두께는 게이트 전압 VG에 의해 변화하고, 따라서 n 채널의 평균 단면적, 즉 소스 · 드레인 간 저항은 게이트 전압에 의해서 제어된다. 그림에 JFET(소스 공통형)의 특성 곡선을 나타냈다. 그림과 같이 채널이 튀어 나온 공핍층에 의해 핀치오프(폐색)되는 점의 드레인 전압 VD를 핀치오프 전압 VP라 한다.

드레인 전압은 더 증대해 가도 드레인 공핍 영역은 확산되지만, 채널 형상은 그다지 변화하지 않고, 드레인 전류도 그림과 같이 거의 일정 값으로 추이한다. 절연 게이트형 FET의 경우에도 마찬가지로 핀치오프는 생각된다.

커뮤니티 Q&A

위 이론과 관련된 게시글이에요.

이해가 안 되거나 궁금한 점이 있다면 커뮤니티에 질문해 보세요!

게시글 작성하기